إذا نظرنا إلى توسع صناعة أشباه الموصلات خلال السنوات الخمس والعشرين الماضية، يبدو أن اعتماد IP للتصميم في كل تطبيق هو أحد عوامل النجاح الرئيسية، مع التطور المذهل لتكنولوجيا السيليكون بعامل x25، من 100 نانومتر في عام 250 إلى 2018 نانومتر (إذا وليس 3 نانومتر) في عام 2. نتوقع أن يلعب الانتقال إلى البنية القائمة على الشرائح الصغيرة قريبًا نفس الدور الذي لعبته البنية القائمة على شريحة SoC والاستخدام المكثف لملكية الفكرية الخاصة بالتصميم في العقد الأول من القرن الحادي والعشرين.

والسؤال هو كيفية التنبؤ بدقة بالإطار الزمني لاعتماد الشرائح الصغيرة وما هي عوامل التمكين الرئيسية لهذه الثورة. سنرى ما إذا كان نشر نظرية الابتكار يمكن أن يكون مفيدًا لضبط التنبؤ وتحديد نوع التطبيق الذي سيكون المحرك. يبدو أن المواصفات القياسية لبروتوكول الاتصال البيني من شريحة إلى شريحة، التي تسمح بتبني الصناعة بسرعة، وقيادة التطبيقات مثل IA أو معالج تطبيقات الهاتف الذكي، هي أهم عوامل التمكين، ولكن كفاءة أدوات EDA أو تعبئة التقنيات الجديدة وإنشاء القوات المسلحة البوروندية المخصصة، من بين أمور أخرى، هي بالتأكيد المفتاح.

المقدمة: ظهور تكنولوجيا الشرائح

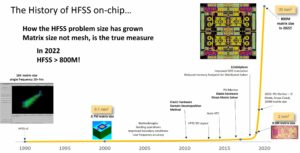

خلال العقد 2010، بدأت فوائد قانون مور في الانهيار. نص قانون مور على أن كثافة الترانزستور تتضاعف كل عامين، وستنخفض تكلفة الحوسبة بنسبة 50%. يرجع التغيير في قانون مور إلى زيادة تعقيد التصميم في تطور بنية الترانزستور من الأجهزة المستوية إلى الأجهزة Finfets. تحتاج Finfets إلى أنماط متعددة للطباعة الحجرية لتحقيق أبعاد الأجهزة إلى أقل من 20 نانومتر.

في نهاية هذا العقد، تزايدت احتياجات الحوسبة بشكل كبير، ويرجع ذلك في الغالب إلى انتشار مراكز البيانات وبسبب كمية البيانات التي يتم إنشاؤها ومعالجتها. في الواقع، يتم الآن استخدام الذكاء الاصطناعي (AI) وتقنيات مثل التعلم الآلي (ML) لمعالجة البيانات المتزايدة باستمرار، مما أدى إلى زيادة الخوادم بشكل كبير في قدرتها الحاسوبية. أضافت الخوادم العديد من نوى وحدة المعالجة المركزية، ودمجت وحدات معالجة رسومات أكبر تستخدم حصريًا لتعلم الآلة، ولم تعد تستخدم للرسومات، وقد قامت بتضمين مسرعات ASIC AI مخصصة أو معالجة ذكاء اصطناعي تكميلية تعتمد على FPGA. تم تنفيذ تصميمات شرائح الذكاء الاصطناعي المبكرة باستخدام شرائح SoC متجانسة أكبر حجمًا، ووصل بعضها إلى الحد الأقصى للحجم الذي تفرضه الشبكة، وهو حوالي 700 ملم2.

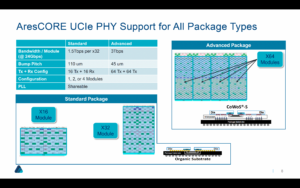

في هذه المرحلة، يبدو أن الحل الصحيح هو التقسيم إلى شريحة SoC أصغر بالإضافة إلى شرائح الحوسبة وشرائح الإدخال/الإخراج المتنوعة. قام العديد من صانعي الرقائق، مثل Intel أو AMD أو Xilinx، بتحديد هذا الخيار للمنتجات التي تدخل مرحلة الإنتاج. في التقرير التمهيدي الممتاز الصادر عن مجموعة Linley Group، بعنوان "تكتسب الشرائح الصغيرة التبني السريع: لماذا أصبحت الرقائق الكبيرة أصغر حجمًا"، تبين أن هذا الخيار يؤدي إلى تكاليف أفضل مقارنةً بالشرائح SoC المتجانسة، نظرًا لتأثير العائد الأكبر. لقد صمم صانعو الرقائق هذه شريحة صغيرة متجانسة، ولكن ظهور واعتماد معيار التوصيل البيني مثل Universal Chiplet Interconnect Express (UCIe) IP يعمل على تسهيل اعتماد الشريحة الصغيرة غير المتجانسة.

إن تطور معايير البروتوكول الأحدث والأسرع يتسارع مع استمرار الصناعة في المطالبة بأداء أعلى. ولسوء الحظ، لا تتم مزامنة المعايير المختلفة من قبل منظمة واحدة. يمكن أن تأتي معايير PCIe الجديدة قبل أو بعد عام واحد (أو أكثر) من معيار بروتوكول Ethernet الجديد. يتيح استخدام التكامل غير المتجانس لمقدمي خدمات السيليكون التكيف مع السوق سريع التغير من خلال تغيير تصميم الشريحة ذات الصلة فقط. وبالنظر إلى أن تصنيع تصميم SoC المتقدم يتطلب نفقات رأسمالية هائلة لعقد معالجة 5 نانومتر أو 4 نانومتر أو 3 نانومتر، فإن تأثير بنيات الشرائح يعد هائلاً لدفع الابتكار المستقبلي في مجال أشباه الموصلات.

يتيح لنا تصميم الشرائح غير المتجانسة استهداف تطبيقات أو قطاعات سوقية مختلفة عن طريق تعديل أو إضافة الشرائح الصغيرة ذات الصلة فقط مع الحفاظ على بقية النظام دون تغيير. ويمكن إطلاق التطورات الجديدة بشكل أسرع في السوق، باستثمارات أقل بكثير، حيث أن إعادة التصميم لن تؤثر إلا على ركيزة الحزمة المستخدمة لإيواء الشرائح الصغيرة. على سبيل المثال، يمكن إعادة تصميم شريحة الحوسبة من TSMC 5nm إلى TSMC 3nm لدمج ذاكرة تخزين مؤقت L1 أكبر أو وحدة معالجة مركزية ذات أداء أعلى أو عدد من مراكز وحدة المعالجة المركزية، مع الحفاظ على بقية النظام دون تغيير. يمكن إعادة تصميم Chiplet التي تدمج SerDes للحصول على معدلات أسرع على عقد العمليات الجديدة التي توفر المزيد من النطاق الترددي للإدخال/الإخراج لتحسين وضع السوق.

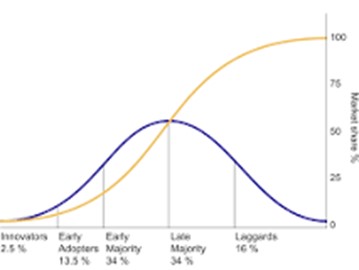

سيؤدي استخدام الشرائح غير المتجانسة إلى توفير وقت وصول أفضل إلى السوق (TTM) عند تحديث النظام، وإعادة استخدام جزء النظام دون أي تغيير إذا كان مصممًا على شرائح صغيرة. وستكون هذه أيضًا طريقة لتقليل التكلفة عند الاحتفاظ ببعض الشرائح الوظيفية على العقد الأقل تقدمًا، وهي أرخص من الأكثر تقدمًا. لكن السؤال الرئيسي هو التنبؤ متى ستنشئ تكنولوجيا الشرائح شريحة كبيرة من سوق أشباه الموصلات؟ سنراجع تاريخ اعتماد بروتوكول الإنترنت (IP) نظرًا لأن الشريحة الصغيرة وبروتوكول الإنترنت (IP) متشابهان، ويجب على كلاهما كسر متلازمة NIH ليصبحا ناجحين. سوف نستخرج الأسباب الرئيسية لاعتماد الشرائح الصغيرة ونبني توقعات، باستخدام نظرية الابتكار والفئة المحددة (المبتكرون، المتبنون الأوائل، وما إلى ذلك. انظر الشكل أدناه).

سنراجع اعتماد ARM CPU IP خلال الفترة من 1991 إلى 2018 وتاريخ اعتماد IP خلال الفترة من 1995 إلى 2027، ونتحقق من مدى التزام معدل الاعتماد هذا بنظرية الابتكار.

سنشرح سبب تعزيز اعتماد الشرائح الصغيرة، ونراجع الأسباب المتعلقة بالتكنولوجيا والتسويق:

- من شركة نفط الجنوب القائمة على IP إلى النظام القائم على شرائح صغيرة

- إمكانية التشغيل البيني، وذلك بفضل معيار البروتوكول المفضل لربط شرائح البيانات

- شرح سبب كون Interface IP المتطور هو المفتاح لاعتماد Chiplet

- التحديات المتعلقة بالتصميم لحلها.

- وأخيرًا وليس آخرًا، الاستثمار الذي قام به المسبك

وأخيرًا، يمكننا بناء توقعات مبدئية لاعتماد الشرائح الصغيرة، استنادًا إلى نظرية الابتكار. فقط نذكر أن الصناعة انتقلت للتو إلى مرحلة "المتبنون الأوائل"، حيث شهدت العديد من بائعي IP والشرائح الصغيرة الذين يخدمون الحوسبة عالية الأداء (HPC) والذكاء الاصطناعي (AI).

إذا قمت بتنزيل ورقة بيضاء، سوف تستمتع بكل النص والصور العديدة، والتي تم إنشاء بعضها حصريًا لهذا العمل.

By إريك إستيف (دكتوراه) محلل ، مالك IPnest

قامت شركة Alphawave برعاية إنشاء هذه الورقة البيضاء، لكن الآراء والتحليلات تخص المؤلف. يمكن العثور على المقالة هنا:

https://awavesemi.com/resource/will-chiplet-adoption-to-mimic-ip-adoption/

اقرأ أيضا:

واجهة IP في عام 2022: نمو بنسبة 22% على أساس سنوي لا يزال يعتمد على البيانات

شارك هذا المنشور عبر:

- محتوى مدعوم من تحسين محركات البحث وتوزيع العلاقات العامة. تضخيم اليوم.

- PlatoData.Network Vertical Generative Ai. تمكين نفسك. الوصول هنا.

- أفلاطونايستريم. ذكاء Web3. تضخيم المعرفة. الوصول هنا.

- أفلاطون كربون، كلينتك ، الطاقة، بيئة، شمسي، إدارة المخلفات. الوصول هنا.

- أفلاطون هيلث. التكنولوجيا الحيوية وذكاء التجارب السريرية. الوصول هنا.

- المصدر https://semiwiki.com/chiplet/339927-will-chiplet-adoption-mimic-ip-adoption/

- :لديها

- :يكون

- :ليس

- $ UP

- 1

- 1995

- 200

- 2018

- 2022

- 2023

- 25

- a

- من نحن

- المعجلات

- التأهيل

- تكيف

- وأضاف

- مضيفا

- متبنين

- تبني

- متقدم

- AI

- بيانات الذكاء الاصطناعي

- الكل

- السماح

- يسمح

- أيضا

- AMD

- من بين

- كمية

- تحليل

- المحلل

- و

- بعيدا

- يبدو

- تطبيق

- التطبيقات

- هندسة معمارية

- هي

- ARM

- البند

- مصطنع

- الذكاء الاصطناعي

- الذكاء الاصطناعي (منظمة العفو الدولية)

- AS

- ASIC

- يسأل

- At

- المؤلفة

- عرض النطاق الترددي

- على أساس

- BE

- أصبح

- بدأ

- يجري

- أقل من

- الفوائد

- أفضل

- كبير

- عززت

- على حد سواء

- استراحة

- نساعدك في بناء

- لكن

- by

- مخبأ

- CAN

- الطاقة الإنتاجية

- الموارد

- الفئة

- الأسباب

- بالتأكيد

- التحديات

- تغيير

- متغير

- أرخص

- التحقق

- رقاقة

- شيبس

- تأتي

- مقارنة

- مكمل

- تعقيد

- إحصاء

- الحوسبة

- النظر

- المقابلة

- التكلفة

- التكاليف

- استطاع

- وحدة المعالجة المركزية:

- خلق

- خلق

- خلق

- على

- البيانات

- عقد

- مخصصة

- تعريف

- كثافة

- تصميم

- تصميم

- تصاميم

- حدد

- التطوير التجاري

- التطورات

- الأجهزة

- مختلف

- التوزيع

- الأبعاد

- مضاعف

- بإمكانك تحميله

- قيادة

- سائق

- قيادة

- اثنان

- أثناء

- في وقت سابق

- في وقت مبكر

- الأوائل

- تخفيف

- النظام الإيكولوجي

- كفاءة

- جزءا لا يتجزأ من

- ظهور

- تمكين

- تمكين

- النهاية

- استمتع

- إلخ

- يتزايد باستمرار

- كل

- تطور

- مثال

- ممتاز

- على وجه الحصر

- توسع

- شرح

- التعبير

- استخراج

- حقيقة

- عامل

- العوامل

- فال

- FAST

- أسرع

- الشكل

- في حالة

- توقعات

- توقع

- وجدت

- FPGA

- تبدأ من

- وظيفي

- مستقبل

- ربح

- ولدت

- الحصول على

- الذهاب

- وحدات معالجة الرسومات

- الرسومات

- تجمع

- التسويق

- يملك

- مفيد

- هنا

- الراقية

- أعلى

- تاريخ

- منـزل

- كيفية

- كيفية

- HPC

- HTTPS

- ia

- if

- التأثير

- نفذت

- مفروض

- in

- زيادة

- في ازدياد

- لا يصدق

- العالمية

- الابتكار

- المبتكرين

- دمج

- المتكاملة

- دمج

- التكامل

- إنتل

- رؤيتنا

- السطح البيني

- إلى

- استثمار

- IP

- IT

- JPG

- م

- حفظ

- القفل

- أكبر

- اسم العائلة

- الى وقت لاحق

- أطلقت

- القانون

- يؤدي

- تعلم

- الأقل

- ليد

- أقل

- مثل

- مما سيحدث

- لينكدين:

- يعد

- بحث

- خفض

- آلة

- آلة التعلم

- صنع

- الرئيسية

- رائد

- صناع

- كثير

- تجارة

- التسويق

- هائل

- ذكر

- تقليل

- ML

- متكشف عن وحدة متراصة

- الأكثر من ذلك

- أكثر

- خاصة

- خطوة

- انتقل

- متعدد

- حاجة

- إحتياجات

- جديد

- التكنولوجيات الجديدة

- أحدث

- المعاهد الوطنية للصحة

- لا

- العقد

- الآن

- عدد

- كثير

- of

- عرض

- الوهب

- on

- ONE

- فقط

- آراء

- خيار

- or

- منظمة

- أخرى

- كاتوا ديلز

- صفقة

- التعبئة والتغليف

- ورق

- جزء

- أداء

- أداء

- مرحلة جديدة

- رسالة دكتوراه

- PHP

- اختيار

- لوحات حائط

- أفلاطون

- الذكاء افلاطون البيانات

- أفلاطون داتا

- بلايستشن

- لعبت

- المزيد

- البوينت

- وضع

- منشور

- توفير الطاقة

- على وجه التحديد

- تنبأ

- تنبؤ

- المفضل

- عملية المعالجة

- معالجة

- معالجة

- المعالج

- الإنتــاج

- المنتجات

- بروتوكول

- مقدمي

- سؤال

- أسرع

- بسرعة

- سريع

- معدل

- الأجور

- الوصول إلى

- عرض

- الأسباب

- إعادة تصميم

- إعادة تصميم

- ذات صلة

- ذات الصلة

- تذكير

- يتطلب

- REST

- مراجعة

- مراجعة

- ثورة

- حق

- النوع

- نفسه

- انظر تعريف

- رؤية

- يبدو

- قطعة

- شرائح

- حدد

- أشباه الموصلات

- الخوادم

- خدمة

- عدة

- أظهرت

- هام

- بشكل ملحوظ

- السيليكون

- مماثل

- عزباء

- المقاس

- الأصغر

- الهاتف الذكي

- حل

- حل

- بعض

- قريبا

- الفضاء

- مواصفات

- سرعة

- المدعومة

- معيار

- المعايير

- ذكر

- لحام عصا

- لا يزال

- بناء

- تحقيق النجاح

- ناجح

- نظام

- أنظمة

- الهدف

- تقنيات

- التكنولوجيا

- تكنولوجيا

- نص

- من

- شكر

- أن

- •

- من مشاركة

- منهم

- نظرية

- تشبه

- هؤلاء

- عبر

- إطار زمني

- إلى

- أدوات

- تيشرت

- هائل

- TSMC

- اثنان

- نوع

- لسوء الحظ

- عالمي

- تحديث

- us

- تستخدم

- مستعمل

- استخدام

- مختلف

- الباعة

- بواسطة

- وكان

- طريق..

- we

- كان

- ابحث عن

- متى

- في حين

- أبيض

- ورقة بيضاء

- لماذا

- سوف

- مع

- للعمل

- سوف

- عام

- سنوات

- التوزيعات للسهم الواحد

- لصحتك!

- زفيرنت