منذ ظهورها لأول مرة في الثمانينيات مع شبكات LAN مشتركة بسرعة 1980 ميجا بت في الثانية عبر الكابلات المحورية، شهدت شبكة Ethernet تطورات متسقة، والآن مع إمكانية دعم سرعات تصل إلى 10 تيرابت في الثانية. وقد أتاح هذا التقدم لشبكة Ethernet خدمة نطاق أوسع من التطبيقات، مثل البث المباشر وشبكات الوصول إلى الراديو والتحكم الصناعي، مع التركيز على أهمية نقل الحزم الموثوق به وجودة الخدمة. مع عرض النطاق الترددي الحالي للإنترنت الذي يبلغ حوالي 1.6 تيرابت في الثانية، هناك طلب متزايد على تحسين التعامل مع حركة المرور داخل مراكز البيانات الخلفية. على الرغم من أن الخوادم الفردية لا تعمل بعد على مستويات تيرابت في الثانية، إلا أن إجمالي حركة مركز البيانات يقترب من هذا النطاق، مما دفع مجموعة 500dj الخاصة بـ IEEE إلى بذل جهود توحيد وتتطلب وحدات تحكم Ethernet قوية وSerDes لإدارة تدفق البيانات المتوسع. وسط هذه الخلفية من الطلبات المتصاعدة، فإن الاتصالات بين المعالجات تسير بالفعل نحو هذه السرعات.

يقود الاتصال بين المعالجات الحاجة إلى معدلات 1.6T مع الحد الأدنى من الكمون. في حين أن الأجهزة الفردية مقيدة بقدرات المعالجة المتأصلة وحجم الرقاقة، فإن دمج الرقائق يمكن أن يزيد من هذه القدرات بشكل كبير. ومن المتوقع أن يتبع الجيل الأول من التطبيقات اتصالات تحويل إلى محول داخل مركز البيانات، مما يتيح تجميع المعالجات والذاكرة عالية الأداء، مما يعزز قابلية التوسع والكفاءة داخل الحوسبة السحابية.

مبادرة IEEE 802.3dj: تطوير معايير Ethernet لقابلية التشغيل البيني بسرعة 1.6 تيرابت في الثانية

يعد الامتثال لجهود التقييس المتطورة أمرًا محوريًا لقابلية التشغيل البيني السلس للنظام البيئي. تعمل مجموعة 802.3dj التابعة لـ IEEE على صياغة معيار Ethernet القادم، والذي يشمل الطبقات المادية ومعلمات الإدارة للسرعات من 200G إلى 1.6 تيرابت في الثانية. هدف المجموعة هو معدل بيانات MAC لشبكة إيثرنت يبلغ 1.6 تيرابت في الثانية، بهدف تحقيق حد أقصى لمعدل خطأ البت لا يزيد عن 10-13 في طبقة MAC. تتضمن الأحكام الإضافية واجهات وحدة المرفقات (AUI) الاختيارية ذات 16 و8 حارات المناسبة لتطبيقات الرقائق المختلفة، مع الاستفادة من 112G و224G SerDes. ماديًا، تتطلب مواصفات 1.6 تيرابت في الثانية النقل عبر 8 أزواج من كابلات Twinax النحاسية لمسافة تصل إلى متر واحد و8 أزواج من الألياف لمسافات تتراوح بين 500 متر و2 كيلومتر. على الرغم من أنه من المتوقع أن يتم التصديق الكامل على المعيار بحلول ربيع عام 2026، فمن المتوقع الانتهاء من المجموعة الأساسية من الميزات في عام 2024.

عرض النطاق الترددي الزائد وتصحيح الأخطاء في أنظمة إيثرنت 1.6T الفرعية

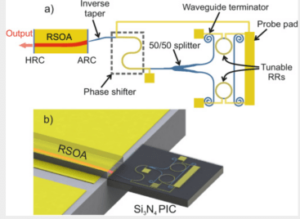

الشكل 1: رسم تخطيطي يصور مكونات نظام إيثرنت فرعي 1.6T.

في تكرارات Ethernet السابقة، ركزت أجهزة الكمبيوتر بشكل أساسي على تشفير البيانات لاكتشاف الحزم بشكل موثوق. ومع ذلك، مع التصعيد إلى سرعات إيثرنت 1.6T، أصبحت الحاجة إلى تصحيح الأخطاء الأمامية (FEC) واضحة، خاصة لمواجهة تدهور الإشارة حتى عبر الروابط القصيرة. ولهذا الغرض، تستمر شبكة 1.6T Ethernet في استخدام Reed-Solomon FEC. يبني هذا الأسلوب كلمة مشفرة تشتمل على 514 رمزًا مكونة من 10 بتات مشفرة في كتلة مكونة من 544 رمزًا، مما يؤدي إلى زيادة عرض النطاق الترددي بنسبة 6%. يتم توزيع كلمات كود FEC عبر الروابط المادية لـ AUI بحيث لا يحمل كل رابط فعلي (8 لـ 1.6T Ethernet) كلمة كود كاملة. لا توفر هذه الطريقة حماية إضافية ضد رشقات الأخطاء فحسب، بل تتيح أيضًا التوازي في وحدة فك التشفير البعيدة، وبالتالي تقليل زمن الوصول.

يقوم المرفق المادي المتوسط (PMA)، الذي يتميز بعلبة تروس وSerDes، بإحضار إشارة Ethernet إلى القنوات المرسلة. بالنسبة لشبكة إيثرنت 1.6T، يتضمن ذلك 8 قنوات تعمل كل منها بسرعة 212 جيجابت في الثانية، وهو ما يمثل 6% من حمل FEC. تقنية التعديل المستخدمة هي تعديل سعة النبض ذو 4 مستويات (PAM-4)، والذي يقوم بتشفير بتتي بيانات لكل رمز إرسال، وبالتالي مضاعفة عرض النطاق الترددي بشكل فعال عند مقارنته بالنهج التقليدي لصفر عدم العودة (NRZ). تعتمد آلية النقل على التحويل من رقمي إلى تناظري، بينما على الطرف المتلقي، يضمن التحويل من تناظري إلى رقمي مقترنًا بمزودي خدمات الإشارة (DSP) استخلاصًا دقيقًا للإشارة.

علاوة على ذلك، من المهم ملاحظة أن أجهزة Ethernet PCS تقدم "FEC خارجيًا" يمتد من طرف إلى طرف على رابط Ethernet. لتعزيز القنوات ذات الوصول الأطول، هناك طبقة إضافية من تصحيح الأخطاء للخطوط المادية الفردية قيد التنفيذ، ومن المحتمل أن تعتمد رمز هام FEC. من المتوقع أن يجد هذا التصحيح تطبيقه الأساسي في وحدات الإرسال والاستقبال الضوئية حيث يكون هذا التصحيح أمرًا ضروريًا.

الشكل 2: رسم تخطيطي يعرض الحمل الإضافي الذي تمت إضافته عند استخدام FEC متسلسل للوصول الموسع.

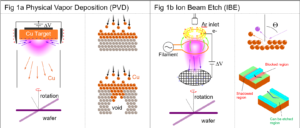

في نموذج النظام الموضح في الشكل 2، يتم توصيل MAC وPCS عبر وحدة بصرية وامتداد ألياف. لدى أجهزة الكمبيوتر معدل خطأ بت يبلغ 10-5 عند رابط الوحدة الضوئية، بالإضافة إلى الأخطاء الواردة من الرابط البصري نفسه. لن يكفي استخدام RS-FEC من طرف إلى طرف لتحقيق الرقم 10-13 معيار إيثرنت، مما يجعل الارتباط غير موثوق به. يتمثل أحد الخيارات في التنفيذ الثلاثي لـ RS FEC المنفصل في كل قفزة، مما يؤدي إلى زيادة التكاليف وزمن الوصول بشكل كبير. الحل الأكثر فعالية هو دمج كود Hamming Code FEC المتسلسل خصيصًا للوصلة الضوئية، مما يلبي الأخطاء العشوائية النموذجية للاتصالات الضوئية. تخلق طبقة FEC الداخلية توسعًا إضافيًا لمعدل الخط من 212 جيجابت في الثانية إلى 226 جيجابت في الثانية، وبالتالي من الضروري أن تتمكن SerDes من دعم معدل الخط هذا.

تحديات الكمون في أنظمة إيثرنت 1.6T

الشكل 3: مسار زمن الوصول لنظام Ethernet الفرعي 1.6T.

تساهم المكونات المختلفة في زمن انتقال Ethernet: قائمة انتظار الإرسال، ومدة الإرسال، ووقت الاجتياز المتوسط، وأوقات المعالجة والاستلام المتعددة. لتصور ذلك، خذ بعين الاعتبار الشكل 3، الذي يعرض نظامًا فرعيًا شاملاً لشبكة إيثرنت 1.6T. في حين أن زمن الوصول يمكن أن يتأثر بوقت رد الفعل للتطبيق البعيد، فإن هذا العامل يعتبر خارجيًا بالنسبة لشبكة إيثرنت، وبالتالي يتم استبعاده غالبًا أثناء تحليل زمن الوصول. يتطلب تقليل زمن الوصول في واجهة Ethernet فهم الظروف المحددة. على سبيل المثال، قد لا يكون زمن الوصول هو الاهتمام الرئيسي لاتصالات قناة الاتصال بين المحولات بسبب التأخير المتأصل في روابط العميل الأبطأ. تلعب المسافة أيضًا دورًا؛ أطوال أكبر تقدم المزيد من الكمون. بالطبع، هذا لا يعني أنه يجب علينا التغاضي عن زمن الاستجابة في سيناريوهات أخرى، حيث إن تقليل زمن الاستجابة هو هدف دائمًا.

يرتبط زمن انتقال الإرسال بطبيعته بمعدل Ethernet وحجم الإطار. على وجه التحديد، بالنسبة لنظام 1.6T Ethernet، يتطلب إرسال حزمة ذات حجم أدنى 0.4ns - بشكل أساسي، إطار Ethernet واحد لكل علامة على مدار الساعة 2.5 جيجا هرتز. من ناحية أخرى، يستغرق نقل الإطار القياسي ذي الحجم الأقصى 8 نانو ثانية، ويمتد إلى 48 نانو ثانية للإطارات الضخمة. الوسيلة المختارة تملي كذلك الكمون. على سبيل المثال، عادةً ما تتحمل الألياف الضوئية زمن وصول يبلغ 5 نانو لكل متر، في حين أن الكابلات النحاسية أسرع قليلاً بمعدل 4 نانو لكل متر.

جزء كبير من زمن الوصول الإجمالي متجذر في وحدة تحكم جهاز الاستقبال. يُدخل مفكك تشفير RS FEC بطبيعته زمن الوصول. لبدء تصحيح الخطأ، يجب أن يتلقى النظام 4 كلمات تشفير، والتي تصل إلى 1.6 نانو عند سرعة 12.8 تيرابت في الثانية. وتؤدي الأنشطة اللاحقة، بما في ذلك تصحيح الأخطاء والتخزين المؤقت، إلى تضخيم زمن الاستجابة هذا. في حين أن مدة تخزين كلمة المرور الخاصة بـ FEC تظل ثابتة، فإن زمن الوصول أثناء استقبال الرسالة يعتمد على التنفيذ المحدد. ومع ذلك، يمكن تحسين زمن الوصول من خلال استخدام استراتيجيات التصميم الرقمي الدقيقة.

في جوهر الأمر، هناك زمن وصول متأصل لا مفر منه بسبب آلية تصحيح الأخطاء (FEC) والمسافة المادية أو طول الكابل. وبعيدًا عن هذه العوامل، تلعب خبرة التصميم دورًا محوريًا في تقليل زمن الوصول لوحدة تحكم Ethernet. الاستفادة من الحل الكامل الذي يدمج ويحسن MAC وPCS وPHY، يمهد الطريق للتنفيذ الأكثر كفاءة ومنخفض زمن الاستجابة.

نبذة عامة

الشكل 4: نجاح التمرير الأول للسيليكون لـ Synopsys 224G Ethernet PHY IP في عملية 3 نانومتر تعرض عيون PAM-4 الخطية للغاية.

تم تصميم شبكة إيثرنت بسرعة 1.6 تيرابت في الثانية لتناسب التطبيقات الأكثر تطلبًا للنطاق الترددي وحساسة لزمن الوصول. مع ظهور تقنية 224G SerDes، جنبًا إلى جنب مع التطورات في MAC وPCS IP، أصبح من الممكن الآن الوصول إلى حلول شاملة تتوافق باستمرار مع معايير 1.6T Ethernet المتطورة. بالإضافة إلى ذلك، نظرًا لزمن الوصول المتأصل في البروتوكول وطرق تصحيح الأخطاء، يجب تصميم تصميم IP الرقمي والتناظري بعناية من قبل مصممين خبراء لتجنب إدخال زمن انتقال غير ضروري في مسار البيانات.

يتطلب تحقيق أعلى مستويات الأداء لتصميمات 1.6T SoC بنية محسنة بكفاءة وممارسات تصميم دقيقة لكل مكون من مكونات الشريحة. وهذا يؤكد على الحفاظ على الطاقة ويقلل من بصمة السيليكون، مما يجعل معدلات البيانات البالغة 1.6T حقيقة واقعة. Synopsys 224G Ethernet PHY IP الذي أثبت كفاءته في السيليكون مهدت الطريق لوحدة التحكم 1.6T MAC وPCS. باستخدام تقنيات التصميم والتحليل والمحاكاة والقياس الرائدة، تواصل Synopsys تقديم سلامة الإشارة الاستثنائية وأداء الارتعاش، مع حل إيثرنت كامل بما في ذلك MAC+PCS+PHY.

- محتوى مدعوم من تحسين محركات البحث وتوزيع العلاقات العامة. تضخيم اليوم.

- PlatoData.Network Vertical Generative Ai. تمكين نفسك. الوصول هنا.

- أفلاطونايستريم. ذكاء Web3. تضخيم المعرفة. الوصول هنا.

- أفلاطون كربون، كلينتك ، الطاقة، بيئة، شمسي، إدارة المخلفات. الوصول هنا.

- أفلاطون هيلث. التكنولوجيا الحيوية وذكاء التجارب السريرية. الوصول هنا.

- المصدر https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :لديها

- :يكون

- :ليس

- :أين

- $ UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- الوصول

- يمكن الوصول

- المحاسبة

- دقيق

- التأهيل

- في

- أنشطة

- وأضاف

- إضافي

- وبالإضافة إلى ذلك

- اعتماد

- التطورات

- تقدم

- ضد

- تهدف

- سمح

- سابقا

- أيضا

- بالرغم ان

- دائما

- وسط

- المبالغ

- أسهب

- an

- تحليل

- و

- كان متوقعا

- تطبيق

- التطبيقات

- نهج

- هندسة معمارية

- هي

- AS

- At

- تجنب

- الخلفية

- خلفية

- عرض النطاق الترددي

- BE

- يصبح

- ما بين

- Beyond

- قطعة

- حظر

- دعم

- تعزيز

- يجلب

- يبني

- لكن

- by

- كابل

- الكابلات

- CAN

- القدرات

- حمل

- التحديات

- قنوات

- رقاقة

- شيبس

- اختيار

- ظروف

- زبون

- ساعة حائط

- سحابة

- الحوسبة السحابية

- الكود

- الجمع بين

- الجمع بين

- Communication

- إكمال

- إكمال

- عنصر

- مكونات

- شامل

- تضم

- الحوسبة

- قلق

- بالتزامن

- متصل

- التواصل

- صيانة

- نظر

- الاعتبارات

- ثابتة

- تواصل

- بشكل متواصل

- المساهمة

- مراقبة

- مراقب

- تحويل

- النحاس

- جوهر

- التكاليف

- مواجهة

- الدورة

- وضعت

- يخلق

- حالياًّ

- البيانات

- مراكز البيانات

- لاول مرة

- التأخير

- نقل

- الطلب

- يطالب

- مطالب

- تصور

- تصميم

- المصممين

- تصاميم

- كشف

- الأجهزة

- يمليه

- مختلف

- رقمي

- بجد

- يعرض

- مسافة

- وزعت

- لا

- مضاعفة

- اثنان

- مدة الأقامة

- أثناء

- كل

- في وقت سابق

- النظام الإيكولوجي

- الطُرق الفعّالة

- على نحو فعال

- كفاءة

- فعال

- بكفاءة

- جهود

- ظهور

- يؤكد

- مؤكدا

- يعمل

- توظيف

- تمكن

- تمكين

- يشمل

- النهاية

- النهائي إلى نهاية

- يضمن

- كامل

- خطأ

- أخطاء

- التصعيد

- جوهر

- أساسي

- أساسيا

- الأثير (ETH)

- حتى

- كل

- واضح

- المتطورة

- مثال

- استثنائي

- استبعاد

- توسيع

- توسع

- متوقع

- خبير

- خبرة

- مد

- إطالة

- خارجي

- استخلاص

- العيون

- عامل

- العوامل

- بعيدا

- أسرع

- المميزات

- ويتميز

- الشكل

- الاسم الأول

- الجيل الاول

- تدفق

- ركز

- يتبع

- البصمة

- في حالة

- صياغة

- إلى الأمام

- FRAME

- تبدأ من

- إضافي

- جيل

- يعطي

- أكبر

- تجمع

- مجموعات

- متزايد

- يد

- معالجة

- مرتفع

- أداء عالي

- جدا

- لكن

- HTML

- HTTPS

- صيغة الامر

- التنفيذ

- أهمية

- أهمية

- تحسن

- in

- في أخرى

- تتضمن

- بما فيه

- في ازدياد

- فرد

- صناعي

- تأثر

- متأصل

- متأصل

- بدء

- مبادرة

- مثل

- يدمج

- التكامل

- سلامة

- السطح البيني

- واجهات

- Internet

- التوافقية

- إلى

- جوهري

- تقديم

- يدخل

- إدخال

- ينطوي

- IP

- IT

- التكرارات

- انها

- نفسها

- JPG

- ممر

- كمون

- طبقة

- طبقات

- الطول

- ومستوياتها

- الاستفادة من

- على الأرجح

- خط

- خطوط

- LINK

- وصلات

- حي

- يعد

- منخفض

- لجنة الهدنة العسكرية

- القيام ب

- إدارة

- إدارة

- ماكس العرض

- أقصى

- مايو..

- تعني

- قياس

- آلية

- متوسط

- مكبر الصوت : يدعم، مع دعم ميكروفون مدمج لمنع الضوضاء

- الرسالة

- طريقة

- طرق

- شديد التدقيق

- أدنى

- تقليل

- يقلل

- التقليل

- وحدة

- الوحدات

- الأكثر من ذلك

- أكثر

- يجب

- تقترب

- حاجة

- الشبكات

- مع ذلك

- لا

- لاحظ

- الآن

- موضوعي

- of

- غالبا

- on

- ONE

- فقط

- تعمل

- الأمثل

- المثلى

- خيار

- or

- أخرى

- على مدى

- الكلي

- أزواج

- المعلمات

- خاصة

- مسار

- أجهزة الكمبيوتر

- إلى

- أداء

- العروض

- مادي

- جسديا

- خط أنابيب

- محوري

- أفلاطون

- الذكاء افلاطون البيانات

- أفلاطون داتا

- يلعب

- المزيد

- محتمل

- قوة

- الممارسات

- في المقام الأول

- ابتدائي

- عملية المعالجة

- معالجة

- المعالجات

- تقدم

- المتوقع

- الحماية

- بروتوكول

- نبض

- غرض

- دفع

- جودة

- راديو

- عشوائية

- نطاق

- معدل

- الأجور

- الوصول

- الوصول إلى

- رد فعل

- واقع

- تسلم

- يستلم

- استقبال

- تقليص

- الخدمة الموثوقة

- بقايا

- أداء

- يتطلب

- مقيد

- مما أدى

- قوي

- النوع

- راسخ

- تشغيل

- التدرجية

- حجم

- سيناريوهات

- سلس

- الثاني

- رأيت

- قطعة

- حساس

- مستقل

- خدمة

- الخدمة

- طقم

- عدة

- شاركت

- قصير

- ينبغي

- التفضيل

- سيجنل

- بشكل ملحوظ

- السيليكون

- محاكاة

- المقاس

- So

- حل

- الحلول

- يمتد

- قيادة

- محدد

- على وجه التحديد

- مواصفة

- بسرعة

- الربيع

- المسرح

- معيار

- التقييس

- المعايير

- تخزين

- استراتيجيات

- متدفق

- لاحق

- جوهري

- تحقيق النجاح

- هذه

- مناسب

- الدعم

- رمز

- نظام

- تناسب

- يأخذ

- تقنية

- تقنيات

- تكنولوجيا

- من

- أن

- •

- من مشاركة

- هناك.

- وبالتالي

- وبالتالي

- تشبه

- عبر

- وهكذا

- علامة

- مربوط

- الوقت

- مرات

- إلى

- تيشرت

- تقليدي

- حركة المرور

- تحويل

- نقل

- الثلاثي

- اثنان

- نموذجي

- عادة

- لا مفر منه

- فهم

- تعهد

- وحدة

- المقبلة

- بناء على

- استخدام

- الاستفادة من

- بواسطة

- تصور

- طريق..

- we

- متى

- التي

- في حين

- على نطاق أوسع

- مع

- في غضون

- سوف

- حتى الآن

- زفيرنت

- صفر