回来了 1991 Cadence 首次宣布了 Virtuoso 产品名称,32 年后的今天,该产品仍然存在并且表现良好。 Cadence 的 Steven Lewis 向我介绍了他们称之为新事物的最新情况 大师工作室,这都是关于现实世界的定制 IC 设计。 在这 32 年里,我们看到半导体工艺沿着摩尔定律前进,从使用平面 CMOS 的 600 纳米,缩小到 22 纳米以下的 FinFET 时代,并在 3 纳米节点达到 GAA。 显然,随着更小的节点带来新的物理效应,需要对其进行建模和仿真以确保首次硅片成功,EDA 工具的需求已经发生了变化。

Cadence Virtuoso Studio 的重点是通过六个领域帮助 IC 设计人员应对当今的挑战:

- 工艺复杂性增加

- 处理 10,000 次电路仿真

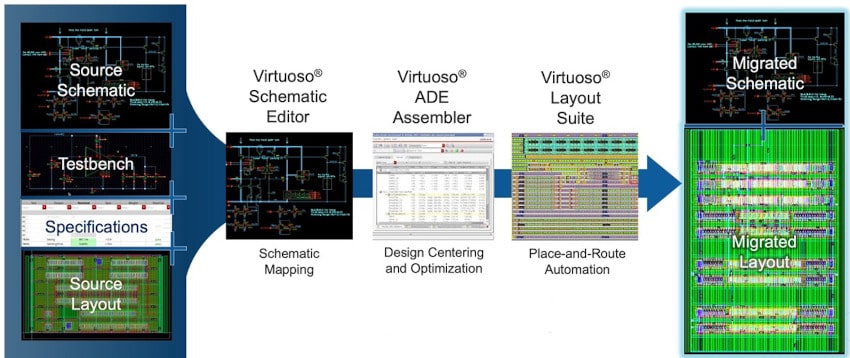

- 设计自动化和电路迁移

- 异构集成

- AI

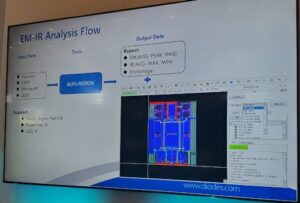

- 签核、设计内验证和分析

大师级ADE (模拟设计环境)允许电路工程师通过原理图捕获和电路仿真来探索他们的模拟、混合信号和 RFIC 设计。 Virtuoso ADE 的架构经过了改进,可以更好地进行作业控制,减少 RAM 使用,并通过使用云加速模拟。 例如,在 10,000 次模拟中运行 Spectre 所需的 RAM 从 420MB 减少到仅 18MB,用于模拟监控,而表达式评估 RAM 则从 420MB 减少到仅 280MB。

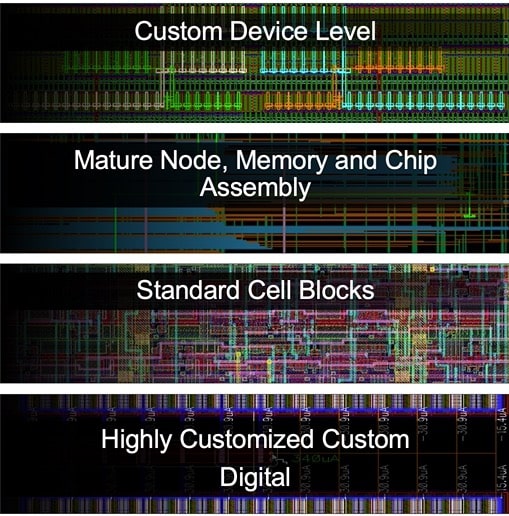

更新到 Virtuoso 布局套件 包括四种布局布线技术选择,每种技术都适合通过 Virtuoso 环境处理手头的独特任务:

四大P&R技术

DRC 和 LVS 运行是物理验证的一部分,并且以批处理模式运行这些、修复和重复,会导致较长的开发进度。 设计内验证允许在处理 IC 布局时交互式使用 DRC 和 LVS,因此可以快速突出显示有关更改内容的反馈,从而提高生产效率。 使用 Virtuoso Layout Suite 的布局设计师可以通过使用以下方法进行设计内验证: 飞马 DRC和LVS技术。

小芯片、2.5D 和 3D 封装跨越了传统上独立的 PCB、封装和 IC 设计领域。 Virtuoso Studio 通过以下方式实现封装、模块和 IC 的协同设计和验证:

展望不久的将来,您可以期待看到有关如何应用人工智能自动从模拟原理图转变为基于机器学习和规范的布局的详细信息。 这些自动生成的试验布局将进一步加快劳动密集型流程。 人工智能应用的第二个发展领域是将定制模拟 IP 迁移到新工艺节点的问题。 敬请关注。

Virtuoso Studio 的早期客户包括负责 IC 和封装协同设计的 Analog Devices、联发科技的领先 IC 消费类设计以及瑞萨电子基于人工智能的流程迁移。

总结

Virtuoso Studio 在 23.1 版本中加入了一些令人印象深刻的新功能,IC 设计团队可以开始使用这些功能来提高工作效率。 Virtuoso 基础设施已经改变,以应对摩尔定律的挑战,10,000 次电路仿真的模拟是实用的,支持 RFIC 和模块 2.5D/3D 协同设计,设计内 DRC/LVS 验证所需的时间大大减少,并且 AI被应用于自动化模拟任务。

相关博客

通过以下方式分享此帖子:- SEO 支持的内容和 PR 分发。 今天得到放大。

- 柏拉图区块链。 Web3 元宇宙智能。 知识放大。 访问这里。

- 与 Adryenn Ashley 一起铸造未来。 访问这里。

- Sumber: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :具有

- :是

- $UP

- 1

- 10

- 3d

- a

- 关于我们

- 加速

- AI

- 所有类型

- 允许

- 沿

- 和

- 公布

- 应用的

- 架构

- 保健

- 国家 / 地区

- 地区

- AS

- At

- 自动化

- 自动

- 自动化

- 背部

- 基于

- BE

- 很

- 作为

- 如下。

- 好处

- 更好

- 带

- by

- Cadence公司

- 呼叫

- CAN

- 捕获

- 挑战

- 更改

- 选择

- 明确地

- 云端技术

- 消费者

- 控制

- 习俗

- 合作伙伴

- 天

- 需求

- 设计

- 设计师

- 设计师

- 设计

- 详情

- 研发支持

- 设备

- 做

- 域名

- 向下

- 每

- 影响

- 使

- 工程师

- 确保

- 环境

- 时代

- 评价

- 例子

- 期望

- 探索

- 特征

- 反馈

- 姓氏:

- 专注焦点

- 针对

- 四

- 止

- 进一步

- 未来

- Go

- 手

- 有

- 帮助

- 点击此处

- 突出

- 创新中心

- HTML

- HTTPS

- ICS

- 有声有色

- in

- 包括

- 基础设施

- 互动

- IP

- 工作

- JPG

- 劳工

- 法律

- 布局

- 信息

- 学习

- 刘易斯

- 长

- 机

- 机器学习

- 三月

- 最大宽度

- 满足

- 移民

- 时尚

- 模块

- 模块

- 监控

- 更多

- 姓名

- 近

- 打印车票

- 全新

- 新功能

- 节点

- 节点

- of

- on

- 一

- 包

- 包

- 包装

- 部分

- 的

- 地方

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 帖子

- 实用

- 当下

- 市场问题

- 过程

- 产品

- 生产力

- 生产率

- 放

- 很快

- 内存

- 达

- 真实

- 真实的世界

- 减少

- 减少

- 释放

- 必须

- 路线

- 运行

- 运行

- 缩放

- 其次

- 查看具体信息

- 半导体

- 分开

- 硅

- 模拟

- SIX

- 小

- So

- 一些

- 东西

- 跨度

- 规格

- 幽灵

- 速度

- 开始

- 留

- 工作室

- 成功

- 套房

- 支持

- 采取

- 需要

- 任务

- 任务

- 队

- 专业技术

- 这

- 其

- 博曼

- 通过

- 次

- 至

- 工具

- 传统

- 试用

- 独特

- 更新

- 用法

- 使用

- 企业验证

- 通过

- 井

- 什么是

- 而

- 将

- 加工

- 世界

- 年

- 和风网