在人工智能 (AI) 和数据密集型应用快速发展的环境中,对高性能互连技术的需求从未如此迫切。即使是 100G 互连,对于基础设施应用来说也不够快。人工智能应用程序以其庞大的数据集和复杂的算法,推动了对前所未有的数据传输速度的需求。 224G 串行器/解串器 (SerDes) 站在高速数据通信革命的最前沿,开创了前所未有的性能和适应性的新时代。

Alphawave 认识到这一市场需求,并通过其尖端的 200G 互连技术正面满足这一需求。这证明了该公司致力于保持数据曲线领先地位,为各行业提供推动人工智能和高性能计算走向未来所需的速度和效率。

最近,该公司举办了有关此主题的网络研讨会,并分享了 AthenaCORE 224G SerDes 测试芯片的结果。 这篇文章探讨了 Alphawave 通过其全面的产品(包括 1.6G 互连技术)来释放 200T 生态系统的努力。

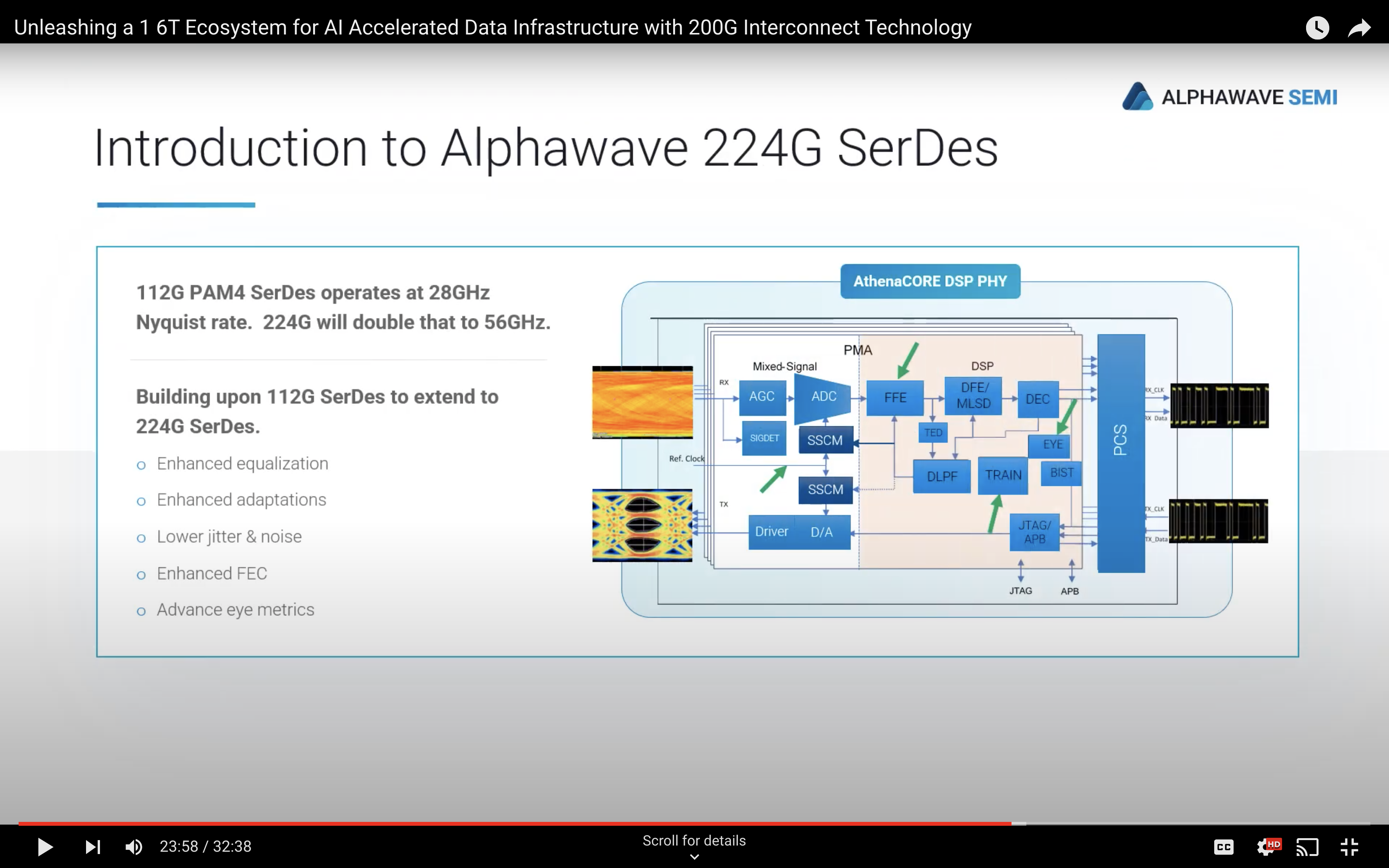

利用 Alphawave 的 112G SerDes 成功提供强大的 224G SerDes

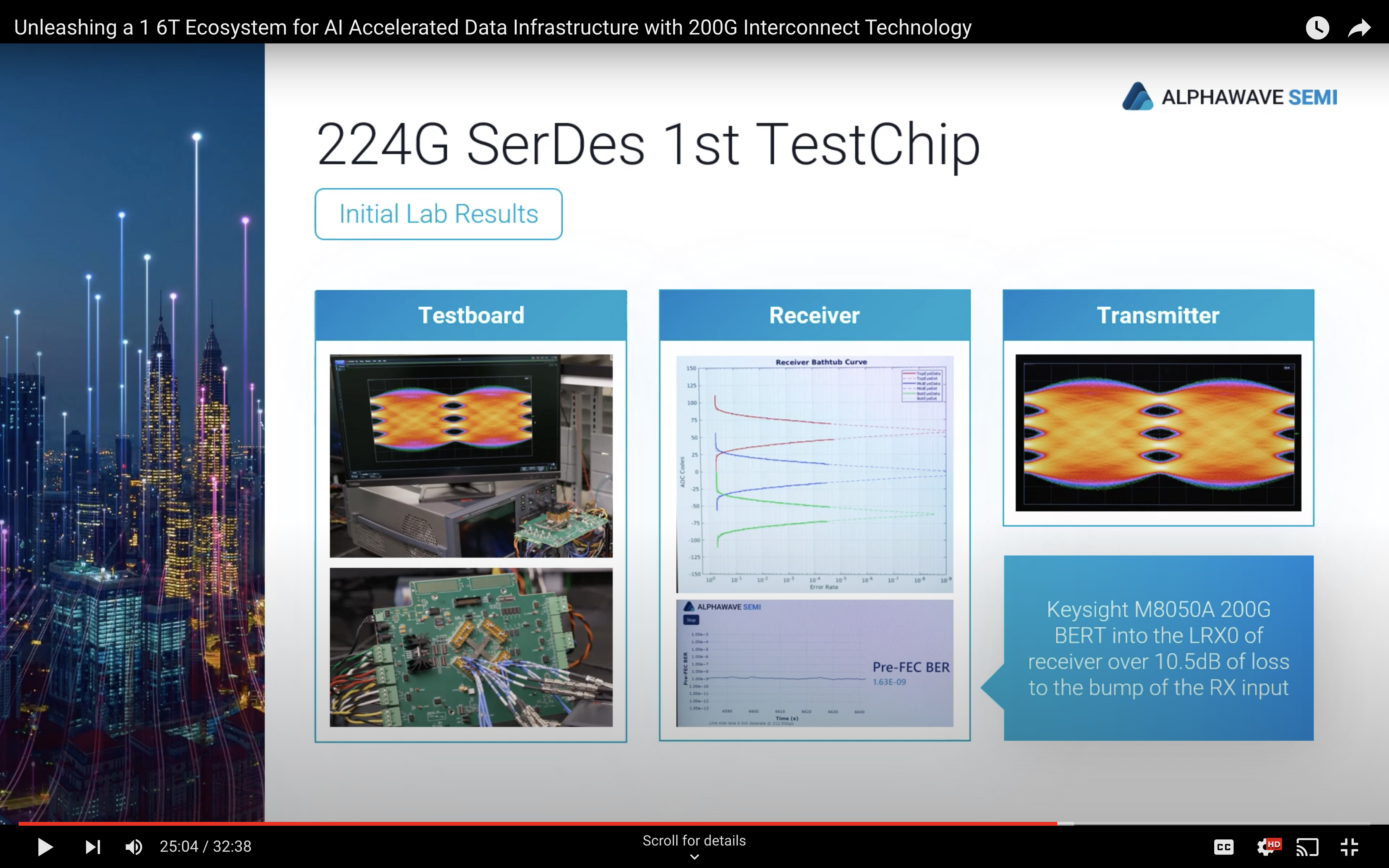

通过扩展其经过验证的 112G SerDes 以支持卓越的 224Gbps,Alphawave 不仅将数据速率提高了一倍,而且还为数据密集型应用开辟了新的可能性,特别是在人工智能 (AI) 和高级计算领域。克服 200G 互连的相关挑战和复杂性需要结合先进技术、创新设计方法和行业内的协作努力。 Alphawave 在 112G SerDes 成功的基础上,满足了 224G SerDes 更严格的要求。

基于 AlphaCORE DSP 的串行器/解串器 (SerDes) 架构旨在提供多功能高速数据通信解决方案,具有可配置的 112G 数字信号处理器 (DSP)。 DSP 架构的可配置性能够适应不同的应用和性能需求,提供即插即用的模块化设计,实现可互换性和轻松集成。该架构以每秒 112 吉比特 (112G) 的数据速率运行,符合数据中心、网络和高性能计算等领域的现代数据通信要求。 SerDes 强调应用定制解决方案、灵活性和适应性,可以根据特定用例进行定制,展示其针对不同应用和环境优化性能的能力。 DSP 的加入强调了它在均衡、纠错和信号调理等任务中的重要性。该架构旨在易于集成并适应各种即插即用模块,确保与不同组件和功能的无缝兼容。作为一种高速通信解决方案,该架构满足不断变化的数据速率需求,并与通信标准的进步保持一致,使其非常适合动态和面向未来的通信环境。

AthenaCORE 224G SerDes 测试芯片结果

Alphawave的创新发展努力

Alphawave 的 200G 互连技术不仅关乎速度,还关乎效率和可靠性。 200G 互连挑战包括信号完整性问题、串扰和色散。该公司投资先进的调制方案,例如 PAM4(脉冲幅度调制 4),它允许在单个符号中编码多个位,从而有效提高数据速率。 Alphawave还部署了先进的DSP技术和自适应纠错方案,以增强200G速度下数据传输的可靠性和性能。

先进的 DSP 技术

最大似然序列检测器 (MLSD) 代表通信系统中采用的复杂数字信号处理 (DSP) 技术,在具有符号间干扰 (ISI) 的场景中尤其有效。与旨在消除 ISI 的传统方法不同,MLSD 独特地利用干扰中的能量来提高信号功率,从而优化符号序列检测。其数学上的最佳方法涉及对所有可能的符号序列进行详尽的搜索,最小化均方误差以识别传输的序列。 MLSD 因其显着增强系统性能的能力而闻名,特别适用于高速数据通信和光通信,解决了 ISI 引起的信号失真问题。虽然 MLSD 的计算需求提高了复杂性考虑因素,但该技术对不同信道条件的适应性强调了其在动态通信环境中的功效。

前向纠错 (FEC) 策略

Alphawave 采用自适应前向纠错 (FEC) 策略,允许根据实时信道条件进行动态调整。这种灵活性可确保在不影响带宽效率的情况下实现最佳性能。 FEC 使系统能够在电气链路上建立更高的误码率 (BER) 目标,从而提供容忍和纠正错误的阈值。自适应FEC根据实时信道状况动态调整纠错强度,平衡纠错和带宽效率。自适应和动态 FEC 策略的兴起增强了系统适应性,同时与先进调制方案的集成优化了性能,特别是在高速和光通信系统中。

支持1.6T生态系统的多功能选项

Alphawave 为 1.6T 生态系统中的交换机 ASIC(专用集成电路)提供了多种选择。这包括能够在 512RU – 100 端口交换机配置中坚持使用 256 × 200G 链路或利用 1 x 32G 链路,从而为不同的部署场景提供可扩展性和灵活性。该公司支持 UCle 的小芯片为芯片级模块化和可扩展性开辟了新的可能性,以满足基础设施应用的高速内存和计算需求。凭借其 2.5D/3D 封装和应用优化的 IP,该公司在复杂性和性能之间取得微妙的平衡,以提供先进的解决方案。

多供应商互操作性

互操作性鼓励创新,涵盖各个维度,包括外形尺寸、SerDes 接口和管理软件,最终目标是实现系统兼容性。多供应商互操作性是新技术采用和成功的关键因素。早期采用者受益于更广泛的兼容产品,而下游实施者则利用互操作性来简化开发,减少时间和成本。通过设定性能标准,互操作性可确保用户可以预测不同组件如何在系统中协同工作。在可互操作解决方案的多样化生态系统中的竞争的推动下,这可以促进更快地获得低成本技术。

与标准机构合作

Alphawave 了解多供应商互操作性的重要性,并积极与 OIF(光互联论坛)和 IEEE 802.3 等行业标准机构合作,为 200G 信令标准的开发做出贡献。此次合作确保了互操作性,并为 Alphawave 技术无缝集成到更广泛的生态系统奠定了基础。 Alphawave 强大的规格和对行业标准的遵守确保其 200G 互连技术能够与各种系统无缝集成。

总结

通过积极贡献行业标准、投资先进技术、提供多功能解决方案,Alphawave 成为人工智能时代 1.6T 生态主流的重要参与者。 Alphawave 提供专为高性能连接而设计的一整套解决方案。他们的高性能连接 IP 跨越 PCIe/CXL、以太网和 HBM/DDR 等关键领域,满足高速数据通信的需求。小芯片技术的结合,特别是利用 UCle,表明了对无缝小芯片互连的承诺。特定的小芯片类型(IO、内存和计算)强调模块化方法,允许不同的小芯片和谐地协同工作。

随着数据密集型应用的不断发展,Alphawave 对创新的承诺使其成为未来高速、可靠和可扩展的人工智能数据基础设施的关键推动者。从本质上讲,Alphawave 是为即将到来的 1.6T 生态系统实现灵活性、可扩展性和创新的关键参与者。

另请参阅:

分解系统:通过 UCIe 互连和基于 Chiplet 的设计实现计算

2022 年接口 IP:同比增长 22% 仍以数据为中心驱动

通过以下方式分享此帖子:

- SEO 支持的内容和 PR 分发。 今天得到放大。

- PlatoData.Network 垂直生成人工智能。 赋予自己力量。 访问这里。

- 柏拉图爱流。 Web3 智能。 知识放大。 访问这里。

- 柏拉图ESG。 碳, 清洁科技, 能源, 环境, 太阳能, 废物管理。 访问这里。

- 柏拉图健康。 生物技术和临床试验情报。 访问这里。

- Sumber: https://semiwiki.com/ip/alphawave/339080-unleashing-the-1-6t-ecosystem-alphawave-semis-200g-interconnect-technologies-for-powering-ai-data-infrastructure/

- :具有

- :是

- :不是

- $UP

- 1

- 1

- 2022

- 32

- a

- 对,能力--

- 关于

- ACCESS

- 实现

- 横过

- 积极地

- 适应

- 自适应

- 地址

- 地址

- 解决

- 遵守

- 调整

- 采纳者

- 采用

- 高级

- 进步

- 向前

- AI

- 人工智能数据

- 瞄准

- 算法

- 对齐

- 所有类型

- 允许

- 允许

- 已经

- 还

- an

- 和

- 预料

- 应用领域

- 应用的

- 的途径

- 方法

- 架构

- 保健

- 地区

- 人造的

- 人工智能

- 人工智能(AI)

- AS

- 上升

- 亚瑟士

- 相关

- At

- 当前余额

- 平衡

- 带宽

- 基于

- BE

- 很

- 得益

- 之间

- 位

- 机构

- 促进

- 更广泛

- 建

- 但是

- by

- 被称为

- CAN

- 容量

- 例

- 餐饮

- 中心

- 挑战

- 渠道

- 合作

- 共同

- 组合

- 承诺

- 沟通

- 通讯系统

- 通信

- 公司

- 公司的

- 兼容性

- 兼容

- 竞争

- 复杂

- 复杂性

- 复杂

- 组件

- 全面

- 折中

- 计算

- 计算

- 计算

- 关注

- 条件

- 配置

- 连接方式

- 注意事项

- 继续

- 贡献

- 贡献

- 常规

- 成本

- 危急

- 关键

- 曲线

- 前沿

- data

- 数据中心

- 数据基础设施

- 数据集

- 交付

- 需求

- 需求

- 部署

- 部署

- 设计

- 设计

- 检测

- 研发支持

- 不同

- 数字

- 尺寸

- 分散

- 不同

- 翻倍

- 驱动

- 驾驶

- 两

- 动态

- 动态

- 早

- 早期采用者

- 缓解

- 易

- 生态系统

- 有效

- 只

- 功效

- 效率

- 工作的影响。

- 消除

- 拥抱

- 重点

- 就业

- 授权

- 如虎添翼

- 推动者

- 使

- 使

- 能源

- 订婚

- 设计

- 提高

- 增强

- 更多

- 确保

- 确保

- 环境中

- 时代

- 错误

- 故障

- 本质

- 建立

- 甚至

- 发展

- 演变

- 延长

- 因素

- 因素

- 高效率

- 特色

- 字段

- 高度灵活

- 针对

- 第一线

- 申请

- 论坛

- 向前

- 寄养

- 止

- 功能

- 功能

- 未来

- 目标

- 事业发展

- 相关信息

- 高性能

- 更高

- 托管

- 创新中心

- HTTPS

- 鉴定

- IEEE

- 重要性

- 重要

- in

- 包括

- 包括

- 包含

- 包容

- 增加

- 表示

- 行业

- 行业中的应用:

- 行业标准

- 基础设施

- 創新

- 创新

- 整合

- 集成

- 积分

- 诚信

- 房源搜索

- 接口

- 干扰

- 互操作性

- 互操作性

- 成

- 投资

- 投资

- 涉及

- IP

- 问题

- IT

- 它的

- 键

- 关键球员

- 景观

- 杠杆作用

- 借力

- 喜欢

- 可能性

- 链接

- 看

- 主流

- 制作

- 颠覆性技术

- 市场

- 大规模

- 数学

- 最大宽度

- 意味着

- 会见

- 内存

- 方法

- 最小化

- 现代

- 模块化

- 模块

- 更多

- 多

- 导航

- 需求

- 打印车票

- 工业网络

- 决不要

- 全新

- 新技术

- 特别是

- of

- 提供

- 供品

- 优惠精选

- on

- 仅由

- 打开

- 操作

- 最佳

- 优化

- 优化

- 追求项目的积极优化

- 附加选项

- or

- 超过

- 克服

- 包装

- 尤其

- 为

- 性能

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 播放

- 播放机

- 插头

- 即插即用

- 职位

- 可能性

- 可能

- 帖子

- 功率

- 供电

- 处理

- 处理器

- 核心产品

- 推进

- 成熟

- 提供

- 优

- 脉冲

- 更快

- 提高

- 范围

- 急速

- 率

- 价格表

- 阅读

- 实时的

- 境界

- 确认

- 认识

- 减少

- 有关

- 可靠性

- 可靠

- 卓越

- 代表

- 岗位要求

- 成果

- 革命

- 健壮

- 可扩展性

- 可扩展性

- 情景

- 方案

- 无缝的

- 无缝

- 搜索

- 其次

- 半

- 序列

- 套数

- 设置

- 共用的,

- 陈列宣传

- 信号

- 意义

- 显著

- 单

- 软件

- 方案,

- 解决方案

- 极致

- 跨度

- 具体的

- 规格

- 速度

- 速度

- 广场

- 阶段

- 标准

- 看台

- 住宿

- 棒

- 仍

- 策略

- 精简

- 实力

- 严格

- 成功

- 这样

- 套房

- SUPPORT

- Switch 开关

- 符号

- 系统

- 产品

- 量身定制

- 需要

- 目标

- 任务

- 技术

- 技术

- 技术

- 专业技术

- 遗嘱

- 这

- 未来

- 其

- Free Introduction

- 门槛

- 次

- 至

- 一起

- 明天

- 主题

- 对于

- 转让

- 全功能包

- 下划线

- 理解

- 独特地

- 肆行

- 不像

- 史无前例

- 即将上市

- 上

- 使用

- 用户

- 迎来

- 各种

- 各个

- 变化

- 多才多艺

- 通过

- 参观

- 网络研讨会

- 这

- 而

- 将

- 中

- 也完全不需要

- X

- 和风网