SPIE 高级光刻会议于 XNUMX 月举行。 我最近有机会采访了 imec 先进图案化工艺和材料副总裁 Steven Scheer,并回顾了 imec 展示的精选论文。

我问史蒂夫今年 SPIE 的首要信息是什么,他说为 High NA 做好准备是关键。 他确定了三个关键的生态系统领域:

- 遮罩和分辨率增强技术 (RET) 基础设施。

- 材料、光刻胶和底层。

- 度量衡学

曝光工具当然也很关键,但这不是史蒂夫所说的。 作者注——我也会写一篇关于 ASML 的 SPIE 演示文稿的文章。

面膜

Steve 继续列出与面具相关的问题:

- 屏蔽 3d 效果,例如焦点偏移和对比度损失 – 高 NA 是低角度曝光,使 3D 效果成为一个更大的问题。

- 低缺陷率掩模坯料和具有低粗糙度和 CD 可变性的掩模

- 需要低 n 掩模来实现更高的对比度并减少掩模 3D 效果。

- 光学邻近校正技术。

- 掩码书写,多光束。

- 掩模拼接——较小尺寸的扫描仪区域需要将芯片拼接在一起。

- 4x 一个方向,8x 其他方向需要一种新型的面罩设计来实现拼接。

- 用于更高源能的薄膜。

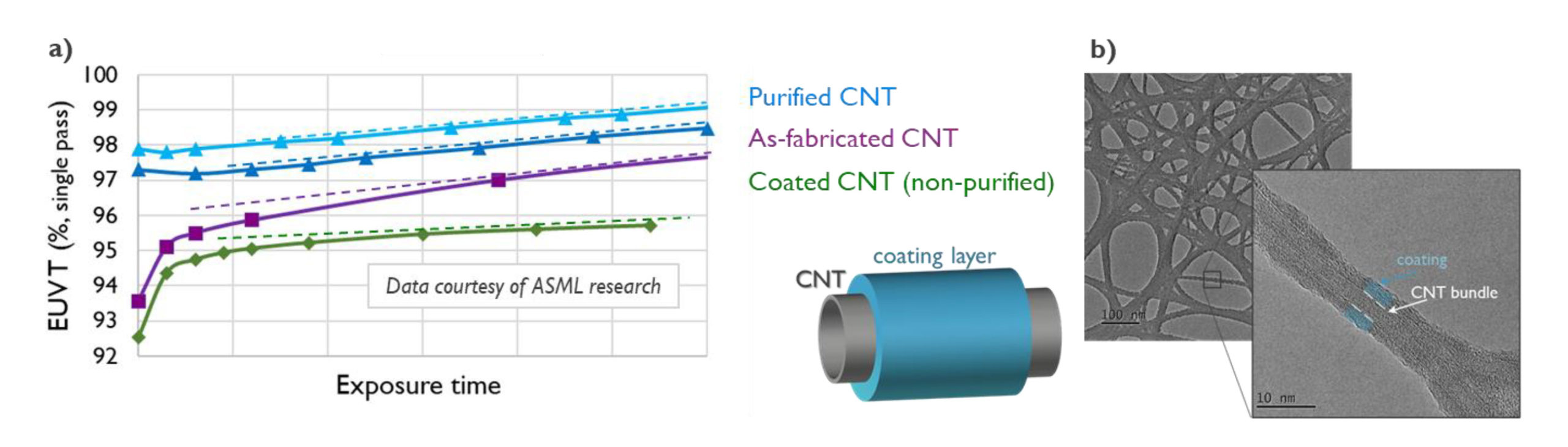

In “CNT 薄膜:最近的优化和曝光结果,” Joost Bekaert 等人探索了碳纳米管薄膜 (CNT)。

ASML 在他们的路线图上有 600 瓦的源系统,目前基于金属硅化物的薄膜只能达到大约 400 瓦。 薄膜需要阻挡颗粒、具有高透射率、足够的机械强度以悬浮在大约 110 毫米乘 140 毫米的区域上,并且耐用。 CNT 显示出高达 98% 的透射率。 EUV 辐射能量如此之高,以至于它会产生氢等离子体,蚀刻薄膜,最终导致薄膜失去机械完整性。 imec 一直在评估蚀刻速率以及如何稳定薄膜。

可以通过观察透射率来评估蚀刻速率,因为薄膜通过蚀刻变薄,透射率增加。 图 1 说明了受各种条件影响的薄膜随时间的传输。

ASML 使用离线等离子曝光工具评估薄膜传输与曝光时间的关系,在这项工作中,imec 展示了多达 3,000 个晶圆的 CNT 薄膜曝光(96 个芯片,每个晶片 30 mJ/cm²),并显示了从实际扫描仪曝光获得的结果之间的相关性以及来自离线工具的那些。

薄膜最初在制造过程中含有挥发性有机杂质,这些杂质会吸收 EUV 能量,直到它们燃烧殆尽,请参见绿色和紫色曲线。 在高温下烘烤薄膜通过燃烧掉污染物来“净化”薄膜,从而导致蚀刻速率主导的传输变化。 两条蓝色曲线的斜率是由蚀刻速率引起的。 绿色曲线表示具有较低蚀刻速率的“涂层”薄膜,但涂层会降低透射率并且可能与非常高的功率水平不兼容。

光刻胶

史蒂夫,然后讨论了光刻胶。

对于光刻胶,24 纳米到 20 纳米的间距是高 NA 插入的最佳点,而 16 纳米间距是最终分辨率。 化学增幅抗蚀剂 (CAR) 在 24nm 以下性能较差。 低至 17 纳米甚至 16 纳米的金属氧化物抗蚀剂 (MOR) 看起来很有希望。 缺陷仍然是一个问题。 24nm 间距的剂量为 67mJ/cm2 对于 MOR 和 77mJ/cm2 汽车。 MOR 存在一些稳定性问题,剂量越低,抗蚀剂的反应性越强/稳定性越差。 这些是挑战,而不是阻碍。

In “按比例缩小用于 EUV 光刻的沉积底层,” Gupta 等人探索了光刻胶底层。 随着间距缩小,对于相同的光致抗蚀剂层,纵横比增加并且可能导致图案倒塌。 改进的底层附着力可以解决这个问题。 或者,可以使用更薄的光刻胶来控制纵横比,但这会导致蚀刻问题,除非可以找到高蚀刻选择性的下层。

imec 发现沉积底层的表面能可以与光致抗蚀剂相匹配,以提高附着力。 沉积底层的密度调整可用于提供改善的蚀刻选择性。

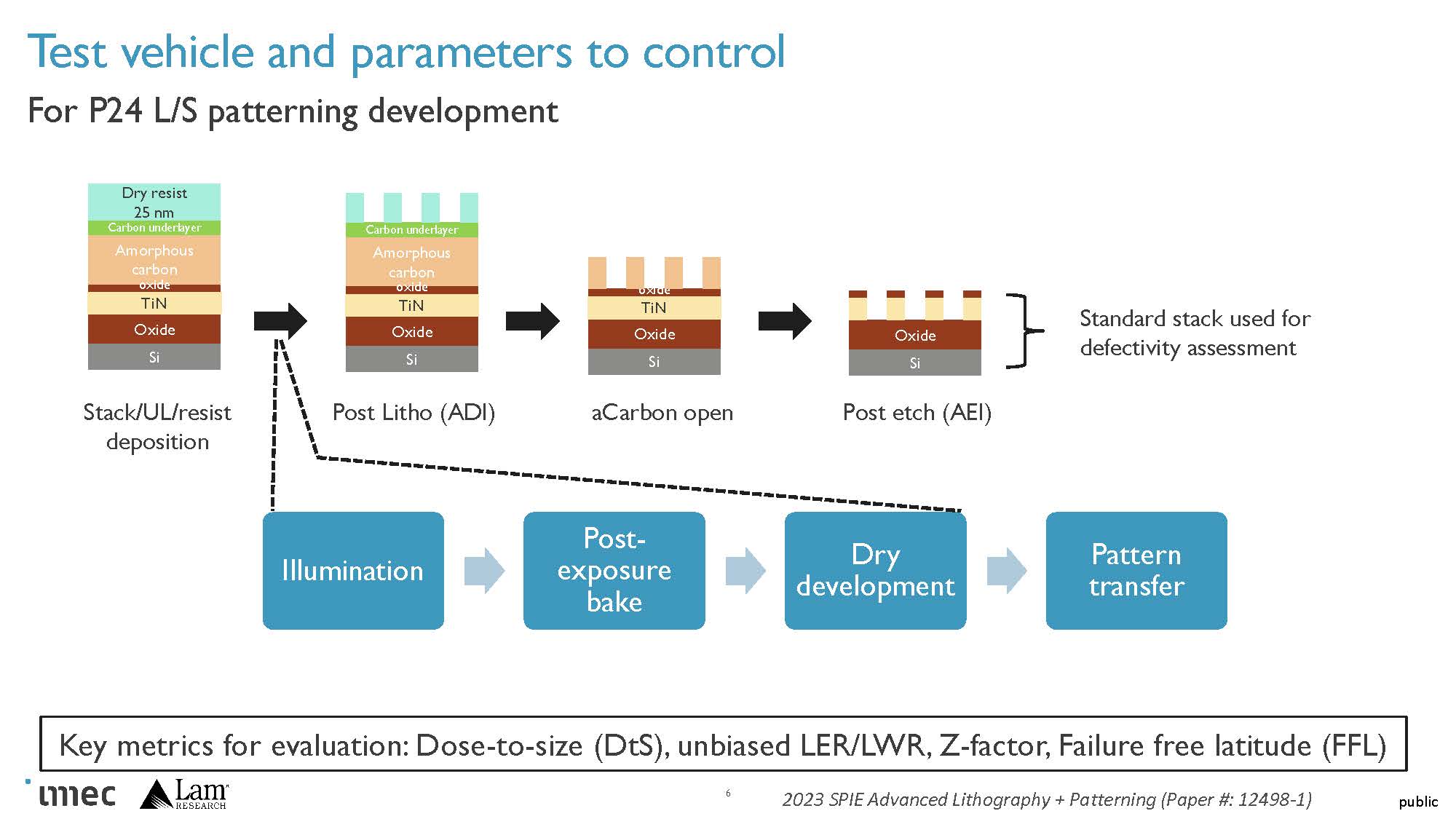

In “高 NA EUV 光刻的干式抗蚀剂图案准备就绪,” 来自 imec 和 Lam 的 Hyo Sean Suh 等人探索了 Lam 的干式光刻胶工艺。 对于 N2+ 和 A14 工艺,金属 2 间距 (M2P) 预计约为 24nm,尖端到尖端 (T15T) 为 2nm,然后在 A10 中,M2P 约为 22nm,T15T <2nm。

Lam 干式抗蚀剂工艺如图 2 所示。

发现曝光后烘烤 (PEB) 可强烈推动剂量减少,但会影响桥接和粗糙度。 协同优化开发和蚀刻可减轻桥接和粗糙度,并显示出用于 24 纳米间距 L/S 图案化的稳健工艺窗口。

In “使用 0.55NA EUV 单一图案进行逻辑金属缩放的可行性,” 徐东波等。 描述了对 High-NA (0.55NA) 系统可以通过单一图案实现的评估。

他们得出结论,24 纳米间距看起来是可以实现的。 20nm 在水平方向看起来很有希望,但垂直方向需要更多工作。 18nm 间距需要额外的工作。

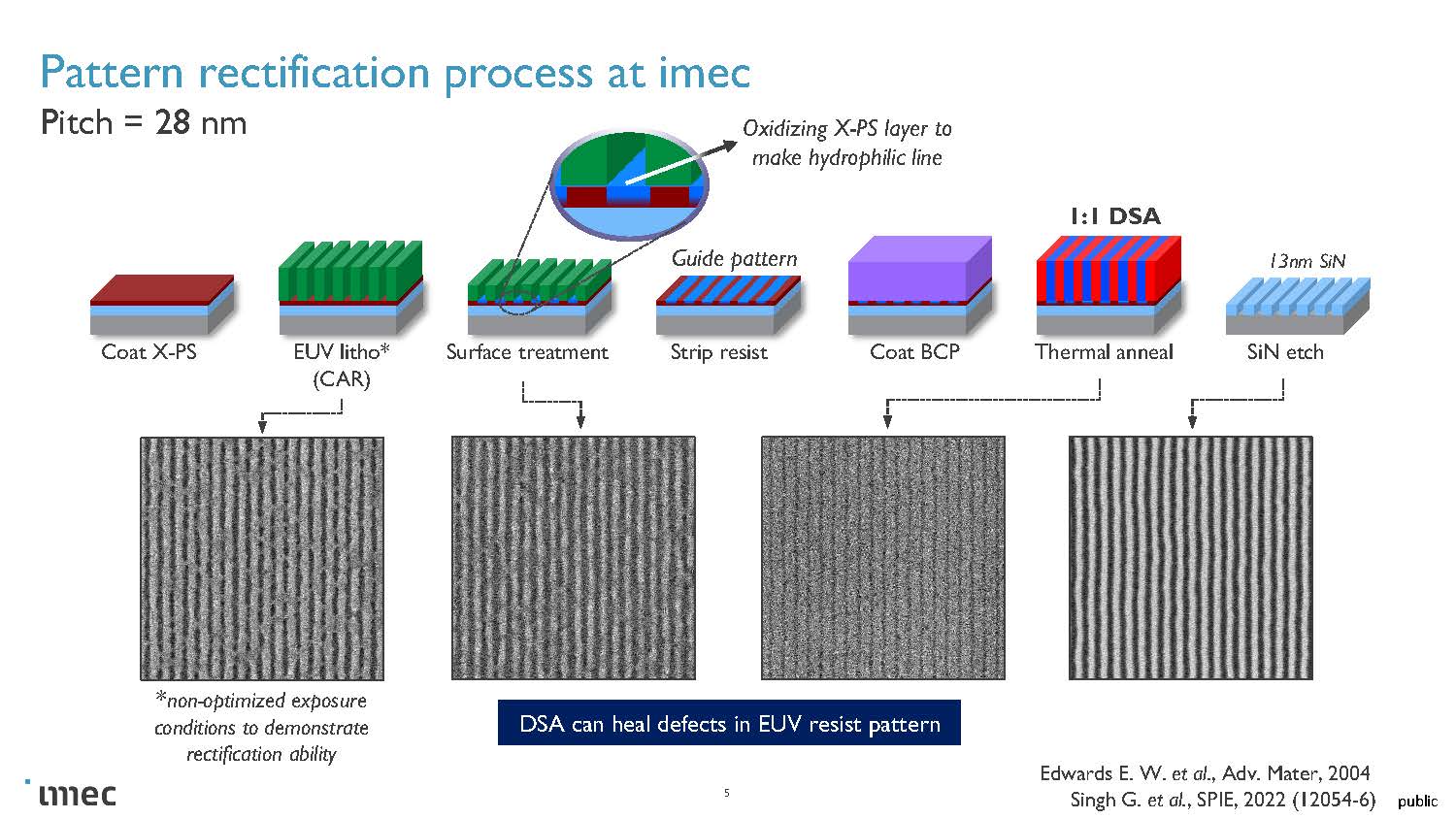

从线粗糙度和随机缺陷的角度来看,EUV 已被证明是一项非常具有挑战性的技术。 定向自组装 (Directed Self Assembly, DSA) 是一项已经存在很长时间但尚未引起太大关注的技术。 DSA 现在作为一种解决 EUV 线粗糙度和随机缺陷的技术而受到关注。

In “使用嵌段共聚物定向自组装的 EUV 光刻线空间图案校正:粗糙度和缺陷率研究,” 朱莉范贝尔等人。 发现将 DSA 与 EUV 相结合优于基于浸没式光刻的 DSA 工艺,具有较低的线宽粗糙度且无错位缺陷。

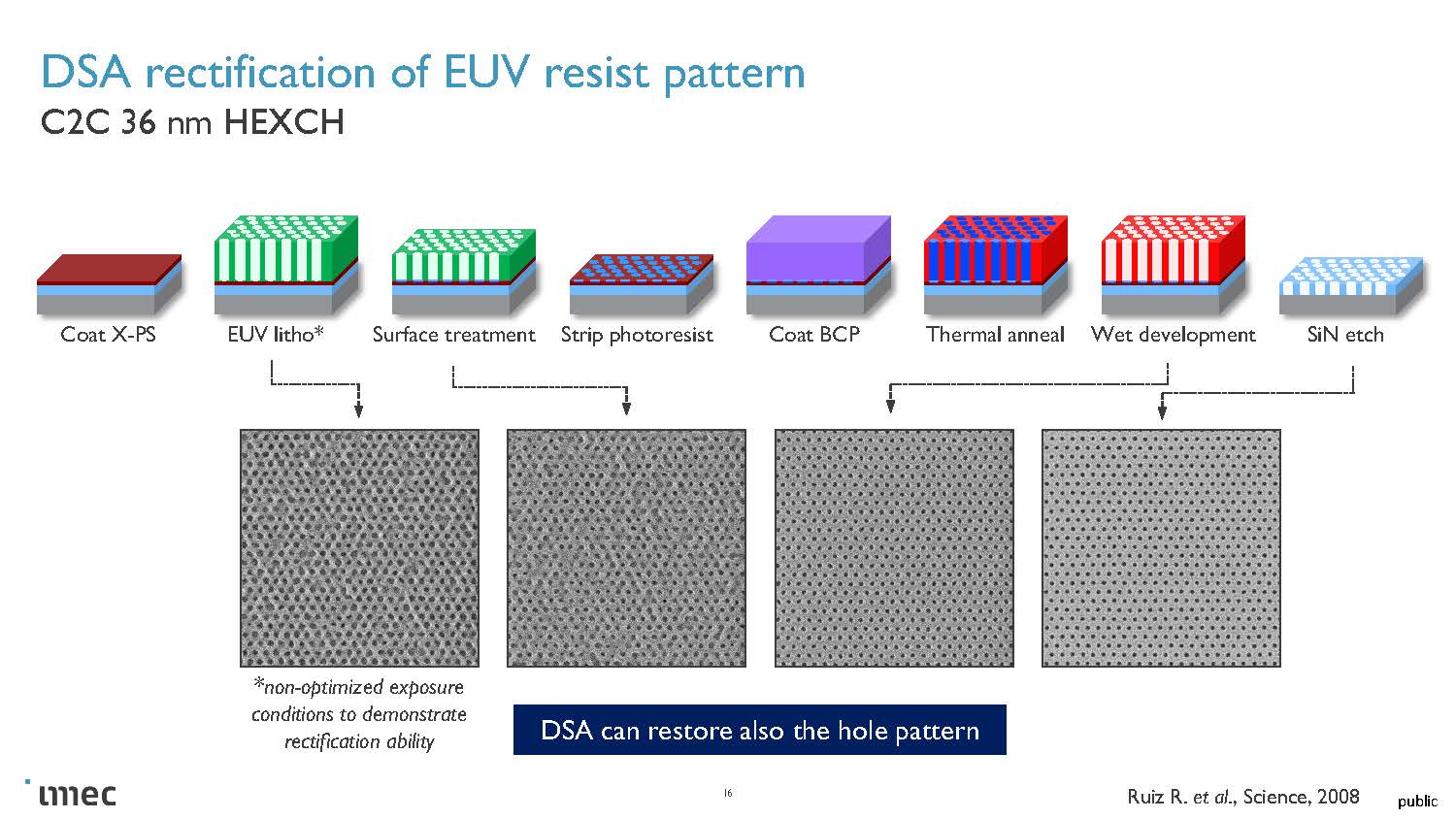

In “通过定向自组装减轻 EUV 光刻中的随机性,” Lander Verstraete 等人。 探索使用 DSA 来减轻 EUV 处理中的随机缺陷。

imec 纠正线/空间 EUV 缺陷的过程如图 3 所示。

图 4 说明了纠正接触阵列缺陷的 imec 过程。

EUV 加 DSA 对于 28nm 间距的线/空间看起来非常有前途,主要缺陷是桥接。 24nm 间距需要改进,桥接缺陷太多。 缺陷与嵌段共聚物配方和退火时间相关。

对于触点阵列,EUV + DSA 改善了局部临界尺寸均匀性 (LCDU) 和图案放置误差,并实现了较低的剂量。

度量衡学

随着薄膜厚度的减少,计量信噪比成为一个问题。

EUV 有一个缺陷工艺窗口,一侧有悬崖,图案断裂成为问题,而在窗口的另一侧有悬崖,图案之间的桥梁成为问题。

当尝试一个新的 pitch 时,随着时间的推移会出现很多缺陷。

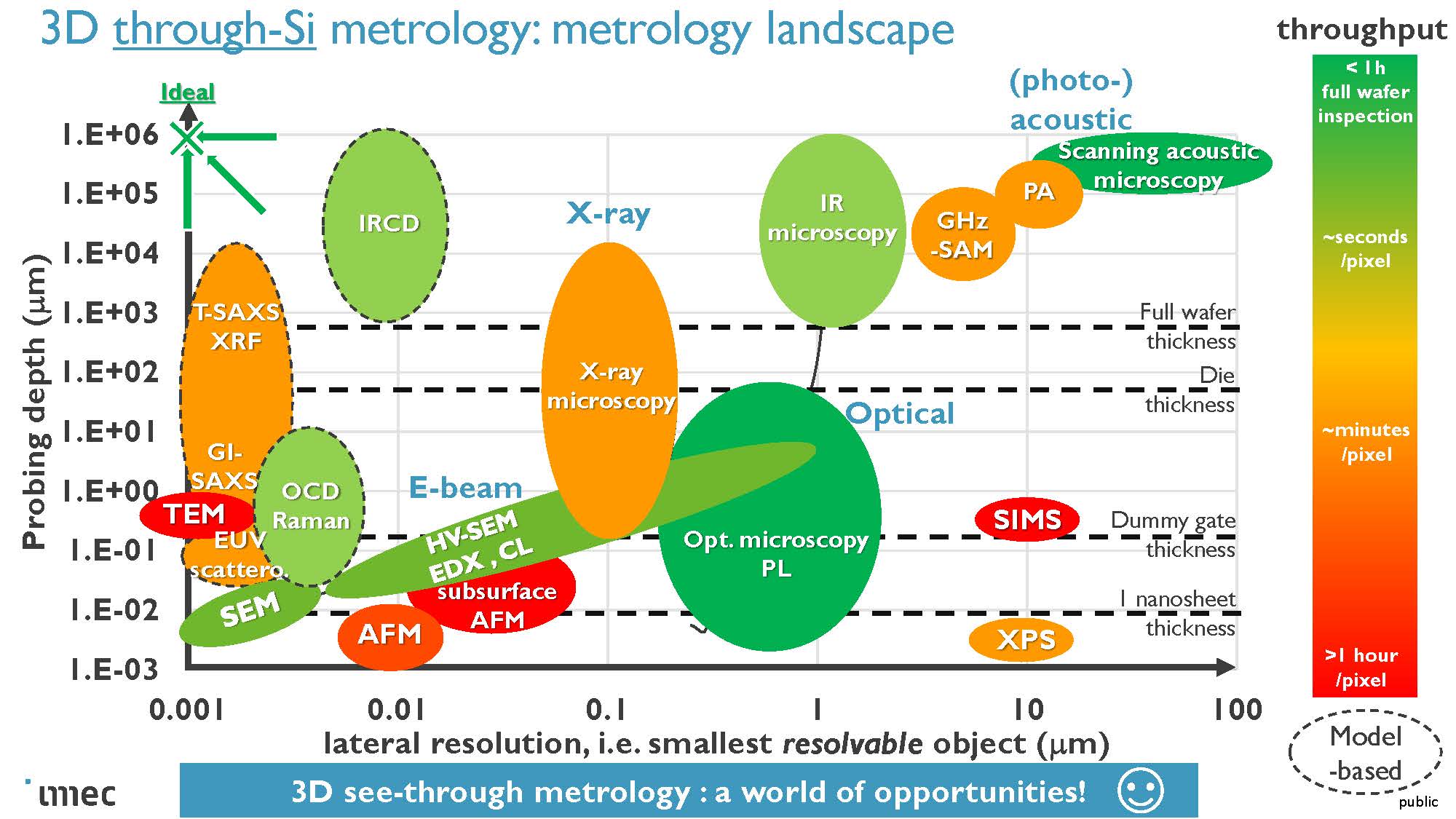

很难以足够的灵敏度测量足够大的区域。 电子束检测灵敏但慢,光学检测快但不灵敏。 像 CFET 这样的新 3D 工艺带来了额外的挑战。

In “高 NA EUVL 的干阻计量准备,” Gian Francesco Lorusso 等人研究了原子力显微镜 (AFM)、电子束检查和 CD SEM,以表征非常薄的光刻胶。

使用 Lam 干式光刻胶工艺< CD SEM 被证明对低至 5 纳米厚的光刻胶是可行的。 随着抗蚀剂厚度的降低,线条粗糙度的增加,桥接缺陷的可印刷性降低,而断裂缺陷保持不变。 图案坍塌仅见于较厚的薄膜。 AFM 测量表明薄膜厚度减少。 E Beam 显示出对缺陷的良好捕获,即使对于非常重要的薄膜也是如此。

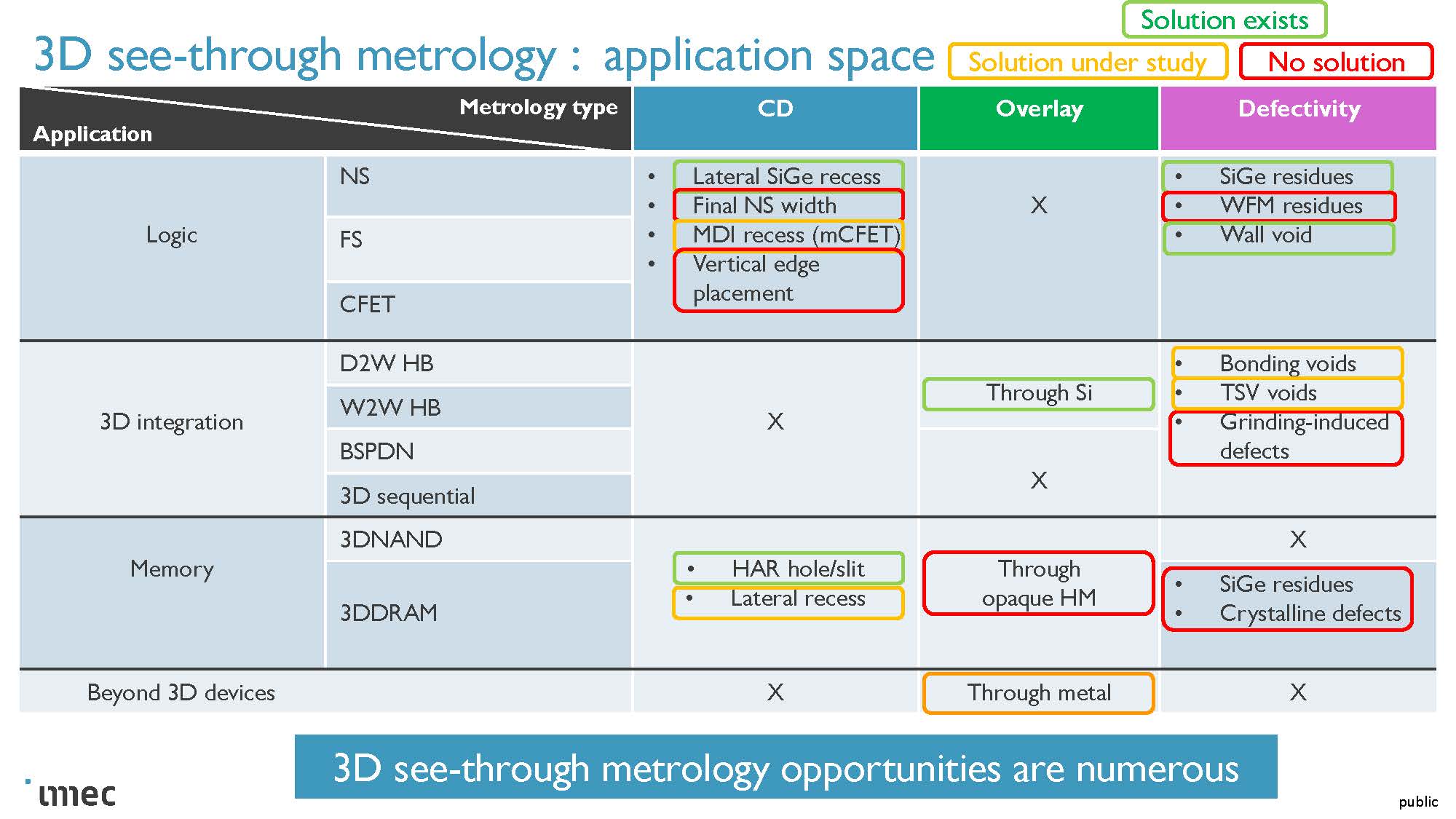

In “3D 时代的半导体计量学”, J. Bogdanowicz 等人,探讨了 3D 结构计量学的挑战。

在3D时代,Z方向成为了新的X/Y缩放。 对于逻辑器件,CFET 和 Semi damascene 提出了挑战,内存 3D DRAM 是未来的挑战,用于系统技术协同优化 (STCO) 的 3D 互连是另一个挑战。

对于水平纳米片和 CFET 工艺,横向凹陷和填充表征以及检测残留物和多层堆叠中的其他缺陷将是至关重要的。 在 3D 内存中,高纵横比 (HAR) 孔/分裂轮廓分析和类似于逻辑检测多层膜中的掩埋缺陷和残留物将是至关重要的。 对于 STCO 应用,粘合界面的完整性和对准将是关键。

对于传统的表面计量,灵敏度和速度之间已经存在权衡,现在检测深度与横向分辨率是一个关键的权衡。 图 5 显示了各种计量技术的探测深度与横向分辨率和吞吐量的关系。

图 6 总结了 3D 计量当前为满足各种需求所做的准备。

从图 6 可以看出,要实现全面的计量计划,仍有许多挑战需要克服。

结论

High NA EUV 时代即将来临。 在薄膜、光致抗蚀剂和计量学方面取得了良好进展,imec 继续在这三个领域努力取得进一步进展。

另请参阅:

2023 年 SPIE 高级光刻会议 – AMAT Sculpta® 公告

通过以下方式分享此帖子:

- SEO 支持的内容和 PR 分发。 今天得到放大。

- 柏拉图爱流。 Web3 数据智能。 知识放大。 访问这里。

- 与 Adryenn Ashley 一起铸造未来。 访问这里。

- 使用 PREIPO® 买卖 PRE-IPO 公司的股票。 访问这里。

- Sumber: https://semiwiki.com/lithography/329278-spie-2023-imec-preparing-for-high-na-euv/

- :具有

- :是

- :不是

- :在哪里

- $UP

- 000

- 1

- 2022

- 2023

- 2D

- 2D材料

- 30

- 3d

- a

- 实际

- 额外

- 地址

- 高级

- 先进的光刻

- AL

- 所有类型

- 已经

- 还

- 放大

- an

- 和

- 另一个

- 应用领域

- 接近

- 约

- 保健

- 国家 / 地区

- 地区

- 围绕

- AS

- 方面

- 组装

- At

- 尝试

- 关注我们

- 作者

- 烘烤

- 基于

- BE

- 光束

- 成为

- 很

- 作为

- 如下。

- 之间

- 阻止

- 蓝色

- 午休

- 休息

- 桥

- 桥梁

- 燃烧

- 但是

- by

- CAN

- 捕获

- 汽车

- 碳

- CD

- 挑战

- 挑战

- 挑战

- 更改

- CO

- 崩溃

- 结合

- 兼容

- 全面

- 总结

- 条件

- 研讨会 首页

- CONTACT

- 污染物

- 继续

- 对比

- 相关

- 课程

- 创建

- 危急

- 电流

- 曲线

- 减少

- 证明

- 密度

- 沉积

- 深度

- 描述

- 设计

- 研发支持

- 设备

- 死

- 尺寸

- 方向

- 讨论

- 错位

- 做

- 向下

- 驾驶

- 驱动

- 干

- 两

- e

- Ë&T

- 生态系统

- 影响

- enable

- 使

- 能源

- 增强

- 更多

- 时代

- 错误

- 评估

- 评估

- 评估

- 甚至

- 终于

- 展品

- 预期

- 探索

- 探讨

- 曝光

- 高效率

- 二月

- 部分

- 数字

- 填

- 电影

- 薄膜

- 专注焦点

- 针对

- 力

- 公式

- 发现

- 止

- 进一步

- 未来

- 越来越

- 非常好

- 绿色

- 民政事务总署

- 硬

- 有

- he

- 保持

- 高

- 更高

- 横

- 创新中心

- How To

- 但是

- HTTPS

- 加氢

- i

- 确定

- 说明

- 浸没

- 改善

- 改进

- 提高

- in

- 增加

- 增加

- 表示

- 基础设施

- 原来

- 诚信

- 英特尔

- 互连

- 接口

- 专属采访

- 推出

- 调查

- 问题

- 问题

- IT

- JPG

- 键

- 林

- 景观

- 大

- 层

- 层

- 铅

- 领导

- 各级

- 喜欢

- Line

- 清单

- 本地

- 逻辑

- 长

- 长时间

- 看

- 寻找

- LOOKS

- 离

- 占地

- 低

- 制成

- 制作

- 管理

- 制造业

- 许多

- 面膜

- 面膜

- 匹配

- 物料

- 最大宽度

- 可能..

- 衡量

- 测量

- 机械

- 内存

- 的话

- 某些金属

- 度量衡学

- 显微镜

- 减轻

- 钱

- 更多

- 许多

- 多

- 需求

- 打印车票

- 需要

- 全新

- 没有

- 噪声

- 现在

- 获得

- of

- 折扣

- 这一点在线下监测数字化产品的影响方面尤为明显。

- on

- 一

- 仅由

- ZAP优势

- 优化

- or

- 有机

- 其他名称

- 输出

- 超过

- 克服

- 文件

- 模式

- 模式

- 性能

- 透视

- 沥青

- 血浆

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 加

- 贫困

- 帖子

- 准备

- 案例分享

- 呈现

- 礼物

- 总统

- 小学

- 市场问题

- 过程

- 过程

- 处理

- 剖析

- 曲目

- 进展

- 有希望

- 成熟

- 提供

- 辐射

- 率

- 价格表

- 比

- 阅读

- 准备就绪

- 最近

- 最近

- 减少

- 减少

- 减少

- 减少

- 有关

- 保持

- 需要

- 分辨率

- 导致

- 成果

- 检讨

- 路线图

- 健壮

- 说

- 同

- 缩放

- 肖恩

- 看到

- 看到

- 选

- 自

- SEM

- 半

- 敏感

- 灵敏度

- 转移

- 显示

- 如图

- 侧

- 信号

- 类似

- 单

- 尺寸

- 雪道

- 放慢

- 小

- So

- 一些

- 来源

- 太空

- 速度

- 花费

- Spot

- 稳定性

- 稳定

- 稳定

- 堆栈

- Steve (史蒂夫)

- 仍

- 实力

- 非常

- 学习

- 主题

- 这样

- 足够

- 优于

- 磁化面

- 暂停

- 甜

- 系统

- 产品

- 会谈

- 技术

- 专业技术

- 比

- 这

- 该座

- 其

- 然后

- 那里。

- 博曼

- 他们

- 事

- Free Introduction

- 今年

- 那些

- 三

- 吞吐量

- 次

- 至

- 一起

- 也有

- 工具

- 工具

- 向

- 跟踪时

- 牵引

- 贸易

- 传统

- 二

- 类型

- 全功能包

- 下

- 直到

- 运用

- 利用

- 利用

- 各个

- 与

- 垂直

- 非常

- 通过

- 可行

- 副总裁

- 挥发物

- 是

- 井

- 去

- 什么是

- 而

- 将

- 窗户

- 工作

- 写

- 写作

- 年

- 您

- 和风网