近二十年来,S2C 一直是 FPGA 原型设计领域的全球领导者,其 FPGA 原型设计平台密切跟踪最新 FPGA 的可用性,包括 Xilinx 和 Intel 的最新 FPGA。 他们肯定兑现了推进超大规模设计原型的原型解决方案的承诺 - 扩大 原型平台容量和功能可支持数十亿门设计。

回顾 4 年第四季度初,S2020C 宣布支持当时全新的 Xilinx VU2P UltraScale+ FPGA,提供单路、双路和四路 FPGA 原型平台。 然后,在 19 年 2020 月,S2C 紧随其后,宣布推出其高密度 Prodigy Logic Matrix 系列原型设计平台,每个逻辑矩阵有 8 个 FPGA,每个服务器机架有 8 个逻辑矩阵(64 个 FPGA),并且可以连接多个服务器。服务器机架在一起。 逻辑矩阵的第一次迭代是通过 Xilinx VU440 FPGA(称为 LX1)给迫不及待想要 VU19P 版本(被称为 LX2).

现在,S2C 正在加强其逻辑矩阵游戏 LX2,其原型可用门容量比 VU60 版本提高了 440%! 每个 FPGA 更多的可用门意味着更少的 FPGA、更少的 FPGA 互连以及相同原型设计的更高性能。 预计登机口容量为 392 亿个登机口 LX2,一个完全填充的标准服务器机架,有 8 个 LX2的 估计可实现超过 3 亿个 ASIC 门的原型设计能力!

图 1:Prodigy Logic Matrix LX2

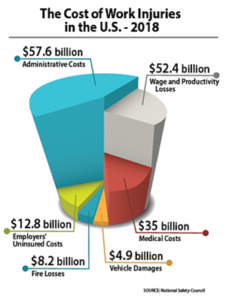

| Prodigy 逻辑矩阵系列 | ||

| LX1 | LX2 | |

| FPGA | XCVU440 | XCVU19P |

| 估计 ASIC 门数 (M) | 240 | 392 |

| FPGA数量 | 8 | 8 |

| 系统逻辑单元 (K) | 44,328 | 71,504 |

| FPGA 内存 (Mb) | 709 | 1,327.2 |

| DSP 切片 | 23,040 | 30,720 |

| 外部用户 I/O | 9,216 | 10,368 |

| 串行解串器收发器 | 第384章 | 640 GTY |

| 神童连接器 | 64 | 72 |

| PGT 连接器 | 8 | 0 |

| 收发器连接器 | 80 个 MSAS,每个 MSAS 带有 4 个 GTH + 8 个 IO | 160 个 MCIO,每个 4 个 GTY + 8 个 IO |

| 串行解串器性能 | 16 Gbps | 28 Gbps |

数字 2:逻辑矩阵系列

灵活、高速互连是高密度 FPGA 原型设计的关键,Logic Matrix 支持分层、三级互连策略: 短桥 用于相邻 FPGA 之间的互连; 系统链接 用于高带宽 FPGA 电缆互连,以及 TransLink的 通过 MCIO 电缆实现更长距离的 FPGA SerDes 互连。 简化FPGA互连并最大化价值 TransLink的,S2C 的分区流程支持 Xilinx 新推出的高速收发器引脚复用 (HSTPM),从而简化了周期精确的信号传输、引脚复用和低延迟 SerDes FPGA 连接。

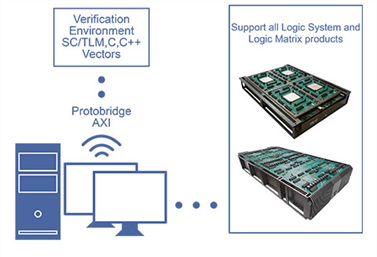

为了最大限度地缩短原型设计时间并最大化原型设计生产力,S2C 的其他原型设计生产力工具在设计时考虑了 Logic Matrix,包括 Player Pro 运行时 软件 – 以及附加 S2C 原型设计工具,包括 原型桥, MDM 专业版和 S2C 的 原型就绪 IP.

Player Pro 运行时 软件包含在 LX2,提供先进的时钟管理、集成自测试、自动板检测、I/O 电压编程、多个 FPGA 下载以及远程系统监控和管理等便捷功能。 还包括 AXEVision,这是一款内置 AXI-over-Ethernet 调试工具,可简化 AXI 相关设计的远程调试。

原型桥 支持主机和计算机之间的高吞吐量数据传输(高达 1GB/s) LX2 – 能够传输大量软件建模事务、视频流或其他测试刺激以进行系统验证。

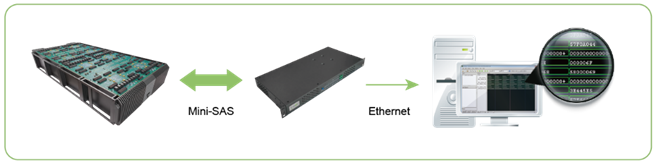

图 3:ProtoBridge

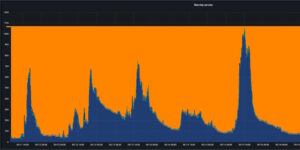

MDM 专业版 具有针对多达 64 个 FPGA 的交叉触发器的深度跟踪调试功能、从单个查看窗口查看多 FPGA 信号跟踪、125GB 外部跟踪波形存储、高达 XNUMXMHz 的跟踪采样率,并支持用于复杂跟踪捕获的触发状态机语言要求。

图 4:MDM Pro

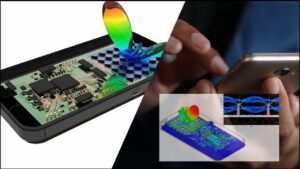

S2C 还提供丰富的库 原型就绪 IP 等加工。为 LX2 – 即插即用子卡 – 加速围绕 FPGA 原型创建原型环境。

图 5:原型就绪 IP 子卡

神童逻辑矩阵 LX2 现在可用。 如需了解更多信息,请联系您当地的 S2C 销售代表,或访问 www.s2ceda.com.

通过以下方式分享此帖子: 来源:https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/