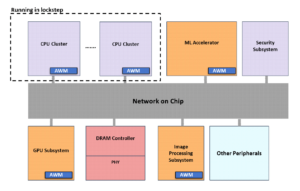

在讨论大型 SOC 的 MBIST 时,“治愈比疾病更糟糕”这句老话是恰当的,在这些 SOC 中,并行运行许多 MBIST 测试可能会超出配电网络 (PDN) 的能力。 内存内置自检 (MBIST) 通常会在开机事件期间自动运行。 由于希望加快测试和芯片启动时间,这些测试经常并行运行。 问题是它们很容易产生比常规芯片操作期间发现的水平高出一个数量级的开关活动。 事实上,这些较高的开关活动水平不仅会导致影响测试结果的电源下降,而且产生的高热量也会损坏芯片。 这些影响会导致不正确的装箱或事件直接和潜在故障。

解决方案是模拟 MBIST 活动以预测 PDN 上的负载和相关的热效应。 通过手头的仿真结果,设计人员可以正确地决定可以并行测试多少个以及哪些内存块。 然而,这在具有许多内存块的大型 SOC 中并不总是可行,因为仿真时间可能过长。 使用门级和更不准确的 RTL 仿真,可能无法运行足够的周期来获取所需的信息。

在题为“分析 MBIST 使用的功率影响”的白皮书中,西门子 EDA 研究了设计人员如何运行充分的仿真,以便在流片前就测试策略做出明智的决策。 西门子与 ARM 合作开发了他们的一款测试芯片,以创建一个测试用例,在该用例中,他们可以通过 DFT 和 Power 应用程序为西门子硬件仿真器 Veloce 应用硬件仿真。 首先,Veloce DFT 应用程序用于输出 MBIST 仿真期间的内部活动。 该应用程序使用标准测试接口语言 (STIL) 并生成行业标准输出文件。

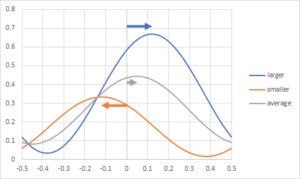

Veloce Power 应用程序从 MBIST 运行中获取活动信息以生成波形、功率曲线和热图,这些可以指示功率峰值何时超过指定限制。 有了这些信息,测试工程师可以就 MBIST 的排序做出明智的决定。

西门子白皮书中描述的 ARM 测试用例包含 176 亿个门。 西门子为此测试用例使用了带有 6 个 Veloce Strato 板的 Veloce 系统。 Veloce 仿真器运行仅需 26 小时,比门级仿真快 15,600 倍。 Veloce 流程的另一个好处是活动信息由 Power 应用流式传输到流程中的电动工具,从而节省磁盘空间和时间。 测试用例的结果显示了几个违反 SOC 设计规范的功率尖峰。 Veloce Power 应用程序的输出显示了通过仿真的总功率水平以及时钟、组合逻辑和存储器的单独功率贡献。 同样,还有关于管芯上何处使用电源的信息。 此信息使确定问题所在变得容易。

发现此类问题需要运行数百万或数十亿个时钟周期。 软件模拟器的局限性使其无法执行必要的分析。 仿真提供了一种独特的途径,可以在硅之前很久就仔细检查 MBIST 和其他测试操作的功率影响。 西门子白皮书提供了对实际测试用例中使用的功率方法的深入了解。 白皮书可在西门子网站上下载阅读。

通过以下方式分享此帖子: 资料来源:https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/