自 1980 世纪 10 年代首次通过同轴电缆提供 1.6Mbps 共享 LAN 以来,以太网不断取得进步,现在有可能支持高达 500Tbps 的速度。 这一进展使以太网能够服务于更广泛的应用,例如直播、无线接入网络和工业控制,强调了可靠的数据包传输和服务质量的重要性。 当前互联网带宽达到约 802.3 Tbps,对改进后端数据中心内部流量处理的需求不断增长。 尽管单个服务器尚未达到每秒太比特的水平,但数据中心的总体流量已接近这一规模,促使 IEEE XNUMXdj 小组开展标准化工作,并需要强大的以太网控制器和 SerDes 来管理不断扩展的数据流。 在需求不断升级的背景下,处理器间通信已经达到了这样的速度。

处理器间通信引领了对 1.6T 速率和最小延迟的需求。 虽然单个设备受到其固有处理能力和芯片尺寸的限制,但组合芯片可以显着扩展这些能力。 第一代应用程序预计将出现数据中心内交换机到交换机连接,从而实现高性能处理器和内存的池化,从而提高云计算内的可扩展性和效率。

IEEE 802.3dj 计划:推进以太网标准以实现 1.6 Tbps 互操作性

遵守不断发展的标准化工作对于生态系统无缝互操作性至关重要。 IEEE 802.3dj 小组正在制定即将推出的以太网标准,其中包括物理层和管理参数,速度从 200G 到每秒 1.6 太比特。 该小组的目标是实现 1.6 Tbps 以太网 MAC 数据速率,目标是 MAC 层的最大误码率不超过 10-13。 进一步的规定包括适合不同芯片应用的可选 16 和 8 通道附件单元接口 (AUI),利用 112G 和 224G SerDes。 从物理上讲,1.6Tbps 规范需要通过 8 对铜质双芯电缆进行传输,传输距离可达 8 米,并通过 500 对光纤进行传输,传输距离可达 2 米至 2026 公里。 尽管该标准预计将于 2024 年春季获得完全批准,但核心功能集预计将于 XNUMX 年完成。

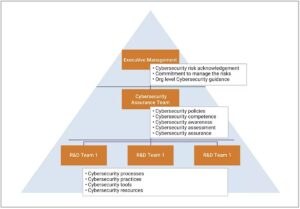

1.6T 以太网子系统中的带宽开销和纠错

图 1:描述 1.6T 以太网子系统组件的图表。

在早期的以太网迭代中,PCS 主要关注数据编码以实现可靠的数据包检测。 然而,随着以太网速度升级至 1.6T,前向纠错 (FEC) 的需求变得明显,特别是为了抵消短链路上的信号衰减。 为此,1.6T 以太网继续采用 Reed-Solomon FEC。 此方法构建的码字包含 514 个 10 位符号,编码为 544 个符号块,导致 6% 的带宽开销。 这些 FEC 码字分布在 AUI 物理链路上,因此每个物理链路(8T 以太网有 1.6 个)不会携带整个码字。 该方法不仅提供了针对突发错误的额外保护,而且还能够在远端解码器处实现并行化,从而减少延迟。

物理介质附件 (PMA) 具有齿轮箱和 SerDes,可将以太网信号传送到传输通道上。 对于 1.6T 以太网,这涉及 8 个通道,每个通道以 212Gbps 运行,占 6% 的 FEC 开销。 采用的调制技术是四级脉冲幅度调制 (PAM-4),它为每个传输符号编码两个数据位,与传统的不归零 (NRZ) 方法并列时,可以有效地使带宽加倍。 传输机制依赖于数模转换,而在接收端,模数转换结合DSP确保了准确的信号提取。

此外,值得注意的是,以太网 PCS 引入了跨越以太网链路端到端的“外部 FEC”。 为了支持更长距离的信道,正在为各个物理线路添加一层纠错层,可能会采用汉明码 FEC。 预计这种校正将在光收发器模块中找到其主要应用,在光收发器模块中这种校正是必要的。

图 2:图表显示了使用级联 FEC 来扩展覆盖范围时增加的额外开销。

在图 2 所示的示例系统中,MAC 和 PCS 通过光学模块和光纤延伸连接。 PCS的误码率为10-5 在光模块链路上,加上光链路本身的错误。 使用单独的 RS-FEC 端到端不足以实现 10-13 以太网标准,导致链路不可靠。 一种选择是在每一跳上三次实施单独的 RS FEC,这会显着增加成本和延迟。 更有效的解决方案是集成专门针对光链路的级联汉明码FEC,以解决光连接的典型随机错误。 该内部 FEC 层将线路速率从 212 Gbps 额外扩展至 226 Gbps,因此 SerDes 必须支持该线路速率。

1.6T 以太网系统中的延迟挑战

图 3:1.6T 以太网子系统的延迟路径。

各种组件都会导致以太网延迟:传输队列、传输持续时间、介质遍历时间以及多个处理和接收时间。 为了形象化这一点,请考虑图 3,它显示了一个综合的 1.6T 以太网子系统。 虽然延迟可能受到远端应用程序反应时间的影响,但该因素是以太网外部的,因此在延迟分析期间通常会被排除。 最大限度地减少以太网接口的延迟需要了解具体情况。 例如,由于较慢的客户端链路上固有的延迟,延迟可能不是交换机之间的中继连接的主要问题。 距离也有影响; 更长的长度会带来更多的延迟。 当然,这并不意味着我们应该忽视其他场景下的延迟,减少延迟始终是一个目标。

传输延迟本质上与以太网速率和帧大小相关。 具体来说,对于 1.6T 以太网系统,传输最小尺寸的数据包需要 0.4ns,本质上是 2.5 GHz 时钟的每个滴答周期传输一个以太网帧。 另一方面,传输标准最大尺寸帧需要 8 纳秒,对于巨型帧则延长至 48 纳秒。 所选择的介质进一步决定了延迟。 例如,光纤通常会产生每米 5 纳秒的延迟,而铜缆的延迟速度稍快一些,为每米 4 纳秒。

整体延迟的很大一部分源于接收器控制器。 RS FEC 解码器本质上会引入延迟。 为了启动纠错,系统必须接收 4 个码字,在 1.6Tbps 下,相当于 12.8ns。 后续活动(包括纠错和缓冲)会放大此延迟。 虽然 FEC 码字存储持续时间保持一致,但消息接收期间的延迟取决于具体实现。 尽管如此,可以通过采用细致的数字设计策略来优化延迟。

本质上,由于 FEC 机制和物理距离或电缆长度,存在固有的、不可避免的延迟。 除了这些因素之外,设计专业知识对于最大限度地减少以太网控制器延迟也发挥着关键作用。 利用集成和优化 MAC、PCS 和 PHY 的完整解决方案,为最高效、低延迟的实施铺平道路。

总结

图 4:Synopsys 224G 以太网 PHY IP 在 3nm 工艺中的首次硅片成功,展示了高度线性的 PAM-4 眼图。

1.6 Tbps 以太网专为带宽要求最高和延迟敏感的应用程序而定制。 随着 224G SerDes 技术的出现,再加上 MAC 和 PCS IP 的进步,现在可以提供持续符合不断发展的 1.6T 以太网标准的全面解决方案。 此外,由于协议和纠错方法固有的延迟,IP 数字和模拟设计必须由专家设计人员精心设计,以避免在数据路径中引入不必要的延迟。

要实现 1.6T SoC 设计的顶级性能,需要对每个芯片组件进行高效优化的架构和细致的设计实践。 这强调了节能并最大限度地减少了芯片占用空间,使 1.6T 数据速率成为现实。 经过硅验证的 Synopsys 224G 以太网 PHY IP 为 1.6T MAC 和 PCS 控制器奠定了基础。 Synopsys 利用领先的设计、分析、仿真和测量技术,持续提供卓越的信号完整性和抖动性能, 完整的以太网解决方案,包括 MAC+PCS+PHY.

- :具有

- :是

- :不是

- :在哪里

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- ACCESS

- 无障碍

- 基本会计和财务报表

- 精准的

- 横过

- 活动

- 添加

- 额外

- 另外

- 采用

- 进步

- 前进

- 驳

- 致力

- 允许

- 已经

- 还

- 尽管

- 时刻

- 烟雨

- 量

- 放大

- an

- 分析

- 和

- 预期

- 应用领域

- 应用领域

- 的途径

- 架构

- 保健

- AS

- At

- 避免

- 后端

- 背景

- 带宽

- BE

- 成为

- 之间

- 超越

- 位

- 阻止

- 加强

- 提高

- 带来

- 建立

- 但是

- by

- 电缆

- 电缆

- CAN

- 能力

- 携带

- 挑战

- 通道

- 芯片

- 碎屑

- 选择

- 情况

- 客户

- 时钟

- 云端技术

- 云计算

- 码

- 结合

- 结合

- 沟通

- 完成

- 完成

- 元件

- 组件

- 全面

- 包括

- 计算

- 关心

- 结合

- 已联繫

- 连接

- 保护

- 考虑

- 注意事项

- 一贯

- 继续

- 一直

- 贡献

- 控制

- 调节器

- 转化

- 铜

- 核心

- 成本

- 抵消

- 课程

- 精雕细琢

- 创建

- 电流

- data

- 数据中心

- 首次亮相

- 延误

- 交付

- 需求

- 严格

- 需求

- 描绘

- 设计

- 设计师

- 设计

- 检测

- 设备

- 使然

- 不同

- 数字

- 用心

- 显示器

- 距离

- 分布

- 不会

- 加倍

- 两

- 为期

- ,我们将参加

- 每

- 此前

- 生态系统

- 有效

- 只

- 效率

- 高效

- 有效

- 工作的影响。

- 出现

- 强调

- 强调

- 就业

- 雇用

- 使

- 使

- 包含

- 结束

- 端至端

- 确保

- 整个

- 错误

- 故障

- 升级

- 本质

- 必要

- 本质上

- 醚(ETH)

- 甚至

- 所有的

- 明显

- 演变

- 例子

- 特殊

- 排除

- 扩大

- 扩张

- 预期

- 技术专家

- 专门知识

- 延长

- 延长

- 外部

- 萃取

- 眼部彩妆

- 因素

- 因素

- 远

- 快

- 特征

- 特色

- 数字

- 找到最适合您的地方

- (名字)

- 第一代

- 流

- 重点

- 其次

- Footprint

- 针对

- 制定

- 向前

- FRAME

- 止

- 进一步

- 代

- 给

- 更大的

- 团队

- 组的

- 成长

- 手

- 处理

- 高

- 高性能

- 高度

- 但是

- HTML

- HTTPS

- 势在必行

- 履行

- 重要性

- 重要

- 改善

- in

- 其他

- 包括

- 包含

- 增加

- 个人

- 产业

- 影响

- 固有

- 本质

- 开始

- 倡议

- 例

- 集成

- 积分

- 诚信

- 接口

- 接口

- 网络

- 互操作性

- 成

- 固有

- 介绍

- 推出

- 介绍

- 涉及

- IP

- IT

- 迭代

- 它的

- 本身

- JPG

- 车道

- 潜伏

- 层

- 层

- 长度

- 各级

- 借力

- 容易

- Line

- 线

- 友情链接

- 链接

- 生活

- 不再

- 低

- MAC

- 制作

- 管理

- 颠覆性技术

- 最大宽度

- 最多

- 可能..

- 意味着

- 数据监测

- 机制

- 中等

- 内存

- 的话

- 方法

- 方法

- 细致

- 最小

- 大幅减低

- 最小化

- 最小化

- 模块

- 模块

- 更多

- 最先进的

- 必须

- 接近

- 需求

- 网络

- 虽然

- 没有

- 注意

- 现在

- 目标

- of

- 经常

- on

- 一

- 仅由

- 操作

- 优化

- 优化

- 附加选项

- or

- 其他名称

- 超过

- 最划算

- 对

- 参数

- 尤其

- 径

- 个人电脑

- 为

- 性能

- 表演

- 的

- 物理

- 管道

- 关键的

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 扮演

- 加

- 潜力

- 功率

- 做法

- 主要

- 小学

- 过程

- 处理

- 处理器

- 级数

- 预计

- 保护

- 协议

- 脉冲

- 目的

- 推动

- 质量

- 广播电台

- 随机

- 范围

- 率

- 价格表

- 达到

- 达

- 反应

- 现实

- 接收

- 接收

- 招待会

- 减少

- 可靠

- 遗迹

- 翻译

- 需要

- 受限

- 导致

- 健壮

- 角色

- 根

- 运行

- 可扩展性

- 鳞片

- 情景

- 无缝的

- 其次

- 看到

- 段

- 敏感

- 分开

- 服务

- 服务

- 集

- 几个

- 共用的,

- 短

- 应该

- 陈列宣传

- 信号

- 显著

- 硅

- 模拟

- 尺寸

- So

- 方案,

- 解决方案

- 跨度

- 逍遥丸

- 具体的

- 特别是

- 规范

- 速度

- 弹簧

- 阶段

- 标准

- 标准化

- 标准

- 存储

- 策略

- 流

- 随后

- 大量

- 成功

- 这样

- 合适的

- SUPPORT

- 符号

- 系统

- 量身定制

- 需要

- 技术

- 技术

- 专业技术

- 比

- 这

- 其

- 那里。

- 从而

- 因此

- 博曼

- Free Introduction

- 通过

- 从而

- 蜱

- 绑

- 次

- 时

- 至

- 最佳

- 传统

- 交通

- 转让

- 发送

- 三倍

- 二

- 普遍

- 一般

- 不可避免的

- 理解

- 承担

- 单元

- 即将上市

- 上

- 运用

- 利用

- 通过

- 想像

- 方法..

- we

- ,尤其是

- 这

- 而

- 更宽

- 中

- 将

- 但

- 和风网

- 零