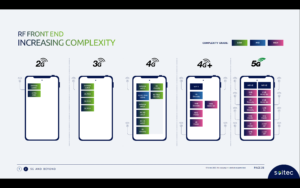

在向能力更强、速度更快、体积更小、功耗更低的系统迈进的过程中,摩尔定律在大约 30 多年的时间里让软件在纯粹的半导体工艺演进中搭便车。计算硬件每年都提供改进的性能/面积/功耗指标,从而允许软件增加复杂性并提供更多功能,而没有任何缺点。然后,轻松的胜利就变得不那么容易了。更先进的工艺继续提供更高的单位面积门数,但性能和功耗的提升开始趋于平缓。由于我们对创新的期望并未停止,因此硬件架构的进步对于弥补这一不足变得更加重要。

增加核心数量的驱动因素

这个方向的早期步骤是使用多核 CPU 通过对跨核心的并发任务进行线程化或虚拟化来加速总吞吐量,并根据需要通过闲置或关闭不活动核心来降低功耗。多核现已成为标准,多核(甚至芯片上有更多 CPU)的趋势在 AWS、Azure、阿里巴巴等云平台中提供的服务器实例选项中已经很明显。

多核/众核架构向前迈出了一步,但由于阿姆达尔定律,CPU 集群的并行性是粗粒度的,并且有其自身的性能和功耗限制。架构变得更加异构,添加了用于图像、音频和其他特殊需求的加速器。人工智能加速器还推动了细粒度并行性,转向脉动阵列和其他特定领域的技术。这种情况一直运行得很好,直到 ChatGPT 出现(拥有 175 亿个参数),GPT-3 演变成拥有 4 万亿个参数的 GPT-100(比当今的 AI 系统复杂几个数量级),迫使 AI 加速器中需要更专业的加速功能。

另一方面,汽车应用中的多传感器系统现在正在集成到单个 SoC 中,以提高环境意识和改进 PPA。在这里,汽车自动化的新水平取决于在单个设备中融合来自多个传感器类型的输入,在子系统中复制 2 倍、4 倍或 8 倍。

Michał Siwinski(Arteris 首席营销官)表示,与多个设计团队在广泛的应用中进行的一个多月的讨论表明,这些团队正在积极转向更高的核心数量,以满足功能、性能和功耗目标。他告诉我,他们也看到这种趋势正在加速。工艺进步仍然有助于增加 SoC 门数,但满足性能和功耗目标的责任现在牢牢掌握在架构师手中。

更多核心,更多互连

芯片上的内核越多意味着这些内核之间的数据连接就越多。在相邻处理元件之间的加速器内,到本地缓存,到稀疏矩阵和其他专门处理的加速器。在加速器块和系统级总线之间添加分层连接。添加用于片上权重存储、解压缩、广播、收集和重新压缩的连接。添加工作缓存的 HBM 连接。如果需要,添加融合引擎。

基于 CPU 的控制集群必须连接到每个复制子系统以及所有常用功能 - 编解码器、内存管理、安全岛和信任根(如果适用)、UCIe(如果是多芯片实现)、PCIe(用于高带宽 I/O) ,以及用于联网的以太网或光纤。

这是大量的互连,对产品的适销性产生直接影响。在 16nm 以下的工艺中,NoC 基础设施目前占面积的 10-12%。更重要的是,作为内核之间的通信高速公路,它可以对性能和功耗产生重大影响。真正的危险是,次优的实现会浪费预期的架构性能和功率增益,或者更糟糕的是,导致大量的重新设计循环收敛。然而,在复杂的 SoC 布局规划中找到良好的实现仍然取决于在已经很紧张的设计进度中缓慢的试错优化。我们需要转向物理感知 NoC 设计,以保证复杂 NoC 层次结构的全面性能和功率支持,并且我们需要更快地进行这些优化。

物理感知 NoC 设计使摩尔定律保持在正轨上

摩尔定律可能还没有消亡,但当今性能和功耗的进步来自架构和 NoC 互连,而不是来自工艺。架构正在推动更多的加速器核心、加速器内的更多加速器以及更多的片上子系统复制。所有这些都增加了片上互连的复杂性。随着设计增加内核数量并转向 16 纳米及以下的工艺几何结构,跨越 SoC 及其子系统的众多 NoC 互连只有通过物理感知网络针对物理和时序限制进行最佳实施,才能支持这些复杂设计的全部潜力关于芯片设计。

如果您也担心这些趋势,您可能需要了解有关 Arteris FlexNoC 5 IP 技术的更多信息 点击这里.

通过以下方式分享此帖子:

- SEO 支持的内容和 PR 分发。 今天得到放大。

- 柏拉图区块链。 Web3 元宇宙智能。 知识放大。 访问这里。

- Sumber: https://semiwiki.com/artificial-intelligence/326727-interconnect-under-the-spotlight-as-core-counts-accelerate/

- :是

- $UP

- 100

- a

- 关于

- 加快

- 加速

- 促进

- 加速器

- 加速器

- 横过

- 积极地

- 高级

- 进步

- 驳

- AI

- 人工智能系统

- 阿里巴巴

- 所有类型

- 允许

- 已经

- 和

- 出现

- 应用领域

- 适当

- 架构

- 保健

- 国家 / 地区

- AS

- At

- 音频

- 汽车

- 可使用

- 意识

- AWS

- Azure

- 带宽

- BE

- 成为

- 如下。

- 之间

- 亿

- 播放

- 公共汽车

- by

- 缓存

- CAN

- 能力

- ChatGPT

- 芯片

- 云端技术

- 簇

- 奇美

- 如何

- 沟通

- 复杂

- 复杂

- 计算

- 并发

- 分享链接

- 连接

- 连接方式

- 后果

- 约束

- 持续

- 控制

- 汇集

- 核心

- 中央处理器

- 危险

- data

- 死

- 交付

- 提升

- 依靠

- 设计

- 设计

- 设备

- 不同

- 直接

- 方向

- 讨论

- 向下

- 缺点

- 每

- 早

- 分子

- 发动机

- 环境

- 甚至

- 所有的

- 进化

- 演变

- 扩大

- 期望

- 预期

- 快

- 特征

- 寻找

- 牢牢

- 针对

- 向前

- Free

- 止

- 前

- ,

- 功能

- 聚变

- 收益

- 理想中

- 非常好

- 保证

- 处理

- 手

- 硬件

- 有

- 帮助

- 此处

- 高

- 更高

- 高速公路

- HTTPS

- 图片

- 影响力故事

- 履行

- 实施

- 重要

- 改善

- in

- 不活跃

- 增加

- 增加

- 基础设施

- 創新

- 例

- 整合

- IP

- 岛

- IT

- 它的

- 跳

- 法律

- 学习用品

- Level

- 各级

- 范围

- 本地

- 占地

- 使

- 颠覆性技术

- 三月

- 矩阵

- 最大宽度

- 满足

- 会议

- 内存

- 指标

- 可能

- 月

- 更多

- 移动

- 移动

- 多

- 需求

- 打印车票

- 需要

- 网络

- 工业网络

- 全新

- 众多

- of

- on

- 附加选项

- 订单

- 其他名称

- 其它

- 己

- 参数

- 性能

- 的

- 物理

- 平台

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 帖子

- 潜力

- 功率

- 供电

- 漂亮

- 过程

- 过程

- 处理

- 产品

- 纯粹

- 推动

- 范围

- 宁

- 真实

- 减少

- 复制

- 复制

- 责任

- 导致

- 骑

- 根

- 实现安全

- 半导体

- 显著

- 自

- 单

- 松弛

- 放慢

- 小

- So

- 软件

- 稀疏矩阵

- 专门

- 聚焦

- 标准

- 开始

- 步

- 仍

- Stop 停止

- 存储

- 提示

- SUPPORT

- 系统

- 产品

- 任务

- 队

- 技术

- 专业技术

- 告诉

- 这

- 博曼

- 通过

- 吞吐量

- 定时

- 至

- 今晚

- 今天的

- 合计

- 趋势

- 趋势

- 兆

- 信任

- 谈到

- 类型

- 下

- 单元

- 通过

- 重量

- 井

- 这

- 宽

- 大范围

- 将

- 胜利

- 中

- 加工

- 年

- 年

- 和风网