模糊测试之于软件验证就像随机化之于硬件验证一样。模糊测试方法可以改进硬件安全测试吗? Paul Cunningham(Cadence 验证总经理)、Raúl Camposano(Silicon Catalyst、企业家、前 Synopsys 首席技术官)和我继续我们的研究想法系列。一如既往,欢迎反馈。

创新

本月的选择是 用于 SoC 安全验证的 HyperFuzzing。作者在 ICCAD 2020 上发表了这篇论文。他们来自印度理工学院坎普尔分校。

这是一种有趣的模糊测试方法,专门适用于现代 SoC 设计。它建立在 超级财产 检查动态模拟。这些超属性可以解释行为 痕迹组,一种非常适合安全检查的方法。作者提供了信息流检查(例如,特权数据不能从 A 泄漏到 B)和非干扰检查(对抗性行为不得干扰计算流)作为示例。然后通过比较有篡改和没有篡改的模拟跟踪束来检查安全性。

这种方法的篡改可以对不可信来源的不同类型的漏洞进行建模。通过随机化固件指令,将指令从组件写入 NoC,或在存储器中进行位翻转。作者还提出了几种新颖的覆盖率指标。这些旨在指导迭代,以围绕受先前篡改运行影响最大的情况进行篡改。

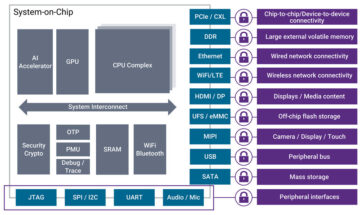

他们的测试用例是一个虽小但具有代表性的 SoC(详细信息参见 GitHub上)针对加密块运行固件测试,检查无干扰和其他漏洞。它们还通过数据块检查运行安全启动。他们在加密块中发现了多个安全违规行为,但包含 ECC 保护的块除外。

保罗的观点

安全验证是一个非常重要的话题,学术界和工业界都在进行大量工作。本文很好地将基于随机突变的覆盖范围与模拟跟踪集的“超属性”结合在一起,以创建一个创新的解决方案,该解决方案既可扩展又可有效地展示安全缺陷。

某些安全属性只能通过一组模拟跟踪来正式定义。例如,“不干扰”意味着攻击者不能干扰设计中某些受保护的计算。为了演示干扰,您需要比较两条迹线,除了一条迹线中存在一些攻击者操作之外,这两条迹线的输入刺激相同。如果受攻击轨迹中的任何受保护计算与黄金轨迹中的计算不同,则存在干扰。

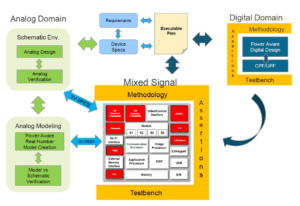

作者为多个跟踪上的断言创建了自己特殊风格的语言,并使用它来制定无干扰和保密性的安全属性。他们构建了一个自定义流程来随机篡改模拟,并检查被篡改和未篡改模拟之间的安全属性。他们的随机篡改算法还具有优雅的基于覆盖范围的学习启发式方法,可以指导其更有效地发现安全缺陷。

对多个模拟进行断言的想法非常强大。我想知道是否可以干净地扩展 SystemVerilog 以支持此类断言。这可能为商业模拟和正式工具的一些引人注目的本机扩展打开大门。另一种可能性可能是扩展新的便携式刺激标准(PSS)以包含跨多个生成的测试的断言。

尽管我确实希望获得有关结果的更多详细信息,但这篇论文读起来既轻松又愉快。作者声称他们的解决方案在开源 SoC 测试用例中发现了安全漏洞,但没有详细说明这些漏洞是什么,也没有详细说明他们的方法与文献中可用于查找相同漏洞的其他方法相比如何。

劳尔的观点

我将首先从技术成熟度的角度来看待这个问题。总的来说,我喜欢这个想法,这是一种非常有趣的设计安全性分级方法。也就是说,每种设计都要求设计人员以新颖的断言语言提供种子测试、篡改和安全规范。对我来说,目前这种方法牢牢地限制在学术领域。非常适合论文和论文,但还没有接近可以跳转到商业应用的东西。

我将戴上我的投资者帽子迎接第二个挑战。毫无疑问,安全是一个重要的话题。但除了我们已经知道的一些领域之外——例如航空航天、国防、支付系统和处理器/服务器。对于大多数原始设备制造商和零部件制造商来说,这仍然不是一个生存问题。如果普遍预期的话,他们愿意勾选一个复选框。但前提是对成本或上市时间的影响很小。因为他们的客户通常不会为安全支付更多费用。这使得大多数市场的安全性仍然依赖于交钥匙 IP,例如硬件信任根和易于使用的应用程序。以这些方式之一打包的解决方案将是可投资的,否则就不那么值得投资了。

我的观点

保罗和劳尔涵盖了我可能建议的大部分内容。我喜欢 Paul 扩展 SVA 的想法,至少是为了鼓励超性能实验。这必须开启一类新的有趣的测试,最终导致新的捆绑验证方法。

通过以下方式分享此帖子: 来源:https://semiwiki.com/eda/299391-fuzzing-to-validate-soc-security-innovation-in-verification/