隆德大学的研究人员发表了一篇题为“用于内存计算加速器的铁电隧道结忆阻器”的技术论文。

摘要:

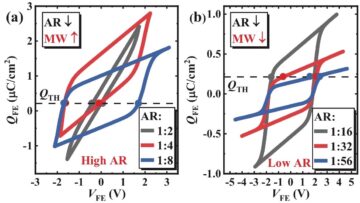

“随着人工智能(AI)应用的飞速发展,冯·诺依曼计算架构暴露出由于大量内存访问而带来的局限性,神经形态计算引起了人们的极大兴趣。神经形态计算提供的并行内存计算有可能显着改善延迟和功耗。模拟神经形态计算硬件的关键是忆阻器,它提供非易失性多态电导水平、高开关速度和能源效率。铁电隧道结 (FTJ) 忆阻器是实现此目的的主要候选者,但特定特性对其性能在集成到大型交叉阵列(深度神经网络推理和训练的核心计算元件)中的影响需要仔细研究。在这项工作中,W/Hf x Zr1-x O2/TiN FTJ 具有 60 种可编程电导状态,动态范围 (DR) 高达 10,电流密度 >3 A m - 2 at V 读 = 0.3 V 和高度非线性的电流-电压 (电流-电压) 特性 (>1100) 已通过实验证明。使用电路宏观模型,评估了真实交叉阵列的系统级性能,并实现了修改后的国家科学技术研究所 (MNIST) 数据集的 92% 分类准确率。最后,低电导与高度非线性相结合 电流-电压 这些特性使得能够实现用于神经形态硬件加速器的大型无选择器交叉阵列。”

找出 技术论文在这里。 2023 年 XNUMX 月发布。

Athle, R. 和 Borg, M. (2023),用于内存计算加速器的铁电隧道结忆阻器。副词。英特尔。系统。 2300554。 https://doi.org/10.1002/aisy.202300554

相关阅读

通过内存计算提高人工智能能源效率

如何处理 zettascale 工作负载并保持在固定的功耗预算内。

具有生物效率的内存计算建模

生成式人工智能迫使芯片制造商更智能地使用计算资源。

- :具有

- :是

- $UP

- 10

- 1100

- 2023

- 60

- a

- 加速器

- ACCESS

- 实现

- AI

- 和

- 应用领域

- 架构

- 保健

- 排列

- 人造的

- 人工智能

- 人工智能(AI)

- AS

- At

- 都

- 预算

- 但是

- by

- 候选人

- 特点

- 分类

- 关闭

- 组合

- 计算

- 计算

- 消费

- 核心

- 电流

- 十二月

- 深

- 深度神经网络

- 证明

- 密度

- 数字

- dr

- 两

- 动态

- 效率

- element

- enable

- 能源

- 能源效率

- 评估

- 裸露

- 终于

- 固定

- 针对

- 部队

- 大

- 硬件

- 有

- 重

- 此处

- 高

- 高度

- HTTPS

- 识别码

- 影响力故事

- 改善

- in

- 研究所

- 积分

- 房源搜索

- 兴趣

- 成

- 调查

- 键

- 大

- 潜伏

- 跨越

- Level

- 各级

- 限制

- 低

- 内存

- 改性

- 更多

- 国家

- 网络

- 神经

- 神经网络

- 全新

- 对象

- of

- on

- 打开

- 纸类

- 并行

- 特别

- 性能

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 潜力

- 功率

- 总理

- 过程

- 可编程

- 提供

- 优

- 出版

- 目的

- R

- 范围

- 实现

- 需要

- 研究人员

- 资源

- 科学

- 科学与技术

- 看到

- 显著

- 速度

- 州

- 留

- 系统

- 文案

- 专业技术

- 其

- Free Introduction

- 标题

- 至

- 产品培训

- true

- 隧道

- 大学

- 上

- 使用

- 运用

- 的

- 是

- 中

- 工作

- 和风网