یہ واپس آ گیا تھا۔ 1991 کہ Cadence نے سب سے پہلے Virtuoso پروڈکٹ کے نام کا اعلان کیا، اور ہم یہاں 32 سال بعد ہیں اور پروڈکٹ زندہ ہے اور کافی اچھی کارکردگی کا مظاہرہ کر رہی ہے۔ کیڈنس سے اسٹیون لیوس نے مجھے کسی نئی چیز کے بارے میں ایک اپ ڈیٹ دیا جسے وہ کہتے ہیں۔ ورچوسو اسٹوڈیواور یہ سب حقیقی دنیا کے لیے اپنی مرضی کے مطابق IC ڈیزائن کے بارے میں ہے۔ ان 32 سالوں میں ہم نے سیمی کنڈکٹر کے عمل کو مور کے قانون کے ساتھ 600nm سے پلانر CMOS کا استعمال کرتے ہوئے دیکھا ہے، 22 nm سے نیچے FinFET دور تک اسکیل کرتے ہوئے، 3nm نوڈ پر GAA تک پہنچتے ہیں۔ واضح طور پر EDA ٹول کے مطالبات بدل گئے ہیں کیونکہ چھوٹے نوڈس نے نئے جسمانی اثرات مرتب کیے ہیں جن کی پہلی سلیکون کامیابی کو یقینی بنانے کے لیے ماڈلنگ اور نقلی بنانے کی ضرورت ہے۔

Cadence Virtuoso اسٹوڈیو کی توجہ IC ڈیزائنرز کو چھ شعبوں کے ذریعے موجودہ دور کے چیلنجوں سے نمٹنے میں مدد کرنا ہے:

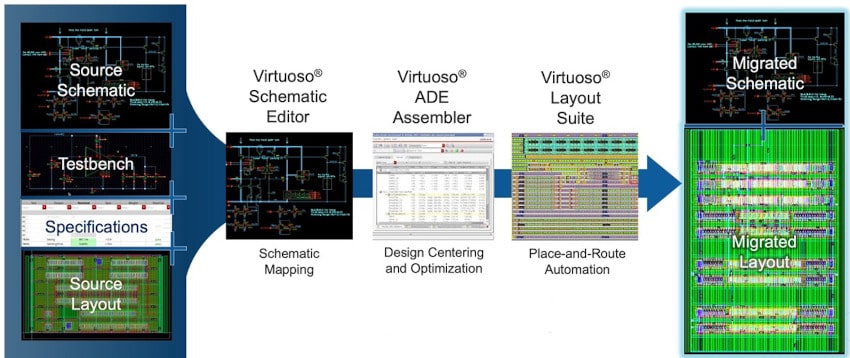

- عمل کی پیچیدگی میں اضافہ

- 10,000 سرکٹ سمیلیشنز کو ہینڈل کرنا

- ڈیزائن آٹومیشن اور سرکٹ کی منتقلی

- متضاد انضمام

- AI

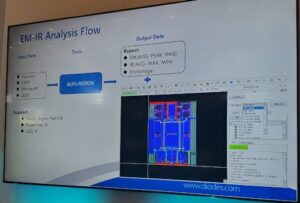

- سائن آف، ان ڈیزائن کی توثیق اور تجزیہ

۔ ورچوسو ADE (اینالاگ ڈیزائن ماحولیات) سرکٹ انجینئرز کو اسکیمیٹک کیپچر اور سرکٹ سمولیشن کے ذریعے اپنے اینالاگ، مخلوط سگنل اور آر ایف آئی سی ڈیزائن کو دریافت کرنے کی اجازت دیتا ہے۔ Virtuoso ADE کے فن تعمیر کو بہتر جاب کنٹرول، RAM کے استعمال کو کم کرنے، اور کلاؤڈ کا استعمال کرتے ہوئے سمیولیشن کو تیز کرنے کے لیے نئی شکل دی گئی ہے۔ ایک مثال کے طور پر 10,000s سمیولیشنز پر سپیکٹر چلانے کے لیے درکار RAM کو 420MB سے گھٹا کر صرف 18MB کر دیا گیا تھا، جب کہ اظہار کی تشخیص 420MB RAM سے گھٹ کر صرف 280MB رہ گئی تھی۔

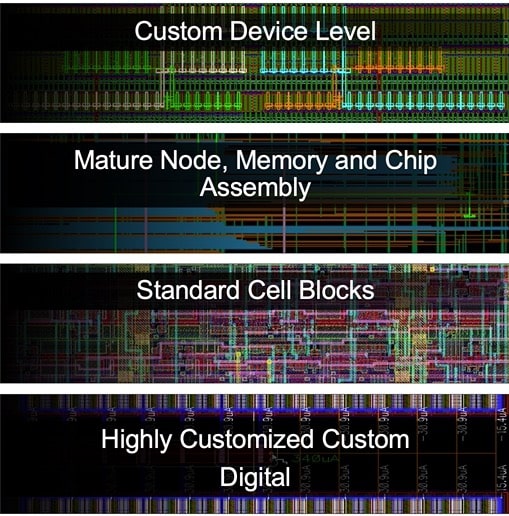

کے لئے تازہ ترین معلومات ورچوسو لے آؤٹ سویٹ جگہ اور راستے کی ٹیکنالوجی کے چار انتخاب شامل ہیں، ہر ایک Virtuoso ماحول کے ذریعے منفرد کام کے لیے موزوں ہے:

چار پی اینڈ آر ٹیکنالوجیز

DRC اور LVS رنز جسمانی تصدیق کا حصہ ہیں، اور ان کو بیچ موڈ میں چلانے، ٹھیک کرنا اور دہرانا، طویل ترقیاتی نظام الاوقات کا باعث بنتا ہے۔ ان ڈیزائن کی توثیق IC لے آؤٹ پر کام کرتے ہوئے DRC اور LVS کے انٹرایکٹو استعمال کی اجازت دیتی ہے، لہذا کیا تبدیل کرنا ہے اس پر فیڈ بیک تیزی سے نمایاں ہو جاتا ہے، جس سے پیداواری صلاحیت میں تیزی آتی ہے۔ Virtuoso لے آؤٹ سویٹ استعمال کرنے والا ایک لے آؤٹ ڈیزائنر ان ڈیزائن کی تصدیق سے فائدہ اٹھاتا ہے۔ Pegasus کے DRC اور LVS ٹیکنالوجی۔

چپلیٹس، 2.5D اور 3D پیکیجنگ پی سی بی، پیکیج اور آئی سی ڈیزائن ڈومینز کے روایتی طور پر الگ الگ دائروں پر محیط ہے۔ Virtuoso اسٹوڈیو پیکجز، ماڈیولز اور ICs کی کو-ڈیزائن اور تصدیق کو اس کے ذریعے قابل بناتا ہے:

مستقبل قریب کو دیکھتے ہوئے آپ اس بارے میں تفصیلات سامنے آنے کی توقع کر سکتے ہیں کہ مشین لرننگ اور تصریحات کی بنیاد پر ایک اینالاگ اسکیمیٹک سے لے آؤٹ میں خود بخود AI کو کس طرح لاگو کیا جا رہا ہے۔ یہ خود کار طریقے سے تیار کردہ ٹرائل لے آؤٹ ایک انتہائی محنتی عمل کو مزید تیز کریں گے۔ AI کو لاگو کرنے کے لیے دوسرا ڈویلپمنٹ ایریا کسٹم اینالاگ آئی پی کو نئے پروسیس نوڈ میں منتقل کرنے کا مسئلہ ہے۔ دیکھتے رہنا.

Virtuoso سٹوڈیو کے ابتدائی صارفین میں IC اور پیکیج کے کو-ڈیزائن کے لیے اینالاگ ڈیوائسز، MediaTek میں معروف IC صارفین کے ڈیزائن، اور Renesas میں AI پر مبنی عمل کی منتقلی شامل ہیں۔

خلاصہ

Virtuoso Studio نے 23.1 کی ریلیز میں کچھ متاثر کن نئی خصوصیات رکھی ہیں جنہیں IC ڈیزائن ٹیمیں زیادہ نتیجہ خیز بننے کے لیے استعمال کرنا شروع کر سکتی ہیں۔ مور کے قانون کے چیلنجوں کا مقابلہ کرنے کے لیے ورچوسو انفراسٹرکچر تبدیل ہو گیا ہے، 10,000s سرکٹ سمیولیشنز کے ساتھ سیمولیشنز عملی ہیں، RFIC اور ماڈیول 2.5D/3D کو-ڈیزائن کی حمایت کی گئی ہے، ان ڈیزائن DRC/LVS کی تصدیق میں بہت کم وقت لگتا ہے، اور AI ہے۔ خودکار ینالاگ کاموں پر لاگو کیا جا رہا ہے۔

متعلقہ بلاگز

اس پوسٹ کو بذریعہ شیئر کریں:- SEO سے چلنے والا مواد اور PR کی تقسیم۔ آج ہی بڑھا دیں۔

- پلیٹو بلاک چین۔ Web3 Metaverse Intelligence. علم میں اضافہ۔ یہاں تک رسائی حاصل کریں۔

- ایڈریین ایشلے کے ساتھ مستقبل کا نقشہ بنانا۔ یہاں تک رسائی حاصل کریں۔

- ماخذ: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- : ہے

- : ہے

- $UP

- 1

- 10

- 3d

- a

- ہمارے بارے میں

- تیز

- AI

- تمام

- کی اجازت دیتا ہے

- ساتھ

- اور

- کا اعلان کیا ہے

- اطلاقی

- فن تعمیر

- کیا

- رقبہ

- علاقوں

- AS

- At

- خود کار طریقے سے

- خود کار طریقے سے

- میشن

- واپس

- کی بنیاد پر

- BE

- رہا

- کیا جا رہا ہے

- نیچے

- فوائد

- بہتر

- لایا

- by

- Cadence سے

- فون

- کر سکتے ہیں

- قبضہ

- چیلنجوں

- تبدیل

- انتخاب

- واضح طور پر

- بادل

- صارفین

- کنٹرول

- اپنی مرضی کے

- گاہکوں

- دن

- مطالبات

- ڈیزائن

- ڈیزائنر

- ڈیزائنرز

- ڈیزائن

- تفصیلات

- ترقی

- کے الات

- کر

- ڈومینز

- نیچے

- ہر ایک

- اثرات

- کے قابل بناتا ہے

- انجینئرز

- کو یقینی بنانے کے

- ماحولیات

- دور

- اندازہ

- مثال کے طور پر

- توقع ہے

- تلاش

- خصوصیات

- آراء

- پہلا

- توجہ مرکوز

- کے لئے

- چار

- سے

- مزید

- مستقبل

- Go

- ہاتھ

- ہے

- مدد

- یہاں

- روشنی ڈالی گئی

- کس طرح

- HTML

- HTTPS

- ICS

- متاثر کن

- in

- شامل

- انفراسٹرکچر

- انٹرایکٹو

- IP

- ایوب

- فوٹو

- لیبر

- قانون

- لے آؤٹ

- لیڈز

- سیکھنے

- لیوس

- لانگ

- مشین

- مشین لرننگ

- مارچ

- زیادہ سے زیادہ چوڑائی

- سے ملو

- منتقلی

- موڈ

- ماڈیول

- ماڈیولز

- نگرانی

- زیادہ

- نام

- قریب

- ضرورت

- نئی

- نئی خصوصیات

- نوڈ

- نوڈس

- of

- on

- ایک

- پیکج

- پیکجوں کے

- پیکیجنگ

- حصہ

- جسمانی

- مقام

- پلاٹا

- افلاطون ڈیٹا انٹیلی جنس

- پلیٹو ڈیٹا

- پوسٹ

- عملی

- حال (-)

- مسئلہ

- عمل

- مصنوعات

- پیداواری

- پیداوری

- ڈال

- جلدی سے

- RAM

- پہنچنا

- اصلی

- حقیقی دنیا

- کم

- کو کم کرنے

- جاری

- ضرورت

- روٹ

- رن

- چل رہا ہے

- سکیلنگ

- دوسری

- تفصیلات دیکھیں

- سیمکولیٹر

- علیحدہ

- سلیکن

- تخروپن

- چھ

- چھوٹے

- So

- کچھ

- کچھ

- دورانیہ

- وضاحتیں

- اسپیکٹرم

- تیزی

- شروع کریں

- رہنا

- سٹوڈیو

- کامیابی

- سویٹ

- تائید

- لے لو

- لیتا ہے

- ٹاسک

- کاموں

- ٹیموں

- ٹیکنالوجی

- کہ

- ۔

- ان

- یہ

- کے ذریعے

- وقت

- کرنے کے لئے

- کے آلے

- روایتی طور پر

- مقدمے کی سماعت

- منفرد

- اپ ڈیٹ کریں

- استعمال

- استعمال کی شرائط

- توثیق

- کی طرف سے

- اچھا ہے

- کیا

- جبکہ

- گے

- ساتھ

- کام کر

- دنیا

- سال

- زیفیرنیٹ