SPIE ایڈوانسڈ لتھوگرافی کانفرنس فروری میں منعقد ہوئی تھی۔ مجھے حال ہی میں imec میں جدید پیٹرننگ کے عمل اور مواد کے نائب صدر Steven Scheer کا انٹرویو کرنے اور imec کے پیش کردہ منتخب کاغذات کا جائزہ لینے کا موقع ملا۔

میں نے اسٹیو سے پوچھا کہ اس سال SPIE میں سب سے اہم پیغام کیا تھا، اس نے کہا کہ ہائی NA کے لیے تیاری کلیدی ہے۔ اس نے ماحولیاتی نظام کے تین اہم علاقوں کی نشاندہی کی:

- ماسک اور ریزولوشن انہانسمنٹ ٹیکنالوجی (RET) انفراسٹرکچر۔

- مواد، photoresist اور underlayers.

- میٹرولوجی

نمائش کے اوزار بھی یقینا کلیدی ہیں، لیکن یہ وہ نہیں ہے جس سے اسٹیو بات کرتا ہے۔ مصنفین نوٹ کریں - میں ASML کی SPIE پریزنٹیشنز پر بھی لکھوں گا۔

ماسک

اسٹیو نے ماسک سے متعلق مسائل کی فہرست جاری کی:

- ماسک 3d اثرات، جیسے فوکس شفٹ اور کنٹراسٹ نقصان - ہائی این اے ایک کم زاویہ کی نمائش ہے جو 3D اثرات کو زیادہ مسئلہ بناتی ہے۔

- کم خرابی والے ماسک خالی جگہیں اور کھردری اور سی ڈی میں کم تغیر کے ساتھ ماسک

- زیادہ کنٹراسٹ کو فعال کرنے اور ماسک 3D اثرات کو کم کرنے کے لیے لو-این ماسک کی ضرورت ہے۔

- آپٹیکل قربت کی اصلاح کی تکنیک۔

- ماسک تحریر، ملٹی بیم۔

- ماسک سلائی - اسکینر فیلڈ کے چھوٹے سائز کے لیے ضروری ہے کہ ڈائی کو ایک ساتھ سلائی جائے۔

- 4x ایک سمت، 8x دوسری سمت میں سلائی کو فعال کرنے کے لیے ایک نئی قسم کے ماسک ڈیزائن کی ضرورت ہے۔

- اعلی منبع توانائی کے لئے پیلیکلز۔

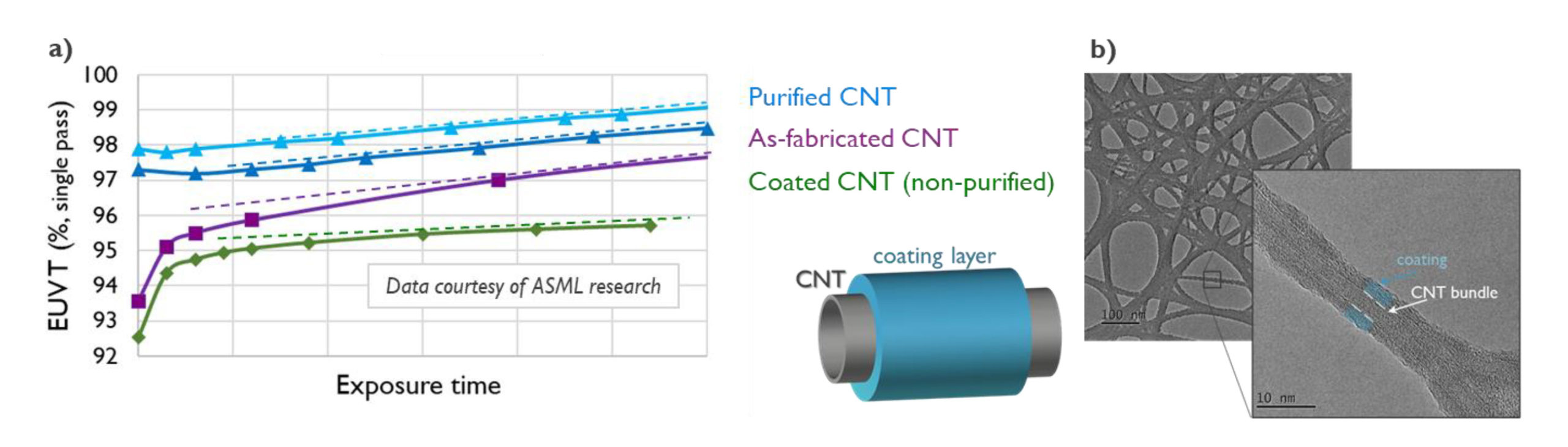

In "CNT pellicles: حالیہ اصلاح اور نمائش کے نتائج،" Joost Bekaert et.al. نے کاربن نانوٹوب پیلیکلز (CNT) کی کھوج کی۔

ASML کے روڈ میپ پر 600 واٹ کے سورس سسٹمز ہیں، دھاتی سلیسائیڈ پر مبنی موجودہ پیلیکلز صرف تقریباً 400 واٹ تک قابل عمل ہیں۔ پیلیکلز کو ذرات کو روکنے، زیادہ ٹرانسمیشن، تقریباً 110 ملی میٹر بائی 140 ملی میٹر کے رقبے پر معطل ہونے کے لیے کافی مکینیکل طاقت، اور پائیدار ہونے کی ضرورت ہوتی ہے۔ CNT نے 98٪ تک ٹرانسمیشن ظاہر کی ہے۔ EUV تابکاری اتنی توانا ہوتی ہے کہ یہ ایک ہائیڈروجن پلازما بناتی ہے جو پیلیکل کو کھینچتی ہے جس کے نتیجے میں میکانیکی سالمیت کے چھلکے کو نقصان پہنچتا ہے۔ imec اینچ کی شرحوں کا جائزہ لے رہا ہے اور پیلیکل کو کیسے مستحکم کیا جائے۔

اینچنگ کی شرحوں کا اندازہ ٹرانسمیشن کو دیکھ کر کیا جا سکتا ہے، کیونکہ پیلیکل اینچنگ سے پتلا ہوتا ہے، ٹرانسمیشن بڑھ جاتی ہے۔ شکل 1 مختلف حالات کے تابع ایک پیلیکل کے وقت کے ساتھ ٹرانسمیشن کی وضاحت کرتا ہے۔

ASML ایک آف لائن پلازما ایکسپوژر ٹول کا استعمال کرتے ہوئے پیلیکل ٹرانسمیشن بمقابلہ نمائش کے وقت کا جائزہ لیتا ہے اور اس کام میں، imec نے 3,000 ویفرز تک CNT پیلیکل ایکسپوژر کا مظاہرہ کیا (96 30 mJ/cm² فی ویفر پر مرتا ہے)، اور اسکپوز سے حاصل کردہ نتائج کے درمیان ارتباط ظاہر کیا۔ اور وہ آف لائن ٹول سے۔

پیلیکلز میں ابتدائی طور پر مینوفیکچرنگ کے عمل سے غیر مستحکم نامیاتی نجاست ہوتی ہے جو EUV توانائی کو جذب کرتی ہے جب تک کہ وہ جل نہ جائیں، سبز اور جامنی رنگ کے منحنی خطوط دیکھیں۔ اعلی درجہ حرارت پر پیلیکل کو پکانا آلودگیوں کو جلا کر پیلیکل کو "پاک" کرتا ہے جس کے نتیجے میں اینچ ریٹ پر ٹرانسمیشن میں تبدیلی آتی ہے۔ دو نیلے منحنی خطوط کی ڈھلوان اینچ کی شرح کی وجہ سے ہے۔ سبز منحنی خطوط ایک "کوٹڈ" پیلیکل کی عکاسی کرتا ہے جو کم اینچ کی شرح کو ظاہر کرتا ہے، تاہم کوٹنگ ٹرانسمیشن کو کم کرتی ہے اور بہت زیادہ طاقت کی سطح کے ساتھ مطابقت نہیں رکھتی ہے۔

فوٹو اسٹورسٹ

سٹیو، پھر photoresist پر تبادلہ خیال کیا.

فوٹو ریزسٹ کے لیے 24nm سے 20nm پچ 16nm پچ حتمی ریزولوشن کے ساتھ ہائی NA اندراج کے لیے ایک خوبصورت جگہ ہے۔ کیمیکل امپلیفائیڈ ریزسٹ (CAR) کی کارکردگی 24nm سے کم ہے۔ میٹل آکسائیڈ ریزسٹ (MOR) 17nm یا یہاں تک کہ 16nm تک امید افزا نظر آتا ہے۔ خرابی اب بھی ایک مسئلہ ہے۔ 24nm پچ کے لیے خوراک 67mJ/cm ہے۔2 MOR اور 77mJ/cm کے لیے2 کار کے لیے۔ MOR میں استحکام کے کچھ مسائل ہیں اور جتنی کم خوراک ہوگی مزاحمت اتنی ہی زیادہ رد عمل/کم مستحکم ہوگی۔ یہ چیلنجز ہیں، شو اسٹاپرز نہیں۔

In "EUV لتھوگرافی کے لیے جمع شدہ زیریں پرتوں کو چھوٹا کیا گیا،" گپتا وغیرہ نے فوٹو ریزسٹ انڈر لیئرز کی کھوج کی۔ جیسے جیسے پچ سکڑ جاتی ہے، اسی فوٹو ریزسٹ پرت کے لیے پہلو کا تناسب بڑھ جاتا ہے اور پیٹرن کے خاتمے کا باعث بن سکتا ہے۔ بہتر انڈر لیئر آسنجن اس کو حل کر سکتا ہے۔ پہلو کے تناسب کو منظم کرنے کے لیے باری باری ایک پتلی فوٹو ریزسٹ کا استعمال کیا جا سکتا ہے لیکن یہ اینچ کے مسائل کا باعث بن سکتا ہے جب تک کہ پرت کے نیچے اعلی اینچ سلیکٹیوٹی نہ مل جائے۔

imec نے پایا کہ جمع شدہ انڈر لیئرز کی سطحی توانائی کو بہتر آسنجن حاصل کرنے کے لیے فوٹو ریزسٹ سے ملایا جا سکتا ہے۔ جمع شدہ انڈر لیئر کی کثافت ٹیوننگ کو بہتر اینچ سلیکٹیوٹی فراہم کرنے کے لیے استعمال کیا جا سکتا ہے۔

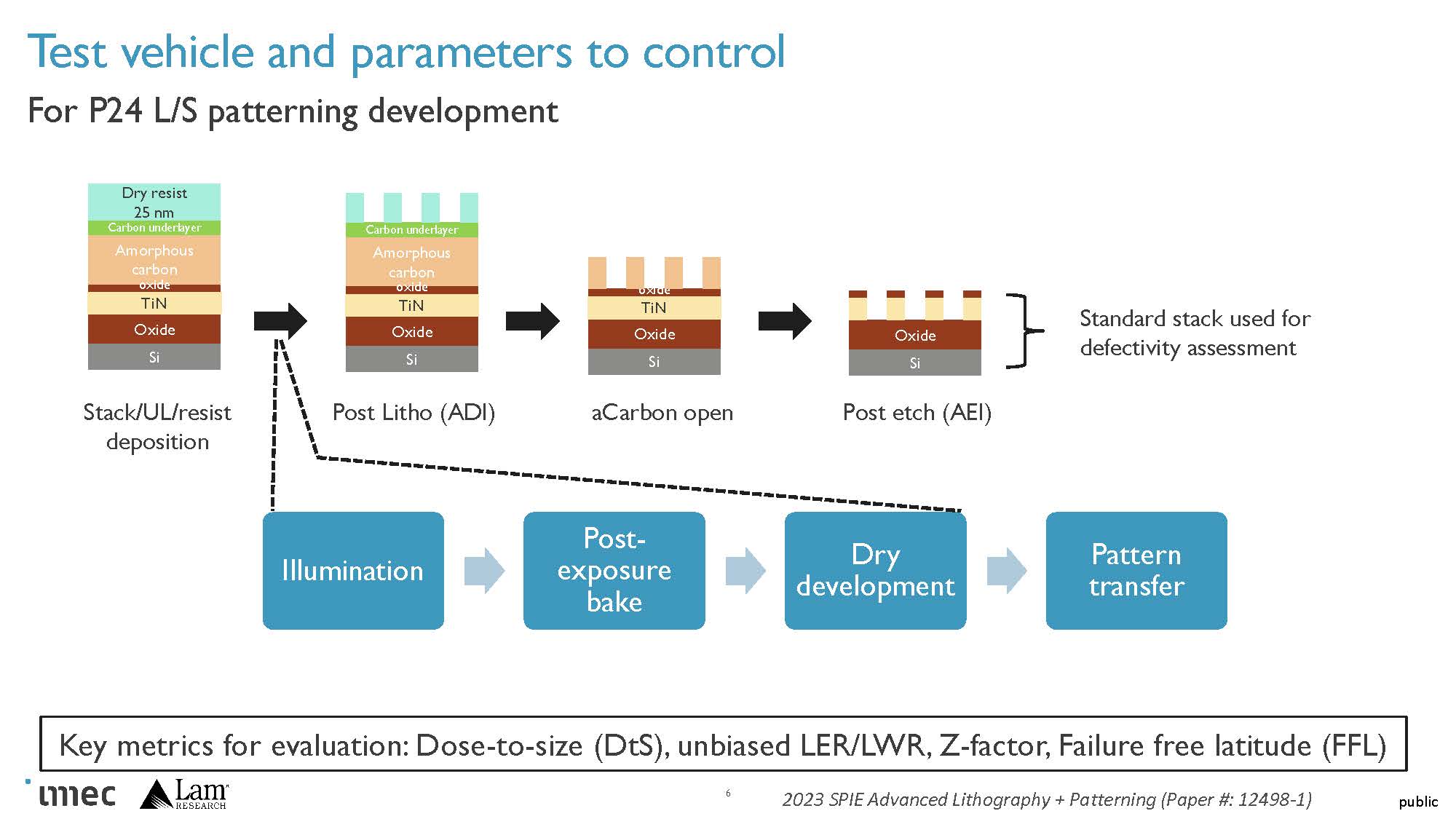

In "اعلی NA EUV لتھوگرافی کی طرف خشک مزاحمت پیٹرننگ کی تیاری،" Imec اور Lam سے Hyo Sean Suh et.al. نے لام کے خشک فوٹو ریزسٹ عمل کو دریافت کیا۔ N2+ اور A14 پراسیسز کے لیے میٹل 2 پچ (M2P) 24nm ٹپ ٹو ٹپ (T15T) کے ساتھ ~2nm ہونے کی توقع ہے اور پھر A10 M2P پر <22nm T15T کے ساتھ ~2nm ہوگی۔

لام خشک مزاحمتی عمل کو تصویر 2 میں دکھایا گیا ہے۔

پوسٹ ایکسپوزر بیک (PEB) خوراک میں کمی کو مضبوطی سے چلاتا ہے لیکن پلوں اور کھردری کو متاثر کرتا ہے۔ تعاون کو بہتر بنانے والی ترقی اور نقاشی پلوں اور کھردری کو کم کرتی ہے اور 24nm پچ L/S پیٹرننگ کے لیے ایک مضبوط عمل ونڈو دکھاتی ہے۔

In "0.55NA EUV سنگل پیٹرننگ کے ساتھ لاجک میٹل اسکیلنگ کی فزیبلٹی،" Dongbo Xu et.al. ہائی-NA (0.55NA) سسٹم سنگل پیٹرننگ کے ساتھ کیا حاصل کرسکتا ہے اس کا اندازہ بیان کیا۔

انہوں نے یہ نتیجہ اخذ کیا کہ 24nm پچ قابل حصول نظر آتی ہے۔ 20nm افقی سمت میں امید افزا لگتا ہے لیکن عمودی سمت میں مزید کام کی ضرورت ہے۔ 18nm پچ کو اضافی کام کی ضرورت ہے۔

EUV لائن کی کھردری اور سٹاکسٹک خرابی کے نقطہ نظر سے ایک بہت ہی چیلنجنگ ٹیکنالوجی ثابت ہوئی ہے۔ ڈائریکٹڈ سیلف اسمبلی (DSA) ایک ٹکنالوجی ہے جو ایک طویل عرصے سے چلی آرہی ہے لیکن اس نے زیادہ توجہ حاصل نہیں کی ہے۔ DSA اب EUV کے لیے لائن کی کھردری اور اسٹاکسٹک نقائص کو دور کرنے کے لیے ایک تکنیک کے طور پر توجہ حاصل کر رہا ہے۔

In "ای یو وی لیتھوگرافی لائن اسپیس پیٹرن رییکٹیفیکیشن بلاک کوپولیمر کا استعمال کرتے ہوئے خود اسمبلی کی ہدایت: ایک کھردری اور خرابی کا مطالعہ،" جولی وان بیل وغیرہ۔ پتہ چلا کہ DSA کو EUV کے ساتھ ملانا DSA کے عمل سے بہتر ہے جس کی بنیاد Immersion Lithography پر مبنی ہے جس میں نچلی لکیر کی چوڑائی کی کھردری اور کوئی جگہ جگہ خرابی نہیں ہے۔

In "ڈائریکٹڈ سیلف اسمبلی کے ذریعہ EUV لتھوگرافی میں اسٹاکسٹکس کو کم کرنا" Lander Verstraete et.al. EUV پروسیسنگ میں اسٹاکسٹک نقائص کو کم کرنے کے لیے DSA کا استعمال کرتے ہوئے دریافت کیا گیا۔

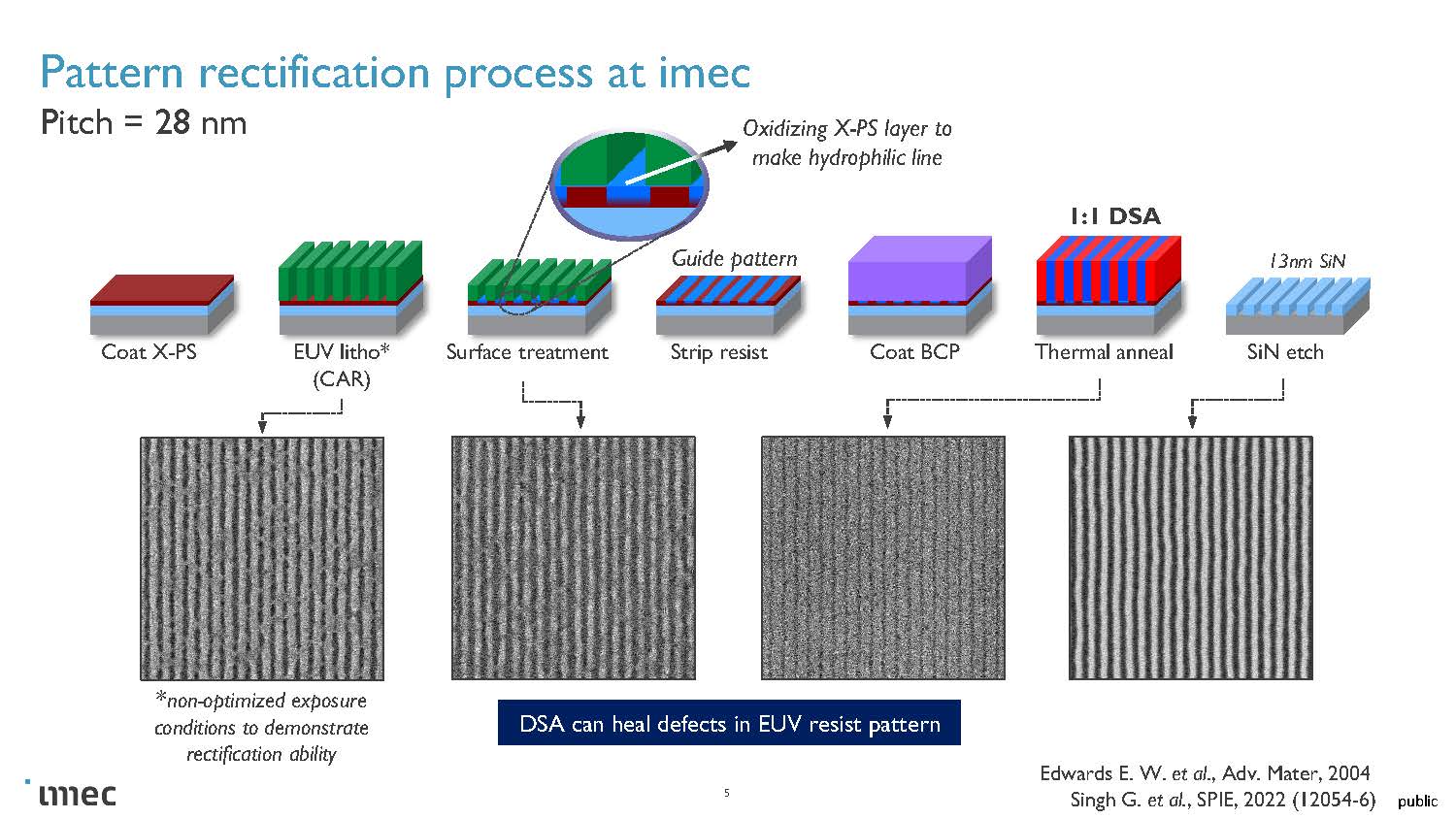

لائن/اسپیس EUV نقائص کو درست کرنے کے imec عمل کو شکل 3 میں دکھایا گیا ہے۔

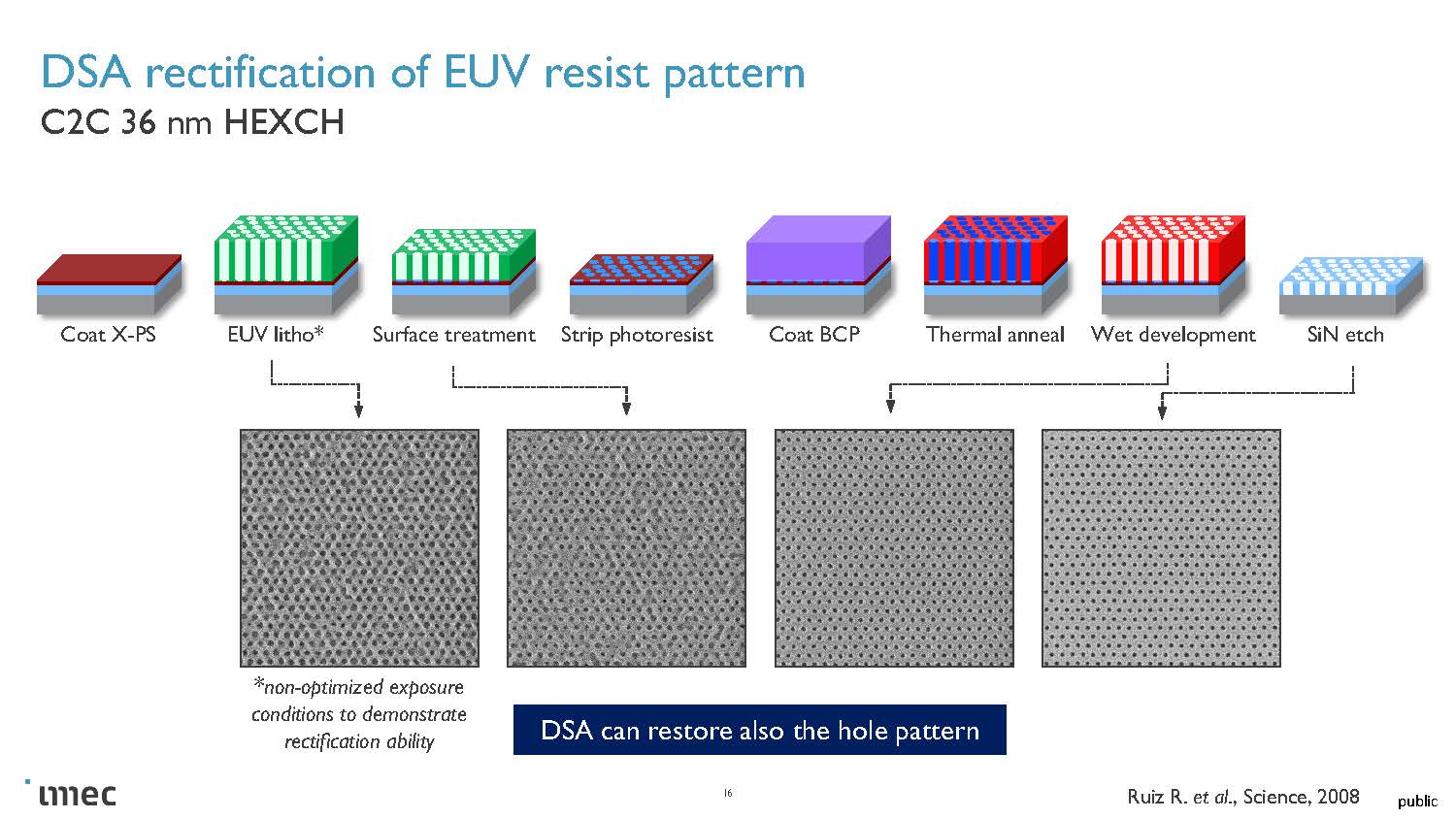

رابطہ صفوں میں نقائص کو دور کرنے کے لیے imec عمل کو شکل 4 میں دکھایا گیا ہے۔

EUV پلس DSA 28nm پچ پر لائن/اسپیسز کے لیے بہت امید افزا نظر آتا ہے جس میں بنیادی خرابی پلوں کی ہے۔ پل کے بہت سے نقائص کے ساتھ 24nm پچ میں بہتری کی ضرورت ہے۔ نقائص بلاک کوپولیمر کی تشکیل اور اینیل ٹائم کے ساتھ منسلک ہوتے ہیں۔

رابطہ صفوں کے لیے EUV + DSA لوکل کریٹیکل ڈائمینشن یونیفارمٹی (LCDU) اور پیٹرن پلیسمنٹ ایرر کو بہتر بناتا ہے اور کم خوراک کو قابل بناتا ہے۔

میٹرولوجی

چونکہ فلم کی موٹائی میں میٹرولوجی سگنل کو شور کے تناسب سے کم کیا جاتا ہے ایک مسئلہ بن جاتا ہے۔

EUV کے ساتھ ایک خرابی کے عمل کی کھڑکی ہے، ایک طرف ایک چٹان ہے جہاں پیٹرن میں ٹوٹنا ایک مسئلہ بن جاتا ہے اور کھڑکیوں کے دوسری طرف ایک چٹان ہے جہاں پیٹرن کے درمیان پل ایک مسئلہ بن جاتے ہیں۔

جب نئی پچ بنانے کی کوشش کی جاتی ہے تو بہت سے نقائص ہوتے ہیں جو وقت کے ساتھ ساتھ ختم ہو جاتے ہیں۔

کافی حساسیت کے ساتھ کافی بڑے علاقے کی پیمائش کرنا مشکل ہے۔ ای بیم کا معائنہ حساس لیکن سست ہے، آپٹیکل تیز ہے لیکن حساس نہیں ہے۔ CFET جیسے نئے 3D عمل اضافی چیلنجز متعارف کراتے ہیں۔

In "اعلی NA EUVL کے لئے خشک مزاحمت میٹرولوجی تیاری،" Gian Francesco Lorusso et.al، اٹامک فورس مائیکروسکوپ (AFM)، ای بیم معائنہ اور CD SEM کی بہت پتلی فوٹو ریزٹس کی خصوصیت کے لیے تحقیقات کرتے ہیں۔

لام ڈرائی فوٹو ریزسٹ عمل کا استعمال کرتے ہوئے < CD SEM کو 5nm موٹی فوٹو ریزسٹ تک قابل عمل دکھایا گیا تھا۔ جیسا کہ مزاحمتی موٹائی میں کمی واقع ہوئی لائن کی کھردری میں اضافہ ہوا، پل کے نقائص کی پرنٹ ایبلٹی میں کمی آئی جبکہ وقفے کے نقائص وہی رہے۔ پیٹرن کا خاتمہ صرف موٹی فلموں میں دیکھا گیا تھا۔ AFM پیمائش نے اشارہ کیا کہ فلم کی موٹائی کم ہوتی ہے۔ ای بیم نے بہت اچھی فلموں کے لیے بھی نقائص کی اچھی گرفت دکھائی۔

In "3D دور کے لیے سیمی کنڈکٹر میٹرولوجی،" J. Bogdanowicz et.al.، 3D ڈھانچے پر میٹرولوجی کے چیلنجز کو دریافت کریں۔

3D دور میں، Z سمت نئی X/Y اسکیلنگ بن گئی ہے۔ منطقی آلات کے لیے، CFET اور Semi damascene چیلنجز پیش کرتے ہیں، میموری میں 3D DRAM مستقبل کا چیلنج ہے، اور سسٹم ٹیکنالوجی کو آپٹیمائزیشن (STCO) کے لیے 3D انٹر کنیکٹس ایک اور چیلنج ہیں۔

افقی نانوشیٹ اور سی ایف ای ٹی کے لیے لیٹرل ریسیس اور فل کریکٹرائزیشن اور ملٹی لیئر اسٹیک میں باقیات اور دیگر نقائص کا پتہ لگانا اہم ہوگا۔ 3D میموری میں ہائی ایسپیکٹ ریشو (HAR) ہول/اسپلٹ پروفائلنگ اور ملٹی لیئر فلموں میں دفن نقائص اور باقیات کا پتہ لگانے والی منطق کی طرح اہم ہوگا۔ STCO ایپلی کیشنز کے لیے بانڈنگ انٹرفیس اور صف بندی کی سالمیت کلیدی ہوگی۔

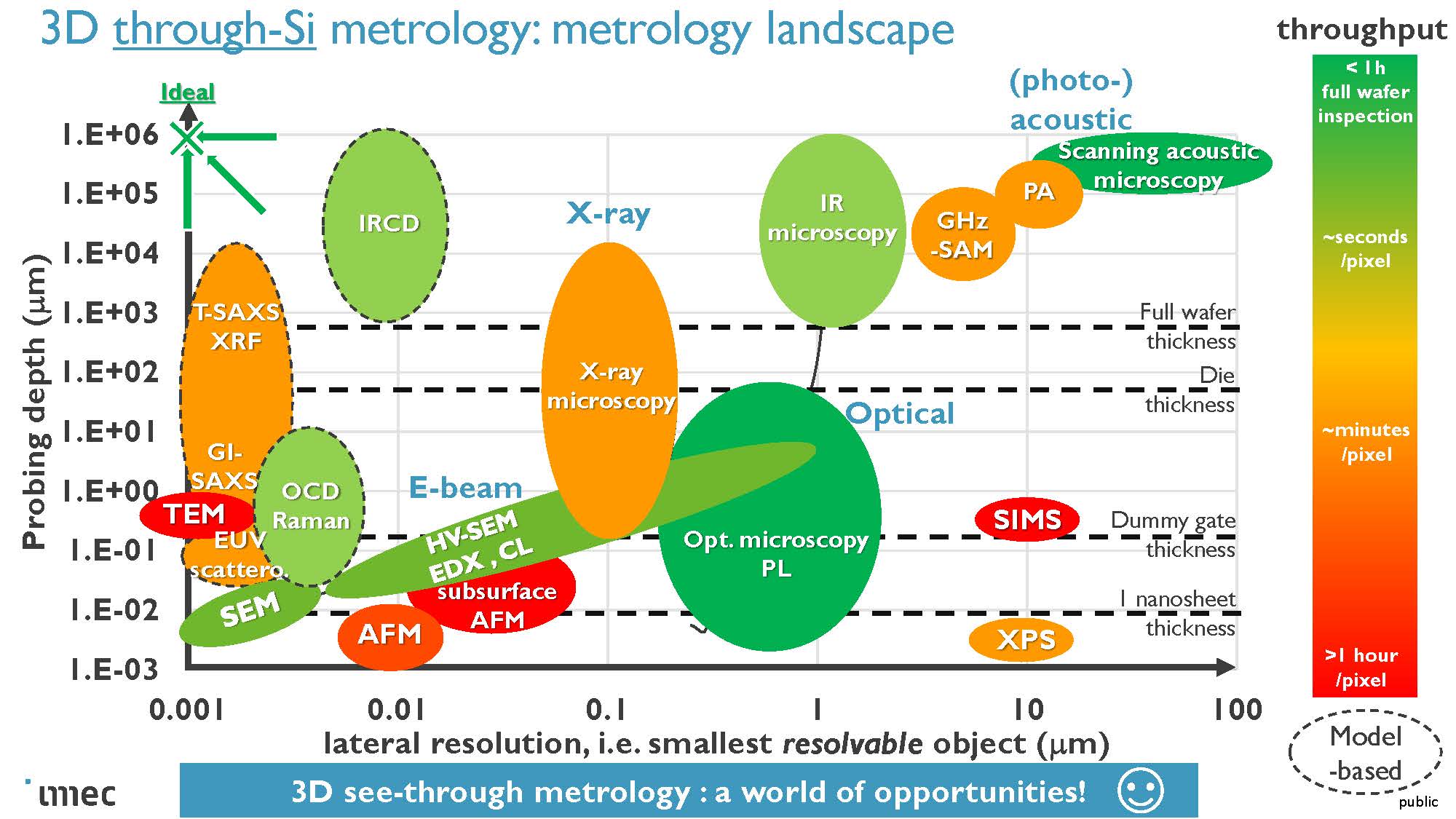

روایتی سطح کی میٹرولوجی کے لیے حساسیت اور رفتار کے درمیان پہلے سے ہی ایک تجارت ہے، اب معائنہ کی گہرائی بمقابلہ پس منظر کی قرارداد ایک اہم تجارت ہے۔ شکل 5 مختلف میٹرولوجی تکنیکوں کے لئے لیٹرل ریزولوشن اور تھرو پٹ بمقابلہ تحقیقات کی گہرائی کو پیش کرتا ہے۔

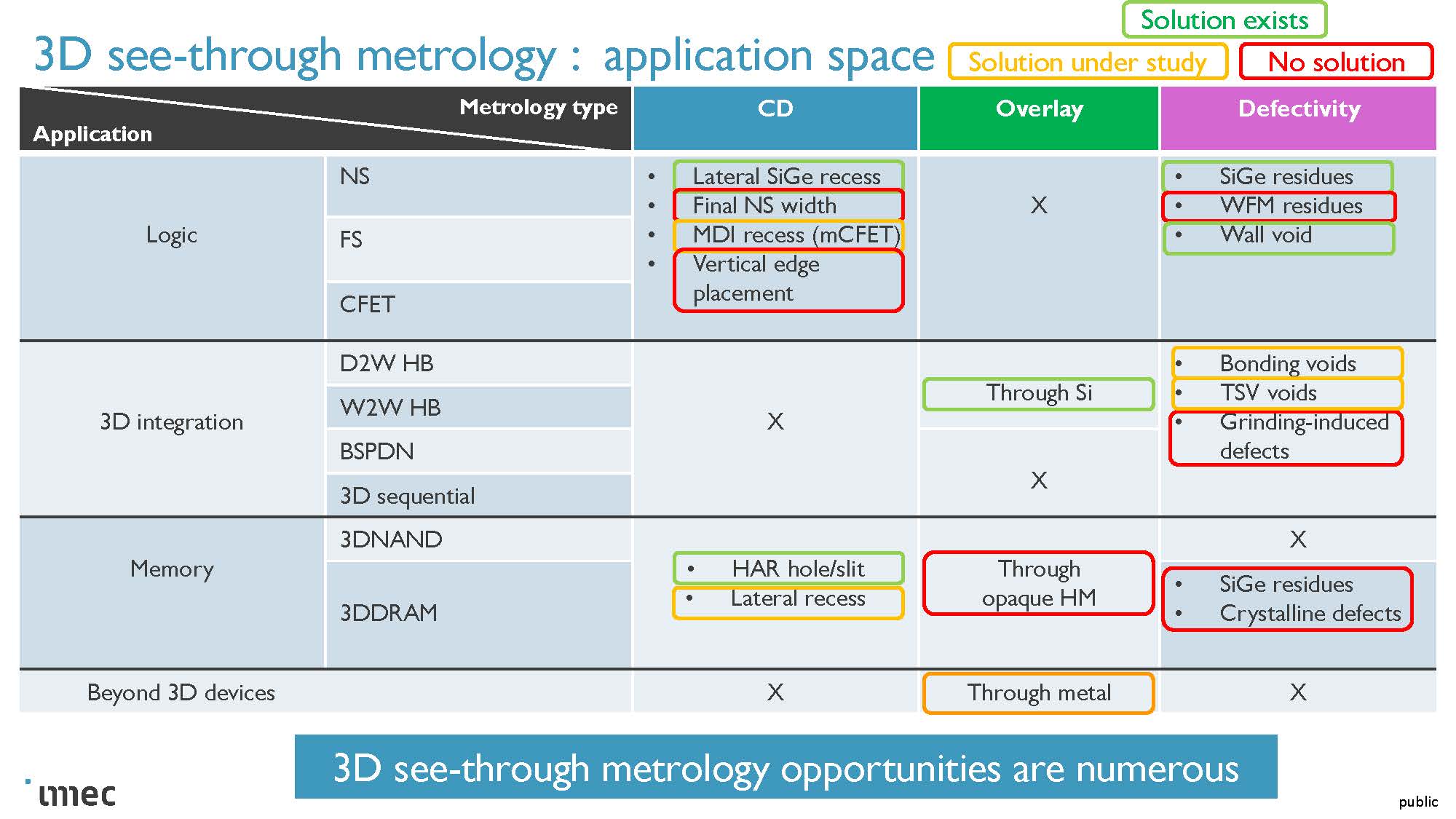

شکل 6 مختلف ضروریات کو پورا کرنے کے لیے 3D میٹرولوجی کی موجودہ تیاری کا خلاصہ کرتا ہے۔

اعداد و شمار 6 سے اب بھی ایک جامع میٹرولوجی پروگرام کے حصول کے لیے بہت سارے چیلنجز پر قابو پانا ہے۔

نتیجہ

ہائی NA EUV کا دور قریب آ رہا ہے۔ پیلیکلز، فوٹو ریزسٹ اور میٹرولوجی میں اچھی پیش رفت ہو رہی ہے اور مزید پیش رفت کے لیے IMEC تینوں شعبوں میں کام جاری رکھے ہوئے ہے۔

بھی پڑھیں:

TSMC نے 300mm پر آپ کے خیال سے کہیں زیادہ رقم خرچ کی ہے۔

SPIE ایڈوانسڈ لتھوگرافی کانفرنس 2023 - AMAT Sculpta® اعلان

IEDM 2023 - 2D مواد - Intel اور TSMC

اس پوسٹ کو بذریعہ شیئر کریں:

- SEO سے چلنے والا مواد اور PR کی تقسیم۔ آج ہی بڑھا دیں۔

- پلیٹوآئ اسٹریم۔ ویب 3 ڈیٹا انٹیلی جنس۔ علم میں اضافہ۔ یہاں تک رسائی حاصل کریں۔

- ایڈریین ایشلے کے ساتھ مستقبل کا نقشہ بنانا۔ یہاں تک رسائی حاصل کریں۔

- PREIPO® کے ساتھ PRE-IPO کمپنیوں میں حصص خریدیں اور بیچیں۔ یہاں تک رسائی حاصل کریں۔

- ماخذ: https://semiwiki.com/lithography/329278-spie-2023-imec-preparing-for-high-na-euv/

- : ہے

- : ہے

- : نہیں

- :کہاں

- $UP

- 000

- 1

- 2022

- 2023

- 2D

- 2D مواد

- 30

- 3d

- a

- حاصل

- اصل

- ایڈیشنل

- پتہ

- اعلی درجے کی

- اعلی درجے کی لتھوگرافی

- AL

- تمام

- پہلے ہی

- بھی

- Amplified

- an

- اور

- ایک اور

- ایپلی کیشنز

- قریب

- تقریبا

- کیا

- رقبہ

- علاقوں

- ارد گرد

- AS

- پہلو

- اسمبلی

- At

- کوشش کی

- توجہ

- مصنفین

- بیکنگ

- کی بنیاد پر

- BE

- بیم

- بن

- رہا

- کیا جا رہا ہے

- نیچے

- کے درمیان

- بلاک

- بلیو

- توڑ

- وقفے

- پل

- پلوں

- جلا

- لیکن

- by

- کر سکتے ہیں

- قبضہ

- کار کے

- کاربن

- CD

- چیلنج

- چیلنجوں

- چیلنج

- تبدیلیاں

- CO

- نیست و نابود

- امتزاج

- ہم آہنگ

- وسیع

- یہ نتیجہ اخذ کیا

- حالات

- کانفرنس

- رابطہ کریں

- آلودگی

- جاری ہے

- اس کے برعکس

- باہمی تعلق۔

- کورس

- پیدا

- اہم

- موجودہ

- وکر

- کم ہے

- demonstrated,en

- کثافت

- جمع

- گہرائی

- بیان کیا

- ڈیزائن

- ترقی

- کے الات

- مر

- طول و عرض

- سمت

- بات چیت

- سندچیوتی

- کر

- نیچے

- ڈرائیو

- کارفرما

- خشک

- دو

- e

- ای اینڈ ٹی

- ماحول

- اثرات

- کو چالو کرنے کے

- کے قابل بناتا ہے

- توانائی

- اضافہ

- کافی

- دور

- خرابی

- اندازہ

- کا جائزہ لینے

- تشخیص

- بھی

- آخر میں

- نمائش

- توقع

- تلاش

- وضاحت کی

- نمائش

- فاسٹ

- فروری

- میدان

- اعداد و شمار

- بھرنے

- فلم

- فلمیں

- توجہ مرکوز

- کے لئے

- مجبور

- تشکیل

- ملا

- سے

- مزید

- مستقبل

- حاصل کرنے

- اچھا

- سبز

- تھا

- ہارڈ

- ہے

- he

- Held

- ہائی

- اعلی

- افقی

- کس طرح

- کیسے

- تاہم

- HTTPS

- ہائیڈروجن

- i

- کی نشاندہی

- وضاحت کرتا ہے

- وسعت

- بہتر

- بہتری

- بہتر ہے

- in

- اضافہ

- اضافہ

- اشارہ کیا

- انفراسٹرکچر

- ابتدائی طور پر

- سالمیت

- انٹیل

- آپس میں جڑتا ہے

- انٹرفیسز

- انٹرویو

- متعارف کرواتا ہے

- کی تحقیقات

- مسئلہ

- مسائل

- IT

- فوٹو

- کلیدی

- لام

- زمین کی تزئین کی

- بڑے

- پرت

- تہوں

- قیادت

- معروف

- سطح

- کی طرح

- لائن

- لسٹ

- مقامی

- منطق

- لانگ

- طویل وقت

- دیکھو

- تلاش

- دیکھنا

- بند

- بہت

- لو

- بنا

- بنانا

- انتظام

- مینوفیکچرنگ

- بہت سے

- ماسک

- ماسک

- ملا

- مواد

- زیادہ سے زیادہ چوڑائی

- مئی..

- پیمائش

- پیمائش

- میکانی

- یاد داشت

- پیغام

- دھات

- میٹرولوجی

- خوردبین

- تخفیف کریں

- قیمت

- زیادہ

- بہت

- کثیر

- ضرورت ہے

- ضرورت

- ضروریات

- نئی

- نہیں

- شور

- اب

- حاصل کی

- of

- بند

- آف لائن

- on

- ایک

- صرف

- مواقع

- اصلاح کے

- or

- نامیاتی

- دیگر

- باہر

- پر

- پر قابو پانے

- کاغذات

- پاٹرن

- پیٹرن

- کارکردگی

- نقطہ نظر

- پچ

- پلازما

- پلاٹا

- افلاطون ڈیٹا انٹیلی جنس

- پلیٹو ڈیٹا

- علاوہ

- غریب

- پوسٹ

- کی تیاری

- پیش پیش

- پیش

- تحفہ

- صدر

- پرائمری

- مسئلہ

- عمل

- عمل

- پروسیسنگ

- پروفائلنگ

- پروگرام

- پیش رفت

- وعدہ

- ثابت

- فراہم

- تابکاری

- شرح

- قیمتیں

- تناسب

- پڑھیں

- تیاری

- حال ہی میں

- حال ہی میں

- کو کم

- کم

- کم

- کمی

- متعلقہ

- رہے

- کی ضرورت ہے

- قرارداد

- نتیجے

- نتائج کی نمائش

- کا جائزہ لینے کے

- سڑک موڈ

- مضبوط

- کہا

- اسی

- سکیلنگ

- شان

- دیکھنا

- دیکھا

- منتخب

- SELF

- SEM

- نیم

- حساس

- حساسیت

- منتقل

- سے ظاہر ہوا

- دکھایا گیا

- کی طرف

- اشارہ

- اسی طرح

- ایک

- سائز

- ڈھال

- سست

- چھوٹے

- So

- کچھ

- ماخذ

- خلا

- تیزی

- خرچ

- کمرشل

- استحکام

- مستحکم

- مستحکم

- Stacks

- سٹیو

- ابھی تک

- طاقت

- سختی

- مطالعہ

- موضوع

- اس طرح

- کافی

- اعلی

- سطح

- معطل

- میٹھی

- کے نظام

- سسٹمز

- مذاکرات

- تکنیک

- ٹیکنالوجی

- سے

- کہ

- ۔

- بلاک

- ان

- تو

- وہاں.

- یہ

- وہ

- بات

- اس

- اس سال

- ان

- تین

- تھرو پٹ

- وقت

- کرنے کے لئے

- مل کر

- بھی

- کے آلے

- اوزار

- کی طرف

- ٹریک

- کرشن

- تجارت

- روایتی

- دو

- قسم

- حتمی

- کے تحت

- جب تک

- کا استعمال کرتے ہوئے

- استعمال کیا

- استعمال کرنا۔

- مختلف

- بنام

- عمودی

- بہت

- کی طرف سے

- قابل عمل

- نائب صدر

- واٹیٹائل

- تھا

- اچھا ہے

- چلا گیا

- کیا

- جبکہ

- گے

- کھڑکیاں

- ساتھ

- کام

- لکھنا

- تحریری طور پر

- سال

- آپ

- زیفیرنیٹ