حالیہ RISC-V سمٹ میں، آخری سیشن چیپلٹس کے بارے میں ایک پینل بلایا گیا تھا۔ RISC-V ماحولیاتی نظام میں چپلیٹ. اسے RISC-V انٹرنیشنل کے سی ای او کالیسٹا ریڈمنڈ نے ماڈریٹ کیا۔ پینلسٹ تھے:

- لارینٹ مول، آرٹیرس کے سی او او

- انیکیت ساہا، ٹینسٹورینٹ کے پروڈکٹ مینجمنٹ کے VP

- ڈیل گرینلی، وینٹانا مائیکرو سسٹمز کے انجینئرنگ کے VP

- روب آئٹکن، Synopsys کے ممتاز معمار

یہ میرے لیے موضوعات کا تھوڑا سا عجیب مجموعہ ہے۔ ظاہر ہے، آپ RISC-V پروسیسر کو چپلیٹ پر لگا سکتے ہیں لیکن چیلنجز واقعی کسی دوسرے پروسیسر سے مختلف نہیں ہیں۔ لیکن RISC-V گرم ہے اور اسی طرح چپلیٹ بھی ہیں، اور وینٹانا جیسی کمپنیاں ان کو جوڑ رہی ہیں۔

میں آپ کو کمپنیوں کے بارے میں تھوڑا سا پس منظر پیش کرتا ہوں تاکہ انہیں سیاق و سباق میں رکھا جا سکے:

- جیسا کہ آپ شاید جانتے ہوں گے، آرٹیرس نیٹ ورک آن چپ (NoCs) بناتا ہے۔ یہ چپلیٹ وینڈرز (اور آئی پی وینڈرز) کے درمیان ایک غیر جانبدار کمپنی ہے۔

- Tenstorrent انتہائی اعلی کارکردگی والے ملٹی کور RISC-V چپس کا ایک پورٹ فولیو ڈیزائن کر رہا ہے۔

- وینٹانا کے پاس RISC-V IP ہے لیکن یہ اسے چپلیٹ کے طور پر بھی فراہم کرتا ہے۔

- Synopsys ظاہر ہے ایک EDA کمپنی ہے لیکن انہوں نے سمٹ کے شروع میں RISC-V cores کا اعلان کیا تھا۔

]

اصل بحث

Calista سے پہلا سوال ایک سافٹ بال تھا جس میں پوچھا گیا کہ چپلیٹ کی قیمت کیا ہے۔

ڈیل نے کہا کہ چپلیٹ کے لیے RISC-V کے بارے میں کچھ خاص نہیں تھا لیکن مارکیٹ فیصلہ کرتی ہے کہ آپ کب بڑی یک سنگی چیزیں یا چپلیٹ کرتے ہیں۔ یہ اس بات پر منحصر ہے کہ ایک گاہک آپ کو کیا ادائیگی کرے گا۔ "ہم آئی پی اور چپلیٹ دونوں فراہم کرتے ہیں، دونوں کے لیے گنجائش موجود ہے۔"

انیکیت نے کہا کہ "چپلیٹس کرنا سستا نہیں ہے لیکن چپلیٹ کرنا اور RISC-V لچکدار ہے اور آپ تیزی سے تراشنے والی مصنوعات کے ساتھ آ سکتے ہیں۔"

لارینٹ پیداواری لاگت کے لیے چلا گیا۔ NRE کو کنٹرول میں رکھنے کے لیے بہت اہم ہے کیونکہ بہت سے لوگ 100M پرزے نہیں بنا رہے ہیں۔ لہذا اس میں مزید دکاندار شامل ہیں اور ایک پیچیدہ سپلائی چین۔ ایک ایس او سی پیچیدہ ہے لیکن چپلیٹ بدتر ہیں۔

روب نے متفاوتیت کی نشاندہی کی جیسے RF اور ینالاگ کے لیے چپلٹس شامل کرنا، اختیاری ایکسلریٹر رکھنا، وغیرہ۔ یہ ممکنہ طور پر نئی منڈیوں کو کھولتا ہے۔

کالیسٹا نے پوچھا کہ ہم آٹوموٹو میں کہاں ہیں۔

انیکیت نے نشاندہی کی کہ آٹوموٹیو بہت قدامت پسند ہے اور اب وہ ایسے پلیٹ فارمز کے بارے میں جارحانہ ہیں جو کم کاروں سے لے کر ہائی اینڈ کاروں تک پہنچ سکتے ہیں۔ چپلیٹ کے ساتھ، کسی نے واقعی فعال حفاظت پر غور نہیں کیا ہے۔

روب ایرو اسپیس میں گیا (کافی آٹوموٹیو نہیں) اور اس بات پر تبادلہ خیال کیا کہ عام طور پر دہائیوں پہلے طے شدہ جسمانی حجم کی وضاحت کیسے ہوتی ہے۔ چیزوں کو فٹ کرنا مشکل ہے۔

لارنٹ: آٹوموٹو کمپنیاں حتمی کیٹلاگ خریدار ہیں اور چپلیٹ انہیں AI، ریڈار، انفوٹینمنٹ وغیرہ میں بہترین استعمال کرنے دیتی ہیں۔

آپ سافٹ ویئر کو چلانے کے لیے کیسے حاصل کرتے ہیں؟

روب: اگر آپ سسٹم کو چھوٹا بناتے ہیں تو یہ ٹھیک ہے۔ لیکن آٹوموٹو کیٹلاگ کی خریداری اسے مشکل بنا دیتی ہے۔

Aniket: متعلقہ ایک بیان "اگر آپ اسے شامل کرتے ہیں تو ہم اسے استعمال نہیں کریں گے"۔ آٹوموٹیو سافٹ ویئر اسٹیک 5 سالوں میں RISC-V کو سپورٹ کریں گے، جو کہ تیز ہے۔ وہاں پہنچنے میں آرم کو 15 سال لگے۔

سوال: ہمیں کنیکٹیویٹی کے لیے کیا ضرورت ہے؟

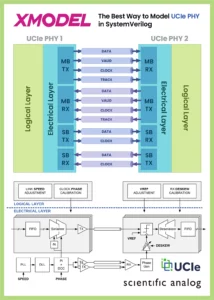

لارینٹ: یہ بہت پیچیدہ ہے خاص طور پر لوگوں کے ساتھ جو چپلٹس کی خریداری کرتے ہیں۔ مختلف دکانداروں کے PHYs، آپس میں کام کرنے کے قابل ہو سکتے ہیں۔ ہر کوئی UCIe کا خواہشمند ہے۔ لوگ ایسے معیارات چاہتے ہیں جو چپلٹس کو بہتر طور پر فٹ کریں۔

انیکیت نے شکایت کی کہ چپلیٹ کے لیے کوئی معیاری ڈیزائن نہیں ہے۔ معیارات کی بڑی کمی۔

روب کا خیال ہے کہ ہم ایک معیاری بہاؤ کے ساتھ آ سکتے ہیں لیکن مختلف چپلیٹ کے ساتھ ہم مختلف ڈیزائن کے بہاؤ کو نہیں چاہتے ہیں۔

سوال: آپ 3-5 سالوں میں چیزیں کہاں دیکھتے ہیں؟

روب: ہم مختلف کے ساتھ ساتھ آگے بڑھیں گے۔

"کیٹلاگ شاپنگ شاید آٹوموٹو OEMs پر منحصر ہے۔ اس میں صنعت کی بہت زیادہ محنت درکار ہوگی۔ کسی بھی متضاد چیز میں زیادہ وقت لگے گا۔

انیکیت نے کہا کہ چپلیٹ پہلے ڈیٹا سینٹر میں ہوں گے اور پھر آٹوموٹو۔ لیکن پہلی لہر سنگل وینڈر ہوگی۔

خلاصہ

یہ ان چیزوں کا مجموعہ ہے جو شرکاء نے کہا اور میری اپنی رائے۔

میرا خیال ہے کہ فی الحال، چپلیٹ پر مبنی RISC-V ڈیزائن ایک کمپنی کی کوشش ہوں گے (سوائے، شاید، ہائی بینڈوڈتھ-میموری (HBM) کے لیے۔ مختلف کمپنیوں، انٹرپوزر کے متعدد چپلیٹ کے ساتھ ڈیزائن بنانا بہت پیچیدہ ہے۔ ، اور ان سب کو جوڑنے کے لیے نیٹ ورک، جسے عام طور پر RDL کہا جاتا ہے۔

مستقبل قریب کے لیے ڈیزائن 2.5D نہیں سچے 3D ہوں گے (جہاں ڈائی ایک دوسرے کے اوپر اسٹیک ہوتے ہیں اور تھرو-سلیکون ویاس یا TSVs کے ساتھ بات چیت کرتے ہیں)۔

آٹوموٹیو کے اپنے چیلنجوں کا ایک سیٹ ہے، خاص طور پر اس بات کو یقینی بنانا کہ چپلیٹ پر مبنی ڈیزائن بہت زیادہ کمپن والے ماحول میں قابل اعتماد ہوں۔ اس کے لیے وسیع پیمانے پر جانچ کی ضرورت ہوگی۔ ایک اور مسئلہ ملٹی ڈائی ماحول میں فعال حفاظت کو یقینی بنانا ہے۔

UCIe امید افزا ہے اور کسی حد تک PCIe پر مبنی ہے۔ PCIe کمپنیوں نے پلگ فیسٹ کے ذریعے قابل اعتمادی کو یقینی بنایا۔ میں نہیں دیکھ رہا ہوں کہ آپ اسی طرح کے میکانزم کے ذریعے چپلیٹ میں UCIe کی انٹرآپریبلٹی کو معاشی طور پر کیسے یقینی بنا سکتے ہیں۔

آخر میں، تکنیکی چیلنجوں کے علاوہ، تجارتی چیلنجز بھی ہیں اگر ہم چپلٹس کو شیلف سے باہر خریدنے اور انہیں مناسب قیمت پر سسٹمز میں جمع کرنے کے قابل ہونے کے نروان کو حاصل کرنا چاہتے ہیں۔ سب سے بڑا چیلنج یہ ہے کہ کون چپلٹس کی انوینٹری کے لیے ادائیگی کرے گا اور اسے رکھے گا۔ اگر تمام چپلیٹس کو آن ڈیمانڈ تیار کرنا ہے تو تیز سائیکل ٹائم کے بہت سے فوائد ضائع ہو جائیں گے۔

لیکن RISC-V چپلیٹ یقینی طور پر ایک ہی کمپنی کے بنائے ہوئے 2.5D انٹرپوزر پر ملٹی ڈائی ڈیزائن کی شکل میں تیزی سے آرہے ہیں۔

بھی پڑھیں:

NoCs آرکیٹیکٹس کو سسٹم میں RISC-V ڈیزائن میں لچک فراہم کرتے ہیں۔

RISC-V cores کو NoCs کے ساتھ جوڑنا SoC پروٹوکول کو آپس میں جوڑتا ہے۔

اس پوسٹ کو بذریعہ شیئر کریں:

- SEO سے چلنے والا مواد اور PR کی تقسیم۔ آج ہی بڑھا دیں۔

- پلیٹو ڈیٹا ڈاٹ نیٹ ورک ورٹیکل جنریٹو اے آئی۔ اپنے آپ کو بااختیار بنائیں۔ یہاں تک رسائی حاصل کریں۔

- پلیٹوآئ اسٹریم۔ ویب 3 انٹیلی جنس۔ علم میں اضافہ۔ یہاں تک رسائی حاصل کریں۔

- پلیٹو ای ایس جی۔ کاربن، کلین ٹیک، توانائی ، ماحولیات، شمسی، ویسٹ مینجمنٹ یہاں تک رسائی حاصل کریں۔

- پلیٹو ہیلتھ۔ بائیوٹیک اینڈ کلینیکل ٹرائلز انٹیلی جنس۔ یہاں تک رسائی حاصل کریں۔

- ماخذ: https://semiwiki.com/ip/arteris/338888-risc-v-and-chiplets-a-panel-discussion/

- : ہے

- : ہے

- : نہیں

- :کہاں

- $UP

- 100M

- 15 سال

- 15٪

- 167

- 200

- 300

- 3d

- a

- قابلیت

- ہمارے بارے میں

- مسرع

- اصل

- شامل کریں

- انہوں نے مزید کہا

- اس کے علاوہ

- فوائد

- ایرواسپیس

- جارحانہ

- پہلے

- AI

- تمام

- ساتھ

- بھی

- کے درمیان

- an

- اور

- کا اعلان کیا ہے

- ایک اور

- کوئی بھی

- آرکیٹیکٹس

- کیا

- بازو

- ارد گرد

- AS

- پوچھنا

- سے پوچھ

- At

- آٹوموٹو

- پس منظر

- کی بنیاد پر

- BE

- کیا جا رہا ہے

- BEST

- بہتر

- بگ

- سب سے بڑا

- بٹ

- دونوں

- تعمیر

- عمارت

- تعمیر

- لیکن

- by

- کہا جاتا ہے

- کر سکتے ہیں

- کاریں

- کیٹلوگ

- سی ای او

- یقینی طور پر

- چین

- چیلنج

- چیلنجوں

- سستے

- رنگ

- مجموعہ

- امتزاج

- کس طرح

- آنے والے

- تجارتی

- ابلاغ

- کمپنیاں

- کمپنی کے

- پیچیدہ

- پیچیدہ

- رابطہ قائم کریں

- رابطہ

- قدامت پرستی

- سمجھا

- سیاق و سباق

- کنٹرول

- coo

- قیمت

- اخراجات

- گاہک

- سائیکل

- ڈیٹا سنٹر

- دہائیوں

- کی وضاحت

- فراہم کرتا ہے

- منحصر ہے

- انحصار کرتا ہے

- ڈیزائن

- ڈیزائننگ

- ڈیزائن

- مر

- مختلف

- بات چیت

- بحث

- جانبدار

- do

- کر

- نہیں

- ہر ایک

- اس سے قبل

- کوشش

- آخر

- انجنیئرنگ

- کو یقینی بنانے کے

- اس بات کا یقین

- کو یقینی بنانے ہے

- ماحولیات

- خاص طور پر

- سب

- اس کے علاوہ

- وسیع

- فاسٹ

- آخر

- پہلا

- فٹ

- مقرر

- لچک

- لچکدار

- بہاؤ

- بہنا

- کے لئے

- متوقع

- فارم

- سے

- فنکشنل

- مزید

- مستقبل

- حاصل

- دے دو

- ہارڈ

- مشکل

- ہے

- ہونے

- ہائی

- اعلی کارکردگی

- پکڑو

- HOT

- کس طرح

- HTTPS

- i

- if

- اہم

- in

- صنعت

- بین الاقوامی سطح پر

- انٹرویوبلائٹی

- انٹرپرائز

- میں

- انوینٹری

- ملوث

- IP

- مسئلہ

- IT

- میں

- فوٹو

- Keen

- رکھیں

- جان

- جانا جاتا ہے

- نہیں

- آخری

- دو

- کی طرح

- اب

- کھو

- بہت

- لو

- بنا

- بناتا ہے

- انتظام

- تیار

- بہت سے

- بہت سے لوگ

- مارکیٹ

- Markets

- زیادہ سے زیادہ چوڑائی

- مئی..

- شاید

- me

- میکانزم

- یادگار

- زیادہ

- ایک سے زیادہ

- my

- ضرورت ہے

- نیٹ ورک

- غیر جانبدار

- نئی

- نہیں

- کچھ بھی نہیں

- اب

- of

- on

- ڈیمانڈ

- ایک

- کھولتا ہے

- رائے

- or

- دیگر

- باہر

- خود

- پینل

- پینل ڈسکشن

- امیدوار

- خاص طور پر

- حصے

- ادا

- لوگ

- شاید

- جسمانی

- پلیٹ فارم

- پلاٹا

- افلاطون ڈیٹا انٹیلی جنس

- پلیٹو ڈیٹا

- پورٹ فولیو

- پوسٹ

- ممکنہ طور پر

- شاید

- پروسیسر

- مصنوعات

- پروڈکٹ مینجمنٹ

- پیداوار

- حاصل

- وعدہ

- پروٹوکول

- فراہم

- خرید

- ڈال

- سوال

- بہت

- ریڈار

- پڑھیں

- واقعی

- مناسب

- حال ہی میں

- متعلقہ

- وشوسنییتا

- قابل اعتماد

- کی ضرورت

- کمرہ

- رن

- سیفٹی

- کہا

- پیمانے

- دیکھنا

- اجلاس

- مقرر

- خریدار

- خریداری

- اسی طرح

- بعد

- ایک

- چھوٹے

- So

- سافٹ ویئر کی

- کچھ بھی نہیں

- مخصوص

- سجا دیئے

- Stacks

- معیار

- معیار

- بیان

- سربراہی کانفرنس

- فراہمی

- فراہمی کا سلسلہ

- حمایت

- کے نظام

- سسٹمز

- لے لو

- بات کر

- ٹیکنیکل

- ٹیسٹنگ

- کہ

- ۔

- ان

- تو

- وہاں.

- وہ

- چیزیں

- لگتا ہے کہ

- سوچتا ہے

- اس

- کے ذریعے

- تعلقات

- وقت

- کرنے کے لئے

- بھی

- لیا

- سب سے اوپر

- موضوعات

- سچ

- حتمی

- کے تحت

- اپ ڈیٹ کریں

- استعمال کی شرائط

- عام طور پر

- قیمت

- وینڈر

- دکانداروں

- بہت

- کی طرف سے

- حجم

- vp

- چاہتے ہیں

- تھا

- لہر

- we

- چلا گیا

- تھے

- کیا

- جب

- جس

- ڈبلیو

- گے

- ساتھ

- بدتر

- سال

- آپ

- زیفیرنیٹ