سیمی کنڈکٹر انجینئرنگ نے پروڈکٹ مینجمنٹ کے گروپ ڈائریکٹر پیٹ ہارڈی کے ساتھ RISC-V پروسیسرز کی تصدیق پر بات چیت کی۔ Cadence سے; مائیک ایفٹیماکس، نائب صدر برائے حکمت عملی اور ماحولیاتی نظام کوڈاسپ; سائمن ڈیوڈ مین، بانی اور سی ای او امپیرا سافٹ ویئر; Sven Beyer، پروسیسر کی تصدیق کے لیے پروگرام مینیجر سیمنز ای ڈی اے۔; کرن وٹل، الائنس پارٹنر مارکیٹنگ کے سینئر ڈائریکٹر Synopsys; ڈیو کیلف، بریکر ویریفیکیشن کے سی ای او، اور ویوسافٹ کارپوریشن کے صدر اور سی ٹی او ہیو ٹران۔ اس گفتگو کے اقتباسات درج ذیل ہیں۔ اس بحث کا ایک حصہ دیکھنے کے لیے، یہاں کلک کریں۔

SE: RISC-V تصدیق کا بہاؤ کیسا لگتا ہے؟

کیلف: ہم پروسیسرز کی تصدیق کو سرگرمیوں کے اسٹیک کے طور پر دیکھتے ہیں، لیکن اس اسٹیک میں بہت سارے لوپ بیکس ہیں۔ بہت ساری کمپنیاں ISA کے ساتھ مطابقت کو ایک الگ سرگرمی سمجھتی ہیں۔ وہ پہلے اسٹیک کے طور پر 'ہیلو ورلڈ' ٹیسٹ کریں گے تاکہ یہ یقینی بنایا جا سکے کہ چیزیں ٹھیک اور چل رہی ہیں، پھر وہ جتنے کنفارمنس ٹیسٹ کر سکتے ہیں چلائیں گے۔ وہ کوشش کرتے ہیں اور ISA سے میچ کرتے ہیں، اور پھر وہ مائیکرو فن تعمیر کی جانچ شروع کرتے ہیں۔ بہت سے لوگ وہاں رک جاتے ہیں۔ جو کچھ ہم دیکھتے ہیں وہ یہ ہے کہ جب وہ کنفارمنس ٹیسٹ چلاتے ہیں، تو وہ موافقت حاصل کرتے دکھائی دے سکتے ہیں، اور پھر وہ مائیکرو آرکیٹیکچر ٹیسٹ لکھنا شروع کر دیتے ہیں، کچھ ایسی چیزیں ڈھونڈتے ہیں جو ٹوٹی ہوئی ہیں اور محسوس کرتے ہیں کہ ISA کے مطابق ہونا محض بنانے سے کہیں زیادہ پیچیدہ ہے۔ یقینی بنائیں کہ ہدایات صحیح طریقے سے چل رہی ہیں۔ جیسے ہی وہ اسٹیک میں مزید اوپر جاتے ہیں، وہ داخل ہوتے ہیں، 'کیا ہم کور کی تصدیق کر سکتے ہیں کیونکہ وہ باقی سسٹم سے متعلق ہیں؟ کیا ہم اس پر OS بوٹ کر سکتے ہیں؟ کیا اس میں ضروری کارکردگی ہے؟ کیا وہ اس بات کو یقینی بنانے کے لیے ڈیزائن کی پروفائل کر سکتے ہیں کہ کارکردگی درست ہے اور تصدیق میں مزید کیڑے ظاہر کرنے کے لیے وہ توثیق کی سرگرمیاں شروع کر سکتے ہیں؟' جب ہم ایک ریگولر ASIC یا ریگولر کور کی جانچ کر رہے ہوتے ہیں، تو آپ تمام تصدیقی سرگرمیوں کو چلا سکتے ہیں، واقعی اچھی کوریج حاصل کر سکتے ہیں، اور پھر آخر میں توثیق کر سکتے ہیں۔ آپ کو اکثر تصدیق پر واپس جانے کی ضرورت نہیں ہے۔ ان پروسیسرز کے ساتھ، آپ کرتے ہیں. آپ کو ہر وقت اس تصدیقی اسٹیک کے ذریعے پیچھے اور آگے جانا ہوگا۔ یہ واقعی آپ کو سست کر دیتا ہے، اور اس فن تعمیر کی پوری تصدیق۔ سنہری حوالہ ماڈل انتہائی اہم ہوتا جا رہا ہے۔ Imperas ماڈلز کو بہت سارے لوگ جدید ترین انڈسٹری کے معیاری ماڈل کے طور پر تسلیم کرتے ہیں۔ ہم ان ماڈلز کے ساتھ کام کر رہے ہیں۔ واقعی ایک ٹھوس بنیادی حوالہ ماڈل لانا جس پر آپ بھروسہ کر سکتے ہیں ایک اہم چیز بنتی جا رہی ہے۔ آپ مائیکرو آرکیٹیکچر کی جانچ کر سکتے ہیں، آپ اس بنیادی ماڈل کے خلاف سسٹم کے باقی حصوں کے ساتھ کچھ تعامل کی جانچ کر سکتے ہیں، اور اصل پروسیسر میں کیا ہو رہا ہے اس کی واضح تصویر حاصل کر سکتے ہیں۔

Tran میں: مجھے اس بارے میں کچھ شک ہے کہ آیا RISC-V کی بات کرنے پر سنہری حوالہ ماڈل کا خیال قابل عمل ہے۔ اگر آپ اس دن پر واپس جائیں جب یونکس منظر عام پر آیا تھا، وہاں مٹھی بھر سپلائرز تھے جن کے اپنے نفاذ تھے۔ آپ کے پاس سولاریس، SVR4، IBM سے AIX وغیرہ تھے۔ ان تمام مختلف یونکس/لینکس کے نفاذ سے، ایک عام قابل عمل کو حاصل کرنے کا خیال جو پورے بورڈ میں چل سکتا ہے، ممکن نہیں تھا۔ ہر وینڈر کو ویلیو ایڈ اور کسٹم ایکسٹینشنز بنانے کی ترغیب دی جاتی ہے جو انہیں دوسرے کے مقابلے میں تفریق فراہم کرے گی۔ ہم اسے یہاں RISC-V کے ساتھ دیکھتے ہیں۔ x86 اور بازو کے ساتھ برعکس، جہاں زیادہ تر نفاذ Intel یا Arm چھتری کے تحت ہوتے ہیں، آپ کے پاس لفظی طور پر سینکڑوں مختلف ادارے اور تنظیمیں ہیں جو اپنے RISC-V کے نفاذ کو تیار کر رہے ہیں۔ جب آپ ویکٹر ایکسٹینشن جیسی چیزوں کے بارے میں بات کرتے ہیں، جہاں قیاس اتنا بڑا ہے، بہت سے نافذ کرنے والوں نے اس ایکسٹینشن کے صرف ایک ذیلی سیٹ کو نافذ کرنے کا فیصلہ کیا ہے۔ آپ اس طرح کے نفاذ کے خلاف عمل درآمد کی تصدیق کرنے کے لیے ایک عام سنہری حوالہ ماڈل کیسے بنا سکیں گے؟ دوسرا، جب ہم عملدرآمد کی تصدیق اور توثیق کے بارے میں بات کرتے ہیں، تو آپ کو ٹول چین اور آپریٹنگ سسٹم میں اسٹیک کو مزید اوپر جانا ہوگا۔ مثال کے طور پر، ویکٹر ایکسٹینشن کو لے لیں۔ ہر وینڈر جس سے میں نے بات کی ہے، اور اس کے ساتھ کام کیا ہے، اس کا اپنا کمپائلر ہے، ان کے ویکٹر ایکسٹینشن کی حمایت میں ان کا اپنا LLVM نفاذ ہے۔ اور ان میں سے کوئی بھی دوسرے کے ساتھ مطابقت نہیں رکھتا۔ لہذا آپ وینڈر A سے LLVM کمپائلر لے سکتے ہیں، کوڈ تیار کر سکتے ہیں، اور یہ وینڈر B سے عمل درآمد کے لیے زیادہ کارآمد نہیں ہوگا۔ اس نقطہ نظر سے، مجھے شک ہے کہ آیا ایک عام ماڈل کے ساتھ آنا بھی ممکن ہے یا نہیں۔ آپ کو ان تغیرات کے خلاف ایک بنیادی لائن دے سکتا ہے۔

ڈیوڈ مین: میں اس تبصرہ سے واضح طور پر متفق نہیں ہوں۔ RISC-V ایک مکمل ڈراؤنا خواب ہے کیونکہ بہت سارے اختیارات ہیں۔ یہ مطابقت اور تعمیل کے لیے چیلنجوں میں سے ایک ہے۔ بہت سارے کنفیگریشن آپشنز ہیں، جو کہ تمام قانونی ہیں، اور بڑا سوال یہ ہے کہ آپ ریفرنس ماڈل کیسے بناتے ہیں؟ لیکن یہ اس سے بھی بدتر ہے۔ ہر تین ماہ بعد، ہر ایکسٹینشن کا ایک نیا ورژن ہوتا ہے۔ ہمارے سمیلیٹر میں، یہ ایک مکمل حوالہ ہے۔ یہ کسی بھی آزاد ذیلی سیٹ کے لیے مکمل طور پر قابل ترتیب ہے، بلکہ ورژن بھی۔ ہمارے پاس ویکٹر کے 11 ورژن ہیں، جن میں سے 4 سلیکون میں چلے گئے ہیں۔ مجھے نہیں لگتا کہ اس میں کوئی مسئلہ ہے، جب تک کہ اسے صحیح طریقے سے ڈیزائن اور تعمیر کیا گیا ہو۔ RISC-V چیزوں کو بہتر طریقے سے کرنے کا موقع فراہم کرتا ہے۔ ہم صرف ایک بازو یا ایک انٹیل رکھنے کے پرانے طریقے کے ساتھ نہیں رہ سکتے۔ یہ کام نہیں کرنے والا ہے۔ اگر پرانی دنیا تھی تو آپ کے پاس ایک حوالہ ماڈل ہوسکتا ہے جو ایک کام کرتا ہے، نئی دنیا یہ ہے کہ آپ کے پاس ایک حوالہ ماڈل ہے جو 100 چیزیں کرسکتا ہے۔ اور یہ وہ جگہ ہے جہاں ہم جا رہے ہیں۔ بصورت دیگر، RISC-V کبھی بھی اپنی تقدیر کو پورا نہیں کرے گا۔ ہمیں ان مسائل کو حل کرنا ہے۔

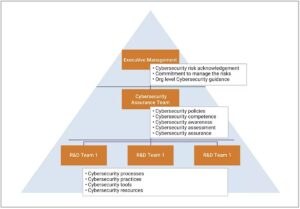

ہردی: ہم پروسیسر کے نفاذ کو جانتے ہیں اور شیطان تفصیلات میں ہے۔ ہم یقینی طور پر آپ سے متفق ہیں کہ سسٹم ویریلوگ، ویریلوگ، ان نفاذ کی تفصیلات کو حاصل کرنے میں بہت بہتر ہے۔ لیکن آپ کو اس عمل کی تصدیق ایک اعلیٰ سطحی ماڈل کے خلاف کرنی ہوگی جو ارادے کو حاصل کر رہا ہے۔ یہ ایک واحد حوالہ ماڈل نہیں ہے۔ یہ بہت سے ہو سکتے ہیں، یا ان متعدد اقسام کے لیے حوالہ ماڈل بنانے کا ایک معیاری طریقہ جن کے بارے میں ہم بات کر رہے ہیں۔

ڈیوڈ مین: پانچ یا چھ سال پہلے، میں RISC-V بین الاقوامی تنظیم کا حصہ تھا جس نے رسمی طور پر دیکھا اور سنہری حوالہ ماڈل بنانے کے لیے SAIL کو زبان کے طور پر منتخب کیا۔ ہمیں جو غلطی ہوئی وہ یہ ہے کہ SAIL بہت قابل ترتیب نہیں ہے۔ یہ ایک فن تعمیر کے لیے بہت اچھا ہے۔ بازو کے لیے، یہ لاجواب ہے۔ ان کے پاس یہ سارا بہاؤ ایک تعریف سے ہے، صحیح بہ تعمیر کے ذریعے، تمام راستے نیچے، رسمی وضاحت سے آتا ہے، اور یہ شاندار ہے۔ RISC-V کے لیے چیلنج یہ ہے کہ اس میں ڈیزائن کے لحاظ سے یہ لامحدود ترتیب ہے۔ اور اس طرح سیل میں اس کی ماڈلنگ میں ایک حقیقی چیلنج ہے۔ یہی وجہ ہے کہ Imperas ایک متحرک ماڈل کے لیے گئے تھے۔

وٹل: RISC-V کو وہاں کی تقریباً ہر کمپنی اپنا رہی ہے۔ یہاں تک کہ معروف سیمی کنڈکٹر فروش بھی RISC-V ڈیزائن کر رہے ہیں، جیسا کہ بہت سے سٹارٹ اپ ہیں۔ لیکن کلید ایک کامیاب تصدیقی منصوبہ حاصل کرنے کے قابل ہونا ہے جہاں آپ کے پاس اپنے کوریج کے اہداف کو حاصل کرنے کے لیے بہت اعلیٰ معیار کا محرک ہے۔ تصدیق اور ڈیبگ دونوں ساتھ ساتھ چلتے ہیں۔ ہارڈ ویئر/سافٹ ویئر ڈیبگ، مسائل کو بیک وقت دیکھنے کے لیے کوڈ کے ذریعے قدم بڑھانا، کلیدی حیثیت رکھتا ہے۔ فن تعمیر کی لچک کی طرف واپس جانا، یہ چیلنجز فراہم کر رہا ہے - اور جہاں موقع ہم سب کے لیے ہے۔ جدید حل تیار کیے جا رہے ہیں۔ RISC-V وینڈرز اور EDA ٹول کمپنیوں کے ساتھ ساتھ دیگر EDA شراکت داروں اور اسی طرح کے درمیان بہت زیادہ تعاون ہو رہا ہے۔

کیلف: ایسی کمپنیاں ہیں جنہوں نے ایک حد تک اس کا پتہ لگایا ہے۔ RISC-V کی لامحدود ترتیب، یہ تمام چیزیں درست ہیں۔ لیکن دن کے اختتام پر، آرم اور انٹیل نے اپنے کسی حد تک کم قابل ترتیب پروسیسرز کی تصدیق کو حل کر دیا ہے۔ ان میں ایک بہاؤ، یا پیچیدہ بہاؤ کا ایک سلسلہ ہے، اور ان بہاؤ میں مختلف سرگرمیوں کا ایک گروپ شامل ہے۔ بازو بہت سارے رسمی اوزار استعمال کرتا ہے، اسے کرنے کے لیے بہت سی مختلف چیزیں۔ شروع کرنے کے لئے ایک اچھی جگہ یہ دیکھ رہی ہے کہ ان میں سے کچھ لوگ اپنے بہاؤ میں کیا کر رہے ہیں، اور اس میں سے کچھ کو خودکار کرنے کی کوشش کر رہے ہیں۔ آپ کو ایک ایسی چیز کی ضرورت ہے جو RISC-V پروسیسر کرنے کی کوشش کرنے والے تمام لوگ استعمال کر سکیں اور ایک ساتھ تعاون کر رہے ہوں — ان مزید عمومی بہاؤ کو سامنے لانے کے لیے تعاون کریں، اور دیکھیں کہ کیا ہم اس میں سے کچھ چیزوں کو معیاری بنا سکتے ہیں۔ اور ایک مناسب معیار کے معنی میں نہیں، بلکہ RISC-V پروسیسرز کی تصدیق کرنے کا ایک حقیقی معیاری طریقہ جو پوری صنعت میں کام کرتا ہے اور کچھ حقیقی مطابقت پیدا کرتا ہے، نہ کہ صرف ہدایات کے مطابق مطابقت رکھتا ہے۔

SE: آپ میں سے ایک جوڑے نے ذکر کیا ہے کہ ہمیں نئے آلات، نئے بہاؤ کی ضرورت ہے۔ آج کس چیز کی کمی ہے؟ ہم کس طرح کام کرنے جا رہے ہیں کہ وہ کون سی چیزیں ہیں جو کسی کو فراہم کرنے کی ضرورت ہے؟

کیلف: بہت سارے لوگ اندرونی طور پر RISC-V پروسیسر کر رہے ہیں، اور وہ نئے سرے سے شروع کر رہے ہیں۔ وہ پروسیسر کی توثیق کرنے کا طریقہ سیکھ رہے ہیں۔ Codasip جیسی کمپنیاں آرم اور انٹیل اور دیگر جیسی جگہوں سے بہت سارے تجربے اور مہارت کے حامل لوگوں کو لاتی ہیں، جو سمجھتے ہیں کہ کیا کرنا ہے۔ لہذا ہم دیکھتے ہیں کہ ان میں سے کچھ کمپنیاں اب بہاؤ پیدا کر رہی ہیں جہاں وہ مسائل پر غور کر رہی ہیں جیسے، 'کیا پروسیسر مکمل ہم آہنگی کی حمایت کر سکتا ہے؟ کیا یہ پورے سسٹم میں کام کرتا ہے؟ کیا RISC-V کے اندر PMP (فزیکل میموری پروٹیکشن) جیسی حفاظتی ہدایات صحیح طریقے سے کام کر سکتی ہیں؟'

ڈیوڈ مین: جب ہم نے RISC-V کے ساتھ پانچ یا چھ سال پہلے آغاز کیا تھا، تو RISC-V کے لیے کچھ خاص نہیں تھا۔ ہمارے پاس ویریلوگ سمیلیٹر تھا، آپ کے پاس کچھ رسمی چیزیں تھیں، آپ کچھ خصوصیات لکھ سکتے تھے۔ وہاں GCC تھا، اور آپ اسے چلا سکتے ہیں اور اسے ڈیبگ کر سکتے ہیں۔ بس یہی تھا. ہم نے پچھلے پانچ سالوں میں جو کچھ دیکھا ہے وہ یہ ہے کہ لوگوں نے بہت سارے ٹولز اور ٹکنالوجی تیار کی ہے، جو یہ سیکھ کر حاصل کی گئی ہے کہ پروسیسرز کی ملکیتی طریقوں سے تصدیق کیسے کی جاتی ہے۔ اور ہم اسے مزید عام کرنے کی کوشش کر رہے ہیں۔ ہم یہ سمجھنے کی کوشش کر رہے ہیں کہ یہ انٹیل اور آرم میں کیسے کیا گیا ہے، اور ٹیکنالوجیز کی اقسام جو استعمال کی گئی ہیں۔ ہم OpenHW کے اندر کام کر رہے ہیں، جہاں میں تصدیق کے کام کو دیکھتا ہوں۔ یہ صنعتی معیار کے ساتھ اوپن سورس سلکان کے بارے میں ہے۔ یہ اوپن سورس ٹولز کے استعمال کے بارے میں نہیں ہے۔ ہم نے پچھلے کچھ سالوں میں جو کچھ سیکھا ہے وہ بہت سی مختلف تکنیکیں ہیں، کام کرنے کے بہت سے مختلف طریقے ہیں، اور ہم نے اس کنفیگر ایبل حوالہ ماڈل کی طرح ٹولز تیار اور بنائے ہیں، جیسے ٹیکنالوجی جو آپ کی تصدیق کرتی ہے، جیسے فنکشنل کوریج جسے ہم چیک کرنے کے طریقوں میں تیار کر رہے ہیں کہ لینکس کتنی اچھی طرح سے چلتا ہے۔ لوگ ٹیسٹ جنریٹر بنا رہے ہیں۔ دوسری کمپنیاں رسمی ٹولز بنا رہی ہیں، جیسے کہ سیمنز سے باہر OneSpin ٹیکنالوجیز جو RISC-V پر مرکوز ہیں۔ تین یا چار دیگر کمپنیاں ہیں جو چیزوں کے باضابطہ پہلو میں شامل ہیں۔ ہم جو دیکھ رہے ہیں وہ یہ ہے کہ کچھ مخصوص RISC-V ٹیکنالوجیز بنائی جا رہی ہیں، کچھ توثیقی IPs بنائے جا رہے ہیں، اور زیادہ سے زیادہ، EDA وینڈرز لوگوں کو درکار طریقہ کار سیکھ رہے ہیں، اور وہ ٹولز بنا رہے ہیں۔ لیکن یہ ابتدائی دن ہے۔ ہم RISC-V کے حقیقی استعمال میں صرف پانچ سال ہیں، اور شاید اس کے تجارتی حصے میں چند سال باقی ہیں۔ اس سے پہلے پانچ سال کی تعلیمی چیزیں تھیں۔ اور Codasip جیسی کمپنیاں، اور سلیکون آئی پی کے دیگر تجارتی وینڈرز، تصدیق کے لیے اندرونی طور پر ٹیکنالوجیز کو تیار اور تیار کر رہے ہیں۔ ہم انہیں تجارتی ٹولز کے طور پر بنانے میں مدد کرنے کی کوشش کر رہے ہیں، جیسا کہ کچھ EDA وینڈرز ہیں۔ ہم RISC-V تصدیقی ٹیکنالوجیز کے اس نئے دور کے آغاز میں ہیں۔

وٹل: مین اسٹریم پروسیسر کے ڈویلپرز جانتے ہیں کہ وہ کیا کر رہے ہیں۔ انہوں نے پہلے بھی x86 اور آرم کیا ہے۔ وہ RISC-V کو اپنا رہے ہیں اور وہ بخوبی جانتے ہیں کہ کیا کرنا ہے۔ وہ اوپن سورس کمیونٹی کا بھی فائدہ اٹھا رہے ہیں۔ مرکزی دھارے کے لیے، جب آپ RISC-V کو دیکھتے ہیں، تو اسے مرکزی دھارے کے ڈیزائنرز نے اپنایا ہے۔ وہیں انہیں طریقہ کار کی ضرورت ہے۔ یہی غائب ہے۔ Synopsys ہر وہ چیز پیش کرتا ہے جو تصدیق اور توثیق کرنے کے لیے درکار ہے، دونوں سافٹ ویئر اور ہارڈ ویئر۔ ہمارے پاس وی آئی پیز ہیں، ہمارے پاس رسمی تکنیک ہے، ہمارے پاس ڈیٹا پاتھ ہے، لیکن جو غائب ہے وہ ایک طریقہ کار ہے۔ اور طریقہ کار پروسیسر کی تصدیق کے انجینئر اور دیگر ماہرین کی مہارت کے ساتھ آتا ہے۔

Eftimakis: یہ آئی پی فروشوں کی خفیہ چٹنی ہے۔ ہم اندرونی طور پر یہی کرتے ہیں۔

ڈیوڈ مین: امپیرا جیسی کمپنیاں اسے مزید عوامی بنانے کی کوشش کر رہی ہیں۔ یہ پہلے ملکیتی IP ہو سکتا ہے۔ ہم RISC-V پروسیسر کی تصدیق کے حوالہ کے بہاؤ پر 90 منٹ کا سبق دیتے ہیں۔ یہ آپ کو درکار تمام مختلف بٹس کو بتاتا ہے، اور آج کون سی ٹیکنالوجیز دستیاب ہیں اور کون سی دستیاب نہیں ہے۔ ہم تجارتی ٹکنالوجی پر مبنی ٹیسٹ جنریٹرز کے بارے میں بات کرتے ہیں۔

وٹل: ہمارے پاس ایک ایسی ہی چیز ہے جسے کک بک کہا جاتا ہے، جسے ہمارے صارفین پورٹل سے ڈاؤن لوڈ کر سکتے ہیں جو اوپن سورس کور استعمال کرتا ہے۔ یہ آپ کو تصدیق کے پورے عمل سے گزر سکتا ہے۔

Beyer کی: نئی ٹولنگ کو شامل کرنا اہم ہے، لیکن ہمیں انتہائی قابل ترتیب RISC-V حوالہ ماڈل کی ضرورت ہے، اور اسے ٹولنگ اور بہاؤ کے لیے دستیاب کرانا ہے۔ پھر ہم اس کے ارد گرد کچھ بنا سکتے ہیں تاکہ گہرے تجربے کے بغیر لوگ RISC-V cores کے لیے تصدیقی تجربہ حاصل کر سکیں۔

Eftimakis: ہم نے اپنے بہاؤ میں ٹولز کو ضم کیا ہے، بشمول Imperas اور OneSpin۔ یہ وہ چیز ہے جسے ہم RISC-V کا حصہ بننے کے فائدے کے طور پر دیکھتے ہیں، کیونکہ ہم ان ٹولز کا فائدہ اٹھا سکتے ہیں جو ماحولیاتی نظام کے لیے بنائے گئے ہیں اور انہیں اپنے تصدیقی بہاؤ میں ضم کر سکتے ہیں۔ ہم ماڈلز، سمیلیشنز، رسمی تصدیق، دعوے وغیرہ کے ساتھ موازنہ کو یکجا کر سکتے ہیں۔ یہ ایک فائدہ ہے جو ہمیں اس ماحولیاتی نظام کا حصہ بننے سے حاصل ہوا ہے۔

- SEO سے چلنے والا مواد اور PR کی تقسیم۔ آج ہی بڑھا دیں۔

- پلیٹو بلاک چین۔ Web3 Metaverse Intelligence. علم میں اضافہ۔ یہاں تک رسائی حاصل کریں۔

- ماخذ: https://semiengineering.com/do-necessary-tools-exist-for-risc-v-verification/

- : ہے

- $UP

- 100

- 11

- a

- قابلیت

- ہمارے بارے میں

- تعلیمی

- حاصل

- حصول

- کے پار

- سرگرمیوں

- سرگرمی

- اپنایا

- اپنانے

- کے بعد

- کے خلاف

- تمام

- اور

- ظاہر

- فن تعمیر

- کیا

- بازو

- ارد گرد

- AS

- asic

- At

- خود کار طریقے سے

- دستیاب

- واپس

- کی بنیاد پر

- بیس لائن

- BE

- کیونکہ

- بننے

- اس سے پہلے

- شروع

- کیا جا رہا ہے

- فائدہ

- بہتر

- کے درمیان

- بگ

- بٹ

- بورڈ

- شاندار

- آ رہا ہے

- ٹوٹ

- لایا

- کیڑوں

- تعمیر

- عمارت

- تعمیر

- گچرچھا

- by

- کہا جاتا ہے

- کر سکتے ہیں

- حاصل کر سکتے ہیں

- گرفتاری

- سی ای او

- کچھ

- یقینی طور پر

- چین

- چیلنج

- چیلنجوں

- چیک کریں

- منتخب کریں

- واضح

- واضح طور پر

- کلک کریں

- کوڈ

- تعاون

- تعاون

- جمع

- کس طرح

- آنے والے

- تبصرہ

- تجارتی

- کامن

- کمیونٹی

- کمپنیاں

- کمپنی کے

- موازنہ

- مطابقت

- ہم آہنگ

- مکمل

- مکمل طور پر

- پیچیدہ

- تعمیل

- ترتیب

- پر غور

- بات چیت

- کور

- کارپوریشن

- سکتا ہے

- جوڑے

- کوریج

- تخلیق

- پیدا

- تخلیق

- اہم

- CTO

- اپنی مرضی کے

- گاہکوں

- اعداد و شمار

- ڈیو

- دن

- دن

- فیصلہ کیا

- گہری

- اخذ کردہ

- تفصیل

- ڈیزائن

- ڈیزائن

- ڈیزائنرز

- ڈیزائن

- تفصیلات

- ترقی یافتہ

- ڈویلپرز

- مختلف

- ڈائریکٹر

- بات چیت

- بحث

- کر

- نہیں

- شک

- نیچے

- ڈاؤن لوڈ، اتارنا

- متحرک

- ہر ایک

- ابتدائی

- ماحول

- ہنر

- انجینئر

- انجنیئرنگ

- وغیرہ

- بھی

- ہر کوئی

- سب کچھ

- وضع

- تیار ہوتا ہے

- بالکل

- پھانسی

- تجربہ

- مہارت

- ماہرین

- مدت ملازمت میں توسیع

- ملانے

- بہت اچھا

- چند

- سمجھا

- مل

- پہلا

- لچک

- بہاؤ

- بہنا

- توجہ مرکوز

- مندرجہ ذیل ہے

- کے لئے

- رسمی طور پر

- آگے

- بانی

- بانی اور سی ای او

- سے

- پورا کریں

- مکمل

- فنکشنل

- مزید

- جی سی سی

- پیدا

- جنریٹر

- حاصل

- حاصل کرنے

- دے دو

- Go

- جا

- گولڈن

- اچھا

- عظیم

- گروپ

- ہاتھ

- مٹھی بھر

- ہو

- ہو رہا ہے۔

- ہارڈ ویئر

- ہے

- ہونے

- مدد

- یہاں

- اعلی معیار کی

- کس طرح

- کیسے

- HTTPS

- سینکڑوں

- i

- IBM

- خیال

- پر عملدرآمد

- نفاذ

- اہم

- in

- حوصلہ افزائی

- شامل

- سمیت

- آزاد

- صنعتی

- صنعت

- جدید

- مثال کے طور پر

- اداروں

- ہدایات

- ضم

- ضم

- انٹیل

- ارادے

- بات چیت

- اندرونی طور پر

- بین الاقوامی سطح پر

- ملوث

- IP

- مسائل

- IT

- میں

- فوٹو

- صرف ایک

- کلیدی

- جان

- زبان

- بڑے

- آخری

- رکھتا ہے

- معروف

- سیکھا ہے

- سیکھنے

- قانونی

- لیوریج

- لیورنگنگ

- کی طرح

- لینکس

- رہتے ہیں

- لانگ

- دیکھو

- کی طرح دیکھو

- دیکھا

- تلاش

- بہت

- مین سٹریم میں

- اکثریت

- بنا

- بنانا

- انتظام

- مینیجر

- بہت سے

- مارکیٹنگ

- میچ

- یاد داشت

- ذکر کیا

- طریقوں

- طریقہ کار

- شاید

- لاپتہ

- ماڈل

- ماڈلنگ

- ماڈل

- ماہ

- زیادہ

- ضروری

- ضرورت ہے

- ضروریات

- نئی

- of

- تجویز

- پرانا

- on

- ایک

- اوپن سورس

- کام

- کام

- آپریٹنگ سسٹم

- مواقع

- آپشنز کے بھی

- تنظیم

- OS

- دیگر

- دیگر

- دوسری صورت میں

- خود

- حصہ

- پارٹنر

- شراکت داروں کے

- راستہ

- لوگ

- کارکردگی

- نقطہ نظر

- جسمانی

- تصویر

- مقام

- مقامات

- منصوبہ

- پلاٹا

- افلاطون ڈیٹا انٹیلی جنس

- پلیٹو ڈیٹا

- پوائنٹ

- پورٹل

- ممکن

- صدر

- شاید

- مسئلہ

- مسائل

- عمل

- پروسیسر

- پروسیسرز

- مصنوعات

- پروڈکٹ مینجمنٹ

- پروفائل

- پروگرام

- مناسب

- مناسب طریقے سے

- خصوصیات

- ملکیت

- تحفظ

- فراہم

- فراہم کرنے

- عوامی

- معیار

- سوال

- اصلی

- احساس

- تسلیم شدہ

- باقاعدہ

- ضرورت

- باقی

- ظاہر

- رن

- چل رہا ہے

- منظر

- دوسری

- خفیہ

- سیکورٹی

- دیکھ کر

- سیمکولیٹر

- سینئر

- احساس

- علیحدہ

- سیریز

- siemens ڈاؤن لوڈ،

- سلیکن

- اسی طرح

- سائمن

- سمیلیٹر

- ساتھ ساتھ

- ایک

- چھ

- شبہ

- سست

- So

- سافٹ ویئر کی

- سولیرس

- ٹھوس

- حل

- حل

- کچھ

- کچھ

- کچھ بھی نہیں

- مخصوص

- ڈھیر لگانا

- معیار

- شروع کریں

- شروع

- شروع

- سترٹو

- ریاستی آرٹ

- قدم رکھنا

- محرک

- بند کرو

- حکمت عملی

- کامیاب

- اس طرح

- سپلائرز

- حمایت

- کے نظام

- لے لو

- بات

- بات کر

- اہداف

- ٹاسک

- تکنیک

- ٹیکنالوجی

- ٹیکنالوجی

- ٹیسٹ

- ٹیسٹنگ

- ٹیسٹ

- کہ

- ۔

- ان

- ان

- وہاں.

- یہ

- بات

- چیزیں

- تین

- کے ذریعے

- وقت

- کرنے کے لئے

- آج

- مل کر

- کے آلے

- اوزار

- علاج

- سچ

- سبق

- اقسام

- چھتری

- کے تحت

- سمجھ

- یونیکس

- us

- استعمال کی شرائط

- توثیق

- قیمت

- مختلف اقسام کے

- وینڈر

- دکانداروں

- توثیق

- تصدیق

- اس بات کی تصدیق

- تصدیق کرنا

- ورژن

- بنام

- قابل عمل

- نائب صدر

- لنک

- راستہ..

- طریقوں

- اچھا ہے

- کیا

- کیا ہے

- چاہے

- جس

- ڈبلیو

- گے

- ساتھ

- کے اندر

- بغیر

- کام

- مشقت

- کام کر

- دنیا

- گا

- لکھنا

- تحریری طور پر

- غلط

- سال

- اور

- زیفیرنیٹ