چپلیٹس نے ڈیزائن کے ایک شعبے کو آسان بنا دیا ہے لیکن دوسرے محاذ پر پنڈورا باکس کھول دیا ہے۔ ہر ایک کی نقلی پیچیدگی چپلیٹ کم ہے لیکن اب چپلیٹ سے چپلیٹ انٹرکنیکٹ پیچیدہ ہو گیا ہے۔ لوگ مختلف انٹرکنیکٹ پروٹوکولز، UCIe کی مختلف حالتوں، UCIe کی ترتیبات میں ترمیم، انٹرفیس کی رفتار، جسمانی تہوں کی تعداد اور اسی طرح ایک کے ساتھ تجربہ کر رہے ہیں۔ اب AXI جیسے میراثی معیارات، نئے پروٹوکول جیسے PICe6.0 اور کیش ہم آہنگی کو مکس میں شامل کریں۔

مجموعی طور پر، یہ تجربات کا ایک بالکل نیا مجموعہ تخلیق کرتا ہے۔ ایک جس کے لیے روایتی ایمولیشن اور RTL ماڈلنگ کام نہیں کرے گی۔ آپ کو سب سے پہلے فن تعمیر کی تجارت پر ایک کوشش خرچ کرنے کی ضرورت ہے، نہ کہ صرف اجزاء کے انتخاب میں۔ اس کا مطلب یہ ہوگا کہ آپ کو ٹریفک کا تجزیہ، ایپلیکیشن پارٹیشننگ، سسٹم کی سائزنگ اور مختلف قسم کی فزیکل پرت کے اثرات کو کرنا ہوگا۔ نیز، درخواست کے لحاظ سے بینچ مارک بہت مختلف ہوگا۔

UCIe تصریح نئی ہے اور کوئی واضح بینچ مارکس نہیں ہیں۔ نیز، UCIe تصریح صرف تاخیر اور طاقت پر رہنمائی فراہم کرتی ہے۔ دونوں سخت تقاضے ہیں۔ اس کا مطلب ہے کہ پاور پرفارمنس ایریا کا مطالعہ ناگزیر ہے۔ جیسا کہ آپ کے پاس پروٹوکول-پروٹوکول-پروٹوکول کی تبدیلی ہے جیسے PCIe 6.0 سے UCIe سے AXI، ماڈلنگ سیٹ اپ پیچیدہ ہے۔

ایک حل یہ ہے کہ سسٹم ماڈلنگ کا استعمال کرتے ہوئے دیکھیں بصری سم سے میرابلیس۔ ڈیزائن. انہوں نے حال ہی میں ایک UCIe سسٹم لیول کا آئی پی ماڈل لانچ کیا ہے اور وہ انٹرکنیکٹ کے استعمال کے متعدد کیسز کا مظاہرہ کریں گے۔ چپلیٹ سمٹ. ڈیزائنرز کی رہنمائی کے لیے، انہوں نے ایک گائیڈ شائع کیا ہے جس میں استعمال کے بہت سے معاملات، متوقع پاور پرفارمنس کے نتائج اور اصلاح کے اختیارات شامل ہیں۔ ان کے پاس سمٹ میں کاغذی پیشکش اور ایک بوتھ دونوں ہیں۔ میں آپ کو وہاں دیکھنے کی امید کرتا ہوں!

اس کے علاوہ، یہاں ایک کاغذ کا لنک ہے جو لوگ حاصل کرسکتے ہیں: UCIe انٹرکنیکٹ آرکیٹیکچر پر مبنی ایک متفاوت کمپیوٹنگ سسٹم کی پرفارمنس ماڈلنگ

خلاصہ:

لیڈنگ ایج نوڈس پر آج کے پیچیدہ چپ ڈیزائن عام طور پر متعدد ڈائز (یا چپلیٹ) پر مشتمل ہوتے ہیں۔ نقطہ نظر مختلف مینوفیکچررز یا عملوں کے ساتھ ساتھ دوبارہ قابل استعمال IP سے مرنے کی اجازت دیتا ہے۔ ڈیزائنرز کو ایسے پیچیدہ حالات کے مختلف نفاذ کا جائزہ لینے کے لیے سسٹم لیول ماڈل کی ضرورت ہوتی ہے۔

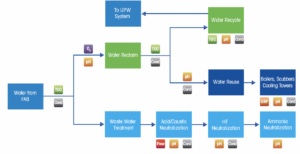

مثال کے نظام میں ایک I/O چپلیٹ، کم پاور کور چپلیٹ، ہائی پرفارمنس کور چپلیٹ، آڈیو-ویڈیو چپلیٹ، اور اینالاگ چپلیٹ، یونیورسل چپلیٹ انٹرکنیکٹ ایکسپریس (UCIe) معیار کا استعمال کرتے ہوئے آپس میں جڑے ہوئے ہیں۔

ہماری ٹیم نے کئی منظرناموں اور کنفیگریشنز پر غور کیا جس میں ایڈوانس اور معیاری پیکجز، مختلف ٹریفک پروفائلز اور وسائل، اور وقت ختم ہونے پر ایونٹس کی رسائی اور جائزہ لینے کے لیے ایک ریٹیمر شامل ہے۔ مشن ایپلی کیشنز کے لیے UCIe انٹر کنیکٹ کی طاقتوں اور کمزوریوں کی نشاندہی کرنے سے ہمیں کارکردگی، طاقت اور فعال ضروریات کو پورا کرنے کے لیے ہر سب سسٹم کے لیے بہترین ترتیب حاصل کرنے میں مدد ملی۔

Mirabilis Design Inc کے بارے میں

میرابیلیس ڈیزائن ایک سلیکون ویلی سافٹ ویئر کمپنی ہے، جو پروڈکٹ کی تفصیلات میں خطرے کی شناخت اور اسے ختم کرنے کے لیے سافٹ ویئر اور تربیتی حل فراہم کرتی ہے، پروڈکٹ کو تیار کرنے کے لیے درکار انسانی اور وقتی وسائل کی درست پیشین گوئی کرتی ہے، اور متنوع انجینئرنگ کے درمیان رابطے کو بہتر بناتی ہے۔

ٹیموں.

VisualSim آرکیٹیکٹ انٹلیکچوئل پراپرٹی، سسٹم لیول ماڈلنگ، سمولیشن، ماحولیات کا تجزیہ اور ایپلیکیشن ٹیمپلیٹس کو یکجا کرتا ہے تاکہ ماڈل کی تعمیر، تخروپن، تجزیہ اور RTL تصدیق کو نمایاں طور پر بہتر بنایا جا سکے۔ ماحول ڈیزائنرز کو اس قابل بناتا ہے کہ وہ تیزی سے ایک ایسے ڈیزائن میں تبدیل ہو جائیں جو ایک دوسرے پر منحصر وقت اور بجلی کی ضروریات کے متنوع سیٹ کو پورا کرتا ہے۔ یہ تحریری تصریح کے متوازی (اور اس کی مدد کے طور پر) اور پروڈکٹ کے نفاذ (مثال کے طور پر، RTL، سافٹ ویئر کوڈ، یا اسکیمیٹک) سے پہلے ڈیزائن کے عمل میں بہت جلد استعمال ہوتا ہے۔

بھی پڑھیں:

ویبنار: فن تعمیر کی تلاش کے دوران 95%+ درست طاقت کی پیمائش کیسے حاصل کی جائے

SysML کو ہارڈ ویئر آرکیٹیکچر سے میپ کرنا

طلباء کے لیے ماڈل پر مبنی ڈیزائن کورسز

اس پوسٹ کو بذریعہ شیئر کریں:

- SEO سے چلنے والا مواد اور PR کی تقسیم۔ آج ہی بڑھا دیں۔

- پلیٹو ڈیٹا ڈاٹ نیٹ ورک ورٹیکل جنریٹو اے آئی۔ اپنے آپ کو بااختیار بنائیں۔ یہاں تک رسائی حاصل کریں۔

- پلیٹوآئ اسٹریم۔ ویب 3 انٹیلی جنس۔ علم میں اضافہ۔ یہاں تک رسائی حاصل کریں۔

- پلیٹو ای ایس جی۔ کاربن، کلین ٹیک، توانائی ، ماحولیات، شمسی، ویسٹ مینجمنٹ یہاں تک رسائی حاصل کریں۔

- پلیٹو ہیلتھ۔ بائیوٹیک اینڈ کلینیکل ٹرائلز انٹیلی جنس۔ یہاں تک رسائی حاصل کریں۔

- ماخذ: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- : ہے

- : ہے

- : نہیں

- a

- درست

- درست طریقے سے

- حاصل

- شامل کریں

- اعلی درجے کی

- امداد

- کی اجازت دیتا ہے

- ساتھ

- بھی

- an

- تجزیہ

- اور

- ایک اور

- درخواست

- ایپلی کیشنز

- نقطہ نظر

- فن تعمیر

- کیا

- رقبہ

- AS

- At

- کی بنیاد پر

- BE

- بن

- اس سے پہلے

- معیار

- معیارات

- کے درمیان

- دونوں

- باکس

- لیکن

- کیشے

- کر سکتے ہیں

- حاصل کر سکتے ہیں

- مقدمات

- چپ

- واضح

- کوڈ

- یکجا

- مواصلات

- کمپنی کے

- مکمل طور پر

- پیچیدہ

- پیچیدگی

- اجزاء

- کمپیوٹنگ

- سلوک

- ترتیب

- سمجھا

- مشتمل

- تعمیر

- تقارب

- تبادلوں سے

- کور

- کورسز

- پیدا

- مظاہرین

- منحصر ہے

- ڈیزائن

- ڈیزائن کا عمل

- ڈیزائنرز

- ڈیزائن

- ترقی

- مختلف

- متنوع

- کے دوران

- ہر ایک

- ابتدائی

- کوشش

- کا خاتمہ

- جذباتی

- کے قابل بناتا ہے

- ماحولیات

- اندازہ

- واقعات

- مثال کے طور پر

- توقع

- استعمال

- تجربات

- ایکسپریس

- توسیع

- پہلا

- کے لئے

- سے

- سامنے

- فنکشنل

- عام طور پر

- حاصل

- گوگل

- رہنمائی

- رہنمائی

- ہارڈ ویئر

- ہے

- مدد

- یہاں

- اعلی کارکردگی

- امید ہے کہ

- کس طرح

- کیسے

- HTTPS

- انسانی

- i

- شناخت

- کی نشاندہی

- اثر

- نفاذ

- عمل درآمد

- کو بہتر بنانے کے

- in

- سمیت

- دانشورانہ

- املاک دانش

- باہم منسلک

- انٹرفیس

- IP

- IT

- فوٹو

- صرف

- تاخیر

- شروع

- پرت

- تہوں

- کی وراست

- سطح

- کی طرح

- LINK

- دیکھو

- لاٹوں

- لو

- کم

- مینوفیکچررز

- زیادہ سے زیادہ چوڑائی

- مطلب

- کا مطلب ہے کہ

- پیمائش

- سے ملو

- ملتا ہے

- مشن

- اختلاط

- ماڈل

- ماڈلنگ

- ماڈلنگ

- ایک سے زیادہ

- ضرورت ہے

- نئی

- نہیں

- نوڈس

- اب

- تعداد

- حاصل

- of

- on

- ایک

- صرف

- کھول

- کھول دیا

- زیادہ سے زیادہ

- اصلاح کے

- آپشنز کے بھی

- or

- پیکجوں کے

- کاغذ.

- متوازی

- کارکردگی

- جسمانی

- پلاٹا

- افلاطون ڈیٹا انٹیلی جنس

- پلیٹو ڈیٹا

- پوسٹ

- طاقت

- پیش گوئی

- پریزنٹیشن

- عمل

- عمل

- مصنوعات

- پروفائلز

- جائیداد

- پروٹوکول

- فراہم کرتا ہے

- فراہم کرنے

- شائع

- میں تیزی سے

- تک پہنچنے

- پڑھیں

- حال ہی میں

- ضرورت

- ضروریات

- وسائل

- نتائج کی نمائش

- قابل اعتماد

- رسک

- منظرنامے

- دیکھنا

- منتخب

- مقرر

- ترتیبات

- سیٹ اپ

- کئی

- نمایاں طور پر

- سلیکن

- سلیکن ویلی

- آسان

- تخروپن

- حالات

- So

- سافٹ ویئر کی

- حل

- حل

- تصریح

- رفتار

- خرچ

- معیار

- معیار

- طاقت

- سخت

- مطالعہ

- اس طرح

- سربراہی کانفرنس

- کے نظام

- ٹیم

- سانچے

- کہ

- ۔

- وہاں.

- وہ

- اس

- وقت

- کرنے کے لئے

- روایتی

- ٹریفک

- ٹریننگ

- اقسام

- یونیورسل

- us

- استعمال کی شرائط

- استعمال کیا جاتا ہے

- کا استعمال کرتے ہوئے

- وادی

- مختلف حالتوں

- توثیق

- بہت

- کی طرف سے

- کمزوریاں

- اچھا ہے

- جس

- گے

- ساتھ

- کام

- لکھا

- آپ

- زیفیرنیٹ