1980'lerde koaksiyel kablolar üzerinden 10 Mb/sn paylaşımlı LAN'larla piyasaya sürülmesinden bu yana Ethernet, tutarlı ilerlemeler kaydetti ve artık 1.6 Tb/sn'ye kadar hızları destekleme potansiyeline sahip. Bu ilerleme, Ethernet'in canlı yayın, Radyo Erişim Ağları ve endüstriyel kontrol gibi daha geniş bir uygulama yelpazesine hizmet etmesine olanak tanıdı ve güvenilir paket aktarımının ve hizmet kalitesinin önemini vurguladı. Mevcut İnternet bant genişliğinin ~500 Tbps seviyesinde olmasıyla birlikte, gelişmiş arka uç veri merkezi içi trafik yönetimine yönelik artan bir talep var. Her ne kadar bireysel sunucular henüz saniyede Terabit seviyelerinde çalışmıyor olsa da, genel veri merkezi trafiği bu ölçeğe yaklaşıyor, bu da IEEE'nin 802.3dj grubunu standardizasyon çabalarına girişmeye sevk ediyor ve genişleyen veri akışını yönetmek için sağlam Ethernet denetleyicilerine ve SerDe'lere ihtiyaç duyuyor. Artan taleplerin olduğu bu ortamda, işlemciler arası iletişim şimdiden bu hızlara ulaşıyor.

İşlemciler arası iletişim, minimum gecikmeyle 1.6T hızlarına olan ihtiyacın öncülüğünü yapıyor. Bireysel cihazlar kendi doğal işlem kapasiteleri ve çip boyutları nedeniyle kısıtlanırken, çiplerin birleştirilmesi bu kapasiteleri önemli ölçüde artırabilir. İlk nesil uygulamaların, yüksek performanslı işlemcilerin ve belleğin bir havuzda toplanmasına olanak tanıyan, bulut bilişimde ölçeklenebilirliği ve verimliliği artıran veri merkezi içi anahtardan anahtara bağlantıların takip etmesi bekleniyor.

IEEE'nin 802.3dj Girişimi: 1.6 Tbps birlikte çalışabilirlik için Ethernet standartlarının geliştirilmesi

Gelişen standardizasyon çabalarına uyum, kesintisiz ekosistem birlikte çalışabilirliği için çok önemlidir. IEEE'nin 802.3dj grubu, saniyede 200G'den 1.6 Terabit'e kadar hızlar için fiziksel katmanları ve yönetim parametrelerini kapsayan yeni Ethernet standardını formüle etme sürecindedir. Grubun hedefi, MAC katmanında 1.6-10'ü aşmayan maksimum bit hata oranını hedefleyen 13 Tbps Ethernet MAC veri hızıdır. Diğer olanaklar arasında, 16G ve 8G SerDes'ten yararlanan, farklı çip uygulamalarına uygun, isteğe bağlı 112 ve 224 şeritli Bağlantı Birimi Arayüzleri (AUI) yer alır. Fiziksel olarak, 1.6 Tbps spesifikasyonu, bir metreye kadar 8 çift bakır twinax kablo ve 8 metre ile 500 km arasındaki mesafeler için 2 çift fiber üzerinden iletim yapılmasını gerektirir. Standardın tamamen onaylanmasının 2026 baharında gerçekleşmesi beklense de, temel özelliklerin 2024 yılında tamamlanması öngörülüyor.

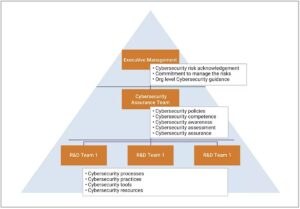

1.6T Ethernet alt sistemlerinde bant genişliği yükü ve hata düzeltme

Şekil 1: 1.6T Ethernet Alt Sisteminin bileşenlerini gösteren diyagram.

Daha önceki Ethernet yinelemelerinde PCS, öncelikle güvenilir paket tespiti için veri kodlamaya odaklandı. Ancak 1.6T Ethernet hızlarına yükselişle birlikte, özellikle kısa bağlantılarda bile sinyal bozulmasını önlemek için İleri Hata Düzeltme (FEC) ihtiyacı belirgin hale geliyor. Bu amaçla 1.6T Ethernet, Reed-Solomon FEC'i kullanmaya devam ediyor. Bu yaklaşım, 514 sembol bloğuna kodlanmış 10 adet 544 bitlik sembolden oluşan bir kod sözcüğü oluşturur ve bu da %6 bant genişliği ek yüküyle sonuçlanır. Bu FEC kod sözcükleri AUI fiziksel bağlantılarına dağıtılır, böylece her bir fiziksel bağlantı (8T Ethernet için 1.6) bir kod sözcüğünün tamamını taşımaz. Bu yöntem yalnızca hata patlamalarına karşı ek koruma sağlamakla kalmaz, aynı zamanda uzak uç kod çözücüde paralelleştirmeyi mümkün kılarak gecikmeyi azaltır.

Bir dişli kutusu ve SerDes içeren Fiziksel Ortam Eklentisi (PMA), Ethernet sinyalini iletilen kanallara getirir. 1.6T Ethernet için bu, her biri 8 Gbps hızında çalışan 212 kanalı içerir ve %6 FEC ek yüküne karşılık gelir. Kullanılan modülasyon tekniği, her iletim sembolü için iki veri bitini kodlayan ve böylece geleneksel Geri Dönüşsüz Sıfır (NRZ) yaklaşımıyla birleştirildiğinde bant genişliğini etkili bir şekilde iki katına çıkaran 4 Seviyeli Darbe Genlik Modülasyonudur (PAM-4). İletim mekanizması dijitalden analoğa dönüşüme dayanırken, alıcı tarafta DSP'lerle birleştirilmiş analogdan dijitale dönüşüm, doğru sinyal çıkarılmasını sağlar.

Ayrıca, Ethernet PCS'nin bir Ethernet bağlantısı üzerinde uçtan uca yayılan bir "dış FEC" sunduğuna dikkat etmek önemlidir. Daha uzun erişim kanallarını desteklemek için, tek tek fiziksel hatlar için ek bir hata düzeltme katmanı planlanıyor ve muhtemelen bir hamming kodu FEC benimseniyor. Bu düzeltmenin, birincil uygulamasını bu düzeltmenin zorunlu olduğu optik alıcı-verici modüllerinde bulması bekleniyor.

Şekil 2: Genişletilmiş erişim için birleştirilmiş FEC kullanıldığında eklenen ek yükü gösteren diyagram.

Şekil 2'de gösterilen örnek sistemde MAC ve PCS, bir optik modül ve bir fiber uzatma yoluyla bağlanmıştır. PCS'nin bit hata oranı 10'dur-5 optik modül bağlantısında artı optik bağlantının kendisinden kaynaklanan hatalar. Tek bir RS-FEC uçtan uca kullanmak, 10'a ulaşmak için yeterli olmaz-13 Bağlantıyı güvenilmez hale getiren Ethernet standardı. Bir seçenek, her atlamada ayrı RS FEC'nin üçlü uygulanması olabilir; bu da maliyetleri ve gecikmeyi önemli ölçüde artırır. Daha etkili bir çözüm, optik bağlantıların tipik rastgele hatalarını karşılayan, özellikle optik bağlantı için birleştirilmiş bir Hamming Kodu FEC'nin entegrasyonudur. Bu iç FEC katmanı, hat hızının 212 Gbps'den 226 Gbps'ye ek bir genişlemesini sağlar, dolayısıyla SerDes'in bu hat hızını destekleyebilmesi önemlidir.

1.6T Ethernet sistemlerinde gecikme sorunları

Şekil 3: 1.6T Ethernet Alt Sistemi için gecikme yolu.

Ethernet gecikmesine çeşitli bileşenler katkıda bulunur: iletim kuyruğu, iletim süresi, orta geçiş süresi ve çeşitli işlem ve alım süreleri. Bunu görselleştirmek için kapsamlı bir 3T Ethernet alt sistemini gösteren şekil 1.6'ü inceleyin. Gecikme uzak uç uygulamanın tepki süresinden etkilenebilirken, bu faktör Ethernet'in dışındadır ve bu nedenle gecikme analizi sırasında sıklıkla hariç tutulur. Ethernet arayüzündeki gecikmeyi en aza indirmek, belirli koşulların anlaşılmasını gerektirir. Örneğin, daha yavaş istemci bağlantılarındaki doğal gecikmeler nedeniyle, anahtarlar arasındaki ana hat bağlantıları için gecikme birincil bir sorun olmayabilir. Mesafe de bir rol oynar; daha büyük uzunluklar daha fazla gecikmeye neden olur. Elbette bu, diğer senaryolarda gecikmeyi göz ardı etmemiz gerektiği anlamına gelmiyor; gecikmeyi azaltmak her zaman bir hedeftir.

İletim gecikmesi doğası gereği Ethernet hızına ve çerçeve boyutuna bağlıdır. Spesifik olarak, 1.6T Ethernet sistemi için minimum boyutlu bir paketin iletilmesi 0.4ns gerektirir; bu, esas olarak 2.5 GHz saatin tıklaması başına bir Ethernet çerçevesi anlamına gelir. Öte yandan, standart maksimum boyutlu bir çerçevenin iletilmesi 8ns sürer; Jumbo Çerçeveler için bu süre 48ns'ye kadar çıkar. Seçilen ortam ayrıca gecikmeyi de belirler. Örneğin, optik fiber tipik olarak metre başına 5 ns'lik bir gecikmeye neden olurken, bakır kablolar metre başına 4 ns ile marjinal olarak daha hızlıdır.

Genel gecikmenin önemli bir bölümü alıcı denetleyicisinden kaynaklanmaktadır. RS FEC kod çözücü, doğası gereği gecikmeye neden olur. Hata düzeltmeyi başlatmak için sistemin 4 Tbps'de 1.6 ns'ye karşılık gelen 12.8 kod sözcüğü alması gerekir. Hata düzeltme ve ara belleğe alma dahil sonraki etkinlikler bu gecikmeyi artırır. FEC kod sözcüğü depolama süresi tutarlı kalsa da, mesaj alımı sırasındaki gecikme, spesifik uygulamaya bağlıdır. Bununla birlikte gecikme, titiz dijital tasarım stratejileri kullanılarak optimize edilebilir.

Temelde, FEC mekanizması ve fiziksel mesafe veya kablo uzunluğu nedeniyle doğal, kaçınılmaz bir gecikme vardır. Bu faktörlerin ötesinde tasarım uzmanlığı, Ethernet denetleyici gecikmesini en aza indirmede çok önemli bir rol oynar. MAC, PCS ve PHY'yi entegre eden ve optimize eden eksiksiz bir çözümden yararlanmak, en verimli, düşük gecikmeli uygulamaya giden yolu açar.

Özet

Şekil 4: Synopsys 224G Ethernet PHY IP için son derece doğrusal PAM-3 gözlerini sergileyen 4nm sürecindeki ilk geçiş silikon başarısı.

1.6 Tbps Ethernet, en fazla bant genişliği gerektiren ve gecikmeye duyarlı uygulamalar için özel olarak tasarlanmıştır. 224G SerDes teknolojisinin ortaya çıkışı ve MAC ve PCS IP'deki gelişmelerle birlikte, gelişen 1.6T Ethernet standartlarına sürekli uyum sağlayan kapsamlı çözümlere artık erişilebiliyor. Ek olarak, protokole özgü gecikme ve hata düzeltme yöntemleri nedeniyle, IP dijital ve analog tasarımının, veri yolunda gereksiz gecikmeye neden olmasını önlemek için uzman tasarımcılar tarafından özenle hazırlanması gerekir.

1.6T SoC tasarımlarında en üst performanslara ulaşmak, verimli bir şekilde optimize edilmiş bir mimariyi ve her çip bileşeni için titiz tasarım uygulamalarını gerektirir. Bu, güç tasarrufunu vurgular ve silikon ayak izini en aza indirerek 1.6T veri hızlarını gerçeğe dönüştürür. Silikonla kanıtlanmış Synopsys 224G Ethernet PHY IP 1.6T MAC ve PCS Kontrol Cihazı için zemini hazırladı. Son teknoloji tasarım, analiz, simülasyon ve ölçüm tekniklerini kullanan Synopsys, olağanüstü sinyal bütünlüğü ve titreşim performansı sunmaya devam ediyor. MAC+PCS+PHY dahil eksiksiz Ethernet çözümü.

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :vardır

- :dır-dir

- :olumsuzluk

- :Neresi

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- erişim

- ulaşılabilir

- muhasebe

- doğru

- Başarmak

- karşısında

- faaliyetler

- katma

- Ek

- Ayrıca

- Benimsemek

- gelişmeler

- ilerleyen

- karşı

- hedefleyen

- izin

- zaten

- Ayrıca

- Rağmen

- her zaman

- ortasında

- tutarları

- yükseltmek

- an

- analiz

- ve

- beklenen

- Uygulama

- uygulamaları

- yaklaşım

- mimari

- ARE

- AS

- At

- önlemek

- Arka uç

- zemin

- Bant genişliği

- BE

- olur

- arasında

- Ötesinde

- Bit

- Engellemek

- desteklemek

- artırılması

- Getiriyor

- inşa

- fakat

- by

- kablo

- kablolar

- CAN

- kapasiteleri

- taşımak

- zorluklar

- kanallar

- yonga

- cips

- seçilmiş

- koşullar

- müşteri

- saat

- bulut

- cloud computing

- kod

- kombine

- birleştirme

- Yakın İletişim

- tamamlamak

- tamamlama

- bileşen

- bileşenler

- kapsamlı

- içeren

- bilgisayar

- İlgilendirmek

- birlikte

- bağlı

- Bağlantılar

- KORUMA

- Düşünmek

- hususlar

- tutarlı

- devam ediyor

- devamlı olarak

- katkıda bulunmak

- kontrol

- kontrolör

- Dönüştürme

- Bakır

- çekirdek

- maliyetler

- karşı koymak

- kurs

- hazırlanmış

- oluşturur

- akım

- veri

- Datacenter

- ilk

- gecikmeleri

- teslim etmek

- Talep

- talep

- talepleri

- resmeden

- Dizayn

- tasarımcıları

- tasarımlar

- Bulma

- Cihaz

- emirlerini

- farklı

- dijital

- özenle

- görüntüler

- mesafe

- dağıtıldı

- Değil

- iki katına

- gereken

- süre

- sırasında

- her

- Daha erken

- ekosistem

- Etkili

- etkili bir şekilde

- verim

- verimli

- verimli biçimde

- çabaları

- çıkma

- vurgulamaktadır

- vurgulayan

- istihdam

- kullanılarak

- sağlar

- etkinleştirme

- kapsar

- son

- son uca

- olmasını sağlar

- Tüm

- hata

- Hatalar

- kızışma

- öz

- gerekli

- esasen

- Eter (ETH)

- Hatta

- Her

- belirgin

- gelişen

- örnek

- olağanüstü

- hariç

- genişleyen

- genişleme

- beklenen

- uzman

- Uzmanlık

- uzatmak

- uzatma

- dış

- çıkarma

- Gözler

- faktör

- faktörler

- uzak

- Daha hızlı

- Özellikler

- Featuring

- şekil

- bulmak

- Ad

- Birinci nesil

- akış

- odaklanmış

- takip

- ayak izi

- İçin

- formüle etmek

- ileri

- ÇERÇEVE

- itibaren

- daha fazla

- nesil

- verir

- büyük

- grup

- Grubun

- Büyüyen

- el

- kullanma

- Yüksek

- yüksek performans

- büyük ölçüde

- Ancak

- HTML

- HTTPS

- zorunlu

- uygulama

- önem

- önemli

- gelişmiş

- in

- Diğer

- dahil

- Dahil olmak üzere

- artan

- bireysel

- Sanayi

- etkilenmiş

- doğal

- doğal olarak

- başlatmak

- Girişim

- örnek

- Entegre

- bütünleşme

- bütünlük

- arayüzey

- arayüzler

- Internet

- Birlikte çalışabilirlik

- içine

- gerçek

- tanıtmak

- Tanıtımlar

- tanıtım

- içerir

- IP

- IT

- yineleme

- ONUN

- kendisi

- jpg

- şerit

- Gecikme

- tabaka

- katmanları

- uzunluk

- seviyeleri

- kaldıraç

- Muhtemelen

- çizgi

- hatları

- LINK

- bağlantılar

- yaşamak

- uzun

- Düşük

- mac

- Yapımı

- yönetmek

- yönetim

- maksimum genişlik

- maksimum

- Mayıs..

- ortalama

- ölçüm

- mekanizma

- orta

- Bellek

- mesaj

- yöntem

- yöntemleri

- titiz

- en az

- azaltmak

- en aza indirir

- minimize

- modül

- Modüller

- Daha

- çoğu

- şart

- yaklaşan

- gerek

- ağlar

- yine de

- yok hayır

- notlar

- şimdi

- nesnel

- of

- sık sık

- on

- ONE

- bir tek

- işletme

- optimize

- optimize

- seçenek

- or

- Diğer

- tekrar

- tüm

- çiftleri

- parametreler

- özellikle

- yol

- PC'ler

- başına

- performans

- performansları

- fiziksel

- fiziksel olarak

- boru hattı

- asıl

- Platon

- Plato Veri Zekası

- PlatoVeri

- çalış

- artı

- potansiyel

- güç kelimesini seçerim

- uygulamalar

- öncelikle

- birincil

- süreç

- işleme

- işlemciler

- ilerleme

- tahmin

- koruma

- protokol

- nabız

- amaç

- itme

- kalite

- radyo

- rasgele

- menzil

- oran

- oranlar

- ulaşmak

- uzanarak almak

- tepki

- Gerçeklik

- teslim almak

- alma

- resepsiyon

- azaltarak

- güvenilir

- kalıntılar

- render

- gerektirir

- kısıtlı

- Ortaya çıkan

- gürbüz

- Rol

- köklü

- koşu

- ölçeklenebilirlik

- ölçek

- senaryolar

- sorunsuz

- İkinci

- görüldü

- bölüm

- hassas

- ayrı

- hizmet vermek

- hizmet

- set

- birkaç

- Paylaşılan

- kısa

- meli

- vitrine

- işaret

- önemli ölçüde

- Silikon

- simülasyon

- beden

- So

- çözüm

- Çözümler

- açıklıklı

- öncülük

- özel

- özellikle

- şartname

- hızları

- bahar

- Aşama

- standart

- standardizasyon

- standartlar

- hafızası

- stratejileri

- akış

- sonraki

- önemli

- başarı

- böyle

- uygun

- destek

- sembol

- sistem

- ısmarlama

- alır

- teknik

- teknikleri

- Teknoloji

- göre

- o

- The

- ve bazı Asya

- Orada.

- böylece

- bu nedenle

- Bunlar

- Re-Tweet

- İçinden

- Böylece

- kene

- bağlı

- zaman

- zamanlar

- için

- üst

- geleneksel

- trafik

- transfer

- iletmek

- Üçlü

- iki

- tipik

- tipik

- kaçınılmaz

- anlayış

- üstlenmek

- birim

- yaklaşan

- üzerine

- kullanma

- kullanmak

- üzerinden

- görselleştirmek

- Yol..

- we

- ne zaman

- hangi

- süre

- Daha geniş

- ile

- içinde

- olur

- henüz

- zefirnet

- sıfır