Çoklu kalıp sistemleri, komple sistemi oluşturmak için aynı pakette bir araya getirilen çeşitli özel fonksiyonel kalıplardan (veya yongalardan) oluşur. Çoklu kalıp sistemleri yakın zamanda, paketlenmiş çipteki işlevselliği iyi bir verimle üretilebilecek şekilde ölçeklendirmeye yönelik bir yol sağlayarak Moore yasasının yavaşlamasının üstesinden gelmek için bir çözüm olarak ortaya çıktı.

Ek olarak, çoklu kalıp sistemleri, farklı pazar segmentlerinin ihtiyaçlarını karşılayacak performans ölçeklendirmesi, aynı üründe çeşitli süreç düğümlerini karıştırıp eşleştirerek işlev başına süreç düğümünün optimizasyonu, pazara sunma süresinin daha hızlı olması ve riskin azaltılması açısından ürün SKU'su esnekliği sağlar.

Kalıptan kalıba daha yüksek yönlendirme yoğunluğu sağlamak ve kalıplar arasında daha yüksek bant genişliği trafiğini desteklemek için paket teknolojisi, silikon aracılara (TSV'lerle) veya silikon köprülere ve daha yakın zamanda yeniden dağıtım katmanlarına (RDL) dayalı yeni, gelişmiş paketler oluşturmak üzere gelişti. , yayılımlar ve HD alt tabakalar.

Çoklu kalıp sistemlerinin başarısının önemli bir yönü, sistemin farklı üretim ve montaj aşamalarında test edilebilirliğini sağlamanın yanı sıra sahada güvenilir operasyonun sağlanmasıdır. Ekstra montaj adımları ve daha karmaşık çarpma ve paketleme teknolojileri kullanan çoklu kalıp sistemleri, monolitik tasarımlar için en son teknolojinin ötesine geçen test ve güvenilirlik prosedürleri gerektirir.

Çıplak kalıplar ve paketin kendisi, tüm kusurlu kalıpların veya paketlerin bir pakete monte edilmeden önce tespit edilmesini sağlamak için önceden test edilmelidir. Arızalı bir kalıp ancak montajdan sonra tespit edilirse, çoklu kalıp sisteminin tamamının hurdaya çıkarılması gerekir; bu da maliyet üzerinde ciddi bir etki yaratır. Çıplak kalıpları test etme sürecine Bilinen İyi Kalıp (KGD) testi denir.

Montaj sürecinin kendisi seçilen paketleme teknolojisine göre değişir. Örneğin, kalıpların ilk önce yerleştirildiği ve ara bağlantının bunların üzerine kurulduğu çip öncelikli teknolojiler, "iyi olduğu bilinen paket" testine izin vermez ve ara bağlantı arızalıysa potansiyel olarak iyi kalıpların hurdaya çıkarılmasıyla sonuçlanır. Öte yandan, ara bağlantının ayrı olarak inşa edildiği ve kalıpların bunun üzerine monte edildiği çip son teknolojilerinde, montajdan önce paketin ön testine olanak sağlanarak iyi kalıpların hurdaya çıkma olasılığı azaltılır.

Çoklu kalıp sistemi test edilebilirlik çözümü çeşitli yönlere ayrılabilir:

- Kalıp içindeki bireysel blokların kapsamını test edin

- Bireysel kalıpların test kapsamı (çıplak kalıplar)

- Birleştirilmiş sistemin testi (kalıptan kalıba kapsamlı)

- Çıplak kalıplarda test kumaşına erişim

- Montajdan sonra test kumaşına hiyerarşik erişim

Bu makale, çok kalıplı sistem güvenilirliğini sağlamak için UCIe IP'den yararlanan kapsamlı bir test edilebilirlik çözümünün faydalarını açıklamaktadır.

UCIe arayüzü için DFT

UCIe arayüzü için yüksek test kapsamı çözümü, çıplak kalıp testi aşamasında kusurlu kalıpları yönlendirmek için UCIe IP'deki kapsamlı test edilebilirlik özelliklerinin uygulanmasıyla elde edilir. Özelliklerden bazıları şunlardır:

- Sentezlenen tüm dijital devreleri kapsayan tarama zincirleri

- Özel bloğa özel BIST işlevselliği

- IO pinine kadar tüm sinyal zincirini kapsayan geri döngü yerleşik kendi kendine test (BIST) işlevi

- Programlanabilir sözde rastgele ikili dizi (PRBS) ve kullanıcı tanımlı test desenleri oluşturucuları ve denetleyicileri

- Yanlış geçişleri ortadan kaldırmak için hata ekleme

Ek olarak, paket montajından sonra kapsamı kalıptan kalıba bağlantıya kadar genişletme işlevi, aşağıdakiler de dahil olmak üzere yüksek düzeyde test kapsamı elde edilmesine yardımcı olabilir:

- Uzak taraf (ölmeden ölmeye) BIST geri döngü işlevi

- Ölümden ölmeye bağlantı BIST

- Marjinallikleri analiz etmek için 2 boyutlu göz marjı oluşturma

- Şerit başına test ve onarım işlevselliği

UCIe testi ve onarımı

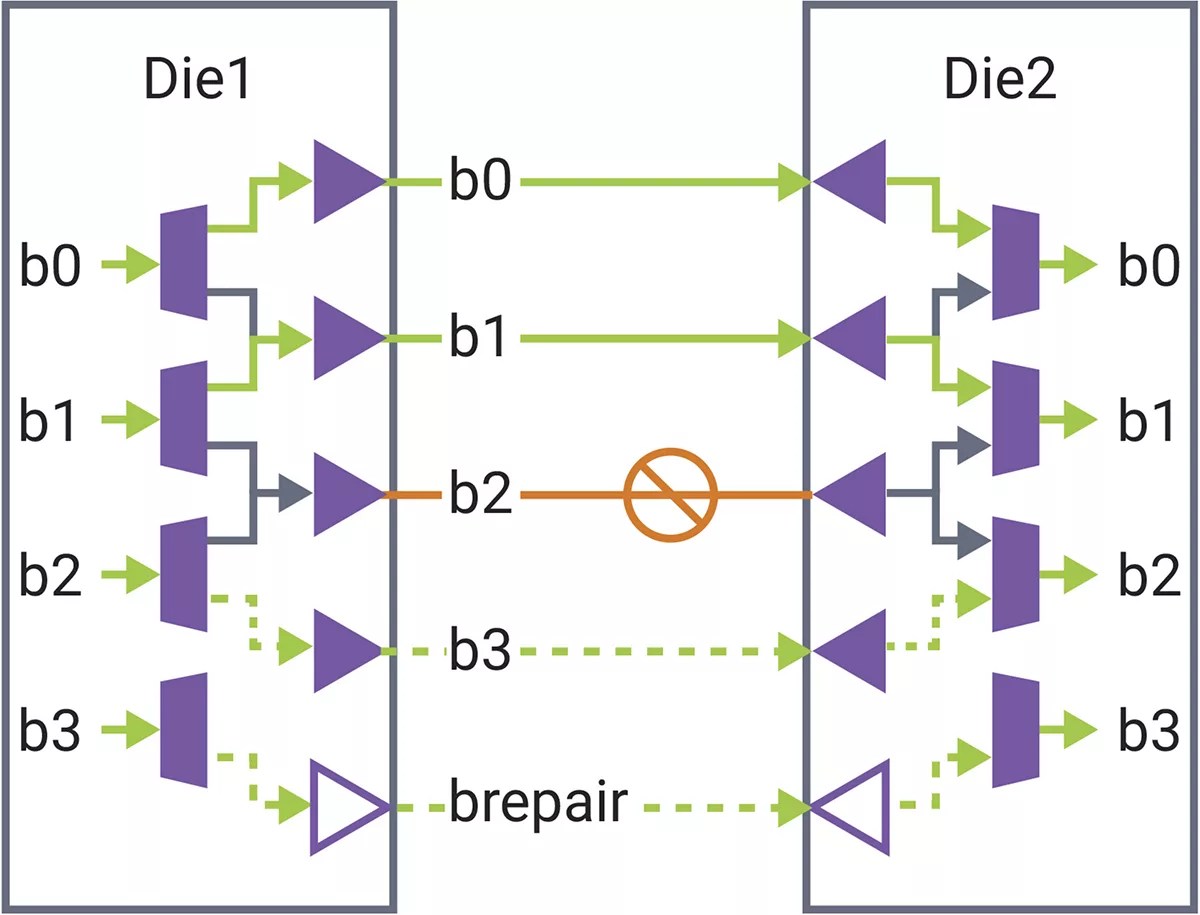

Gelişmiş paketler, ince aralıklı mikro darbeleme ve silikon veya RDL aracıları üzerinde yönlendirme ile yüksek yoğunluklu yönlendirmeye olanak tanır. Montaj işlemi sırasında bazı mikro tümsek bağlantıları iyi oluşmayabilir ve bozulabilir. UCIe, montaj sonrasında bu bağlantıları potansiyel verim kaybını telafi edecek şekilde test etme ve onarma olanağı sunar.

UCIe testi ve onarımı, üretim testi sırasında ve bağlantı başlatılırken gerçekleştirilir. Test aşamasında her bir bağlantı yavaş hızda kusurlara karşı kontrol edilir. Arızalı bağlantılar, verilerin UCIe standardı tarafından önceden tanımlanmış yedek bağlantılara yeniden yönlendirilmesiyle onarılır.

Gelişmiş paketleri hedefleyen UCIe yapılandırmaları, tüm işlevsel bağlantıların onarılmasını sağlamak için yön başına 8 adede kadar yedek pin (TX ve RX) içerir:

- Veri pini onarımı için dört yedek pin, her 2 veri pini grubu için 32 pin

- Saat ve saatler ile palet pimi onarımı için bir yedek pim

- Her biri geçerli pin, yan bant veri pini ve saat veri pini onarımı için üç yedek pin

Test ve onarım yürütmesi, ölmeden ölmeye bağlantısında geçerli bir trafik olmadığında gerçekleşir. Onarım tamamlandıktan ve bağlantı başlatıldıktan sonra iyi olduğu ve trafiğin sorunsuz geçilebileceği varsayılır. Sonuçta ortaya çıkan PHY onarım imzası adı verilen PHY konfigürasyonu, bağlantının her iki ucundaki dahili kayıtlarda saklanır.

Çalışma sırasında eskime veya diğer mikro darbe özellikleri nedeniyle bozulma, bağlantı performansını etkileyebilir. Bu, protokol düzeyinde bit hata oranındaki (BER) artışla veya en kötüsü veri kaybıyla tespit edilecektir. Bu durumda bağlantının kesilmesi ve yeni bir test ve onarım adımının gerçekleştirilmesi beklenir.

Bununla birlikte, bazı uygulamaların ölümden ölüme bağlantıdaki trafiğin sürekliliği açısından sıkı gereksinimleri vardır; bunlar, çalışma sırasında trafiğin kesintiye uğramasını tolere edemezler. Bu durumlarda, bir test edilebilirlik çözümü her UCIe alıcı pinine Sinyal Bütünlüğü Monitörleri (SIM) ekler.

Şekil 1: Yerleşik yedek bağlantılar kullanılarak bağlantı onarımı.

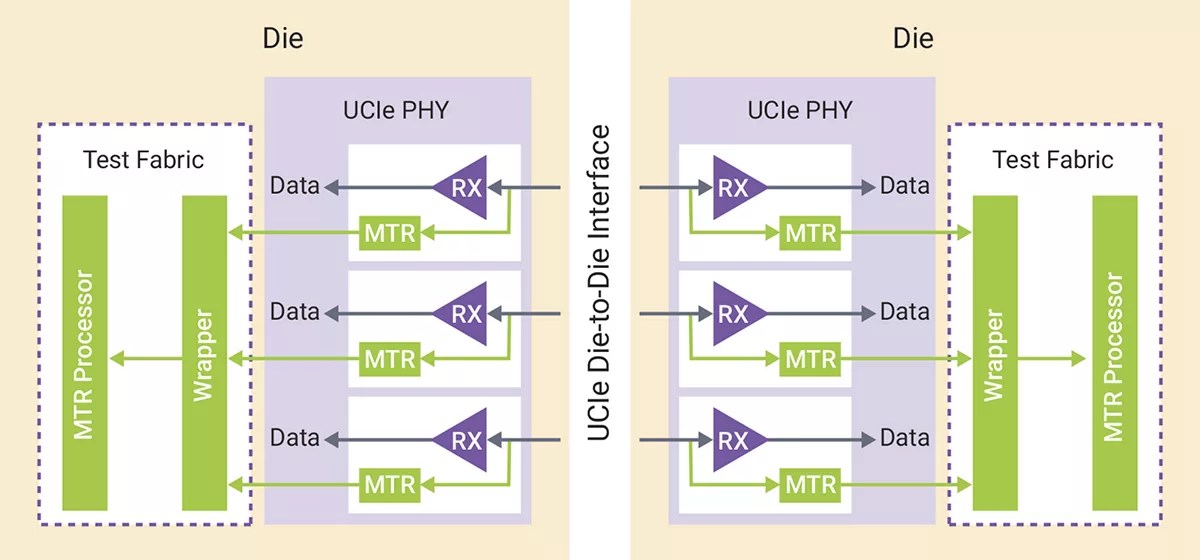

Sinyal bütünlüğü monitörleri

SIM monitörleri alıcıya gömülü küçük bloklardır. Bağlantı performansını etkileyebilecek veya bağlantının artık sağlıklı olmadığını ve yakın gelecekte kopabileceğini gösteren sinyal özelliklerindeki değişiklikleri tanımlamak için normal çalışma sırasında alıcı pinindeki sinyali sürekli olarak algılarlar.

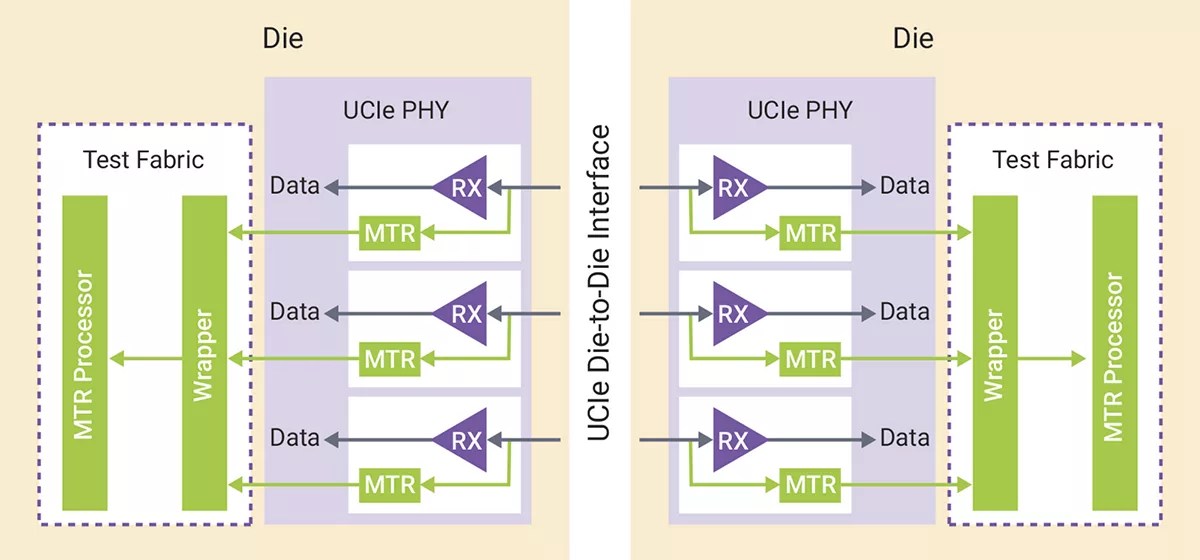

Bireysel sensörler tarafından toplanan veriler, daha ileri işlemler için arayüzün dışındaki bir İzleme, Test ve Onarım (MTR) kontrol cihazında toplanır. Verilerin birden çok UCIe bağlantısından toplanması, çoklu kalıp sisteminin sağlığına ilişkin anında bilgi sağlayabilir ve bağlantıların tahmine dayalı bakımını mümkün kılabilir.

Bu prosedür yoluyla belirli bir bağlantının arızalanma riskiyle karşı karşıya olduğu tahmin edilirse, trafik kesintisi olmadan bile devre dışı bırakılabilir ve veriler, UCIe PHY onarım mekanizmasından yararlanılarak yedek bağlantılardan birine yeniden yönlendirilebilir.

Şekil 2: UCIe bağlantıları için sağlık izleme çözümü.

Uyanma süresinin hızlandırılması

Ölmeden ölmeye arayüz kullanım durumlarının çoğu için (örneğin, sunucu bölme veya ölçeklendirmede) trafik modelinin çalışma sırasında kararlı olduğu varsayılırken, bazı kullanım durumlarında trafik bir patlama davranışı sergileyebilir. Bu gibi durumlarda trafik yokken güç tasarrufu sağlamak için arayüzün düşük güç moduna getirilmesi tercih edilir. Bağlantının yeniden başlatılması, test ve onarım sürecinden kaçınılarak ve önceki PHY başlatma sırasında oluşturulan UCIe PHY onarım imzasına güvenilerek hızlandırılabilir.

Bu konsept, kalıbın tamamen kapatıldığı durumlara da genişletilebilir. Bu durumlarda, PHY onarım imzası PHY'den alınır ve kalıp üzerinde kalıcı bir bellekte (eFuse veya flash) saklanır. Bellek muhtemelen farklı kullanım durumlarını veya koşullarını kapsayan birden fazla imzayı saklayarak ek kullanıcı esnekliği sağlayabilir.

UCIe ile kalıp testlerini hızlandırma

Test süresi pahalı bir üründür. Farklı kalıpların testlerini paralel olarak yürütmek için test stratejisini hiyerarşik olarak bölümlendirerek test süresini hızlandırmak mümkündür. İki kalıbın test altyapısının hiyerarşik olarak bağlanmasıyla hiyerarşi, çoklu kalıp sistemindeki birden fazla kalıp boyunca genişletilebilir. Böyle bir yaklaşım, ana kalıptaki tek bir JTAG (veya benzeri) test arayüzünden çoklu kalıp sistemindeki tüm kalıplara erişime olanak tanır.

Çoğu zaman test süresinin sınırlaması, test vektörlerinin kalıplara yüklenmesi veya okunması zamanıdır. JTAG arayüzleri hız darboğazı haline gelebilir. Bu sınırlamanın üstesinden gelmek için tasarımcılar, test ekipmanına arayüz olarak PCI Express (PCIe) veya USB vb. gibi mevcut yüksek hızlı arayüzleri kullanabilirler. Test vektörleri ve komutları bu arayüz için paketlenir ve üretim testi aşamasında kalıpta paketinden çıkarılır.

Çoğu kalıbın yüksek hızlı bir arayüzü yoktur, ancak UCIe kalıptan kalıba arayüzü test sırasında kalıplar arasında büyük test vektörlerini ve komutları yüksek hızda taşımak için kullanılabilir. UCI kalıptan kalıba arayüzü, pin sayısını artırmadan tüm çoklu kalıp sistemi boyunca yüksek hızlı DFT erişimini genişletir; bu, özellikle IO ve alanı sınırlı kalıplar için önemlidir.

Özet

UCIe kalıptan kalıba arayüzünün yanı sıra, tüm bu test ve güvenilirlik geliştirme özelliklerini mümkün kılan ortak payda, tüm dahili blokları bağlayabilen bir test, onarım ve izleme yapısıdır. Test, onarım ve izleme yapısı, çoklu kalıp sistemindeki çeşitli kalıpları kapsayarak aşağıdaki önemli işlevleri yerine getiren yapılandırılmış bir hiyerarşik altyapı sağlar:

- Çoklu kalıp sisteminde bireysel kalıpların testini yönetir

- Test süresini azaltmak için test planlamasını optimize eder

- UCIe arayüzü aracılığıyla kalıplar arasında yüksek hızlı test erişimini destekler

- UCIe arayüzüne gömülü sağlık izleme arayüzlerinden bilgi toplar ve sistem düzeyinde daha fazla işleme olanak sağlar

- PHY onarım imzasının kalıcı bir bellekte depolanmasını yönetir

- Ve dahası

Synopsys, hızlı heterojen entegrasyon için EDA ve IP dahil olmak üzere kapsamlı ve ölçeklenebilir çok kalıplı bir sistem çözümü sağlar. Güvenli ve güvenilir bir ölümden ölüme bağlantı için Synopsys, eksiksiz bir UCIe Denetleyici, PHY ve Doğrulama IP çözümü sunar. Synopsys SLM ve Test Ailesinin bir parçası olarak, STAR Hiyerarşik Sistem (SHS) çözümünün yanı sıra eksiksiz bir UCIe İzleme, Test ve Onarım (MTR) çözümü de mevcuttur. MTR çözümü, UCIe hatlarındaki sinyal kalitesini ölçmek için sinyal bütünlüğü monitörünü, kendi kendine test için BIST'i ve yedek şerit tahsisi için onarım mantığını içerir; SHS çözümü ise IEEE 1687, IEEE 1149.1 ve IEEE 1838 endüstri standartlarını destekleyen bağlantı yapısı olarak hizmet eder. arayüzler. Bu eksiksiz çözüm, çok kalıplı sistemlerin güvenilir çalışması için kritik önem taşıyan silikon yaşam döngüsünün tüm aşamalarında UCIe'nin durumunun verimli ve uygun maliyetli bir şekilde izlenmesini sağlar.

Kaynaklar:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoAiStream. Web3 Veri Zekası. Bilgi Genişletildi. Buradan Erişin.

- Adryenn Ashley ile Geleceği Basmak. Buradan Erişin.

- PREIPO® ile PRE-IPO Şirketlerinde Hisse Al ve Sat. Buradan Erişin.

- Kaynak: https://semiengineering.com/from-known-good-die-to-known-good-system-with-ucie-ip/

- :vardır

- :dır-dir

- :olumsuzluk

- :Neresi

- $UP

- 1

- 8

- a

- kabiliyet

- hızlandırmak

- hızlandırılmış

- erişim

- Başarmak

- elde

- Elde Ediyor

- karşısında

- ilave

- Ek

- Ekler

- ileri

- Sonra

- Yaşlanma

- Türkiye

- tahsis

- izin vermek

- veriyor

- boyunca

- an

- çözümlemek

- ve

- uygulamaları

- yaklaşım

- ARE

- göre

- AS

- boy

- yönleri

- monte

- Montaj

- varsayılır

- At

- mevcut

- kaçınma

- Bant genişliği

- merkezli

- BE

- müşterimiz

- önce

- olmak

- faydaları

- arasında

- Ötesinde

- Engellemek

- Blokları

- her ikisi de

- mola

- köprüler

- getirmek

- yapılı

- yerleşik

- by

- denilen

- CAN

- yapamam

- dava

- durumlarda

- zincir

- zincirler

- özellikleri

- kontrol

- yonga

- saat

- Saatler

- emtia

- ortak

- tamamlamak

- tamamen

- karmaşık

- kapsamlı

- kavram

- koşullar

- yapılandırma

- Sosyal medya

- bağlantı

- Bağlantılar

- Bağlantı

- sürekli

- kontrolör

- Ücret

- uygun maliyetli

- olabilir

- kapsama

- kaplama

- yaratmak

- çevrimiçi kurslar düzenliyorlar.

- kritik

- veri

- tanımlı

- yoğunluk

- tasarımcıları

- tasarımlar

- algılandı

- Ölmek

- farklı

- dijital

- yön

- özürlü

- bölünmüş

- do

- aşağı

- gereken

- sırasında

- her

- verimli

- gidermek

- gömülü

- ortaya

- etkinleştirmek

- sağlar

- etkinleştirme

- uçları

- artış

- sağlamak

- sağlanması

- ekipman

- vb

- Eter (ETH)

- Hatta

- gelişti

- örnek

- infaz

- sergi

- mevcut

- beklenen

- pahalı

- ekspres

- uzatmak

- kapsamlı, geniş

- ekstra

- göz

- kumaş

- yanlış

- aile

- HIZLI

- Daha hızlı

- hatalı

- Özellikler

- alan

- ince

- Ad

- flaş

- Esneklik

- takip etme

- İçin

- oluşturulan

- itibaren

- işlev

- fonksiyonel

- işlevsellik

- fonksiyonlar

- daha fazla

- gelecek

- toplanmış

- jeneratörler

- Go

- Tercih Etmenizin

- grup

- el

- Var

- Sağlık

- sağlıklı

- yardım et

- hiyerarşi

- Yüksek

- daha yüksek

- Ancak

- HTTPS

- belirlemek

- IEEE

- if

- darbe

- uygulanması

- önemli

- in

- dahil

- içerir

- Dahil olmak üzere

- Artırmak

- artan

- belirtmek

- bireysel

- sanayi

- bilgi

- Altyapı

- anlayışlar

- anlık

- bütünleşme

- bütünlük

- arayüzey

- arayüzler

- iç

- kesilmiş

- içine

- IP

- IT

- kendisi

- anahtar

- bilinen

- şerit

- büyük

- Kanun

- katmanları

- seviye

- leverages

- kaldıraç

- yaşam döngüsü

- sınırlama

- LINK

- bağlantılar

- yük

- mantık

- uzun

- kayıp

- kayıp

- Düşük

- yapılmış

- Ana

- bakım

- pazar

- Maç

- uygun

- maksimum genişlik

- Mayıs..

- ölçme

- mekanizma

- Bellek

- Moda

- izlemek

- izleme

- monitörler

- yekpare

- Daha

- çoğu

- MTR

- çoklu

- şart

- yakın

- ihtiyaçlar

- yeni

- yok hayır

- düğüm

- düğümler

- normal

- numara

- of

- Teklifler

- on

- ONE

- bir tek

- operasyon

- optimizasyon

- or

- Diğer

- dışarı

- dışında

- Üstesinden gelmek

- paket

- paketlenmiş

- paketler

- ambalaj

- Paralel

- Bölüm

- özellikle

- geçti

- yol

- model

- desen

- performans

- kalıcı

- faz

- pimleri

- Zift

- Platon

- Plato Veri Zekası

- PlatoVeri

- mümkün

- belki

- potansiyel

- potansiyel

- güç kelimesini seçerim

- powered

- tahmin

- önceki

- Önceki

- olasılık

- sorunlar

- prosedürler

- süreç

- işleme

- PLATFORM

- üretim

- protokol

- sağlamak

- sağlar

- sağlama

- kalite

- oran

- Okumak

- geçenlerde

- kurtarır

- azaltmak

- azaltarak

- kayıtlar

- güvenilirlik

- güvenilir

- onarım

- gerektirir

- Yer Alan Kurallar

- Ortaya çıkan

- Risk

- yönlendirme

- koşmak

- RX

- aynı

- İndirim

- ölçeklenebilir

- ölçekleme

- çizelgeleme

- güvenli

- segmentler

- seçilmiş

- sensörler

- Dizi

- ciddi

- vermektedir

- birkaç

- meli

- yan

- işaret

- İmzalar

- Silikon

- SIM

- benzer

- tek

- durumlar

- yavaş

- Yavaşlama

- küçük

- çözüm

- biraz

- açıklıklı

- özel

- özel

- hız

- kararlı

- standart

- Star

- state-of-the-art

- adım

- Basamaklar

- hafızası

- mağaza

- saklı

- Stratejileri

- yapılandırılmış

- başarı

- böyle

- destek

- Destek

- sistem

- Sistemler

- hedefleme

- Teknolojileri

- Teknoloji

- şartlar

- test

- Test yapmak

- testleri

- o

- The

- Onları

- sonra

- Orada.

- Bunlar

- onlar

- Re-Tweet

- İçinden

- zaman

- için

- üst

- iz

- trafik

- nakletme

- iki

- TX

- usb

- kullanım

- Kullanılmış

- kullanıcı

- kullanma

- çeşitli

- Doğrulama

- üzerinden

- oldu

- Yol..

- webp

- İYİ

- Ne

- ne zaman

- hangi

- süre

- irade

- ile

- içinde

- olmadan

- En kötü

- Yol ver

- zefirnet