S2C เป็นผู้นำระดับโลกในด้านการสร้างต้นแบบ FPGA มาเกือบสองทศวรรษแล้ว และแพลตฟอร์มการสร้างต้นแบบ FPGA ได้ติดตามความพร้อมใช้งานของ FPGA ล่าสุดอย่างใกล้ชิด รวมถึง FPGA ล่าสุดจากทั้ง Xilinx และ Intel และพวกเขากำลังส่งมอบตามคำมั่นสัญญาที่จะพัฒนาโซลูชันการสร้างต้นแบบสำหรับการสร้างต้นแบบการออกแบบที่มีระดับไฮเปอร์สเกล – ปรับขนาดขึ้น ความจุของแพลตฟอร์มต้นแบบและความสามารถในการรองรับการออกแบบเกตหลายพันล้านชิ้น

เมื่อมองย้อนกลับไปในช่วงต้นไตรมาสที่ 4 ปี 2020 S2C ได้ประกาศสนับสนุน Xilinx VU19P UltraScale+ FPGA รุ่นใหม่ โดยนำเสนอแพลตฟอร์มต้นแบบ FPGA แบบเดี่ยว แบบคู่ และแบบสี่ส่วน จากนั้นในเดือนธันวาคมปี 2020 S2C ได้ติดตามด้วยการประกาศของตระกูล Prodigy Logic Matrix ที่มีความหนาแน่นสูงของแพลตฟอร์มการสร้างต้นแบบที่มี 8 FPGA ต่อ Logic Matrix, 8 Logic Matrix ต่อแร็คเซิร์ฟเวอร์เดี่ยว (64 FPGA) และการเชื่อมต่อหลายชุด ชั้นวางเซิร์ฟเวอร์เข้าด้วยกัน การทำซ้ำครั้งแรกของ Logic Matrix ถูกส่งด้วย Xilinx VU440 FPGA (ขนานนามว่า LX1) ให้กับลูกค้ารุ่นแรกที่ไม่สามารถรอรุ่น VU19P ได้ (ขนานนามว่า LX2).

ตอนนี้ S2C กำลังก้าวขึ้นสู่เกม Logic Matrix ด้วย LX2ซึ่งเพิ่มความสามารถในการสร้างต้นแบบของเกตที่ใช้งานได้ถึง 60% เมื่อเทียบกับรุ่น VU440! ประตูที่ใช้งานได้มากขึ้นต่อ FPGA หมายถึง FPGA ที่น้อยลง การเชื่อมต่อระหว่าง FPGA ที่น้อยลง และประสิทธิภาพที่สูงขึ้นสำหรับการออกแบบต้นแบบเดียวกัน ด้วยความจุประตูประมาณ 392 ล้านประตูต่อ LX2, แร็คเซิร์ฟเวอร์มาตรฐานที่บรรจุเต็มพร้อม 8 LX2's เปิดใช้งานความสามารถในการสร้างต้นแบบโดยประมาณมากกว่า 3 พันล้านเกต ASIC!

รูปที่ 1: Prodigy Logic Matrix LX2

| ตระกูลเมทริกซ์ลอจิกอัจฉริยะ | ||

| LX1 | LX2 | |

| FPGA | เอ็กซ์ซีวียู440 | เอ็กซ์ซีวียู19พี |

| ประตู ASIC โดยประมาณ (M) | 240 | 392 |

| จำนวน FPGAs | 8 | 8 |

| เซลล์ลอจิกระบบ (K) | 44,328 | 71,504 |

| หน่วยความจำ FPGA (Mb) | 709 | 1,327.2 |

| สไลซ์ DSP | 23,040 | 30,720 |

| ผู้ใช้ภายนอก I/Os | 9,216 | 10,368 |

| เครื่องรับส่งสัญญาณ SerDes | 384 จีทีเอช | 640 จีทีวาย |

| ตัวเชื่อมต่ออัจฉริยะ | 64 | 72 |

| ตัวเชื่อมต่อ PGT | 8 | 0 |

| ตัวเชื่อมต่อเครื่องรับส่งสัญญาณ | 80 MSAS แต่ละรายการพร้อม 4 GTH + 8 IO | 160 MCIO แต่ละรายการพร้อม 4 GTY + 8 IO |

| ประสิทธิภาพ SerDes | 16 Gbps | 28 Gbps |

รูป 2: ครอบครัวลอจิกเมทริกซ์

การเชื่อมต่อถึงกันด้วยความเร็วสูงที่ยืดหยุ่นเป็นกุญแจสำคัญในการสร้างต้นแบบ FPGA ที่มีความหนาแน่นสูงและ Logic Matrix รองรับกลยุทธ์การเชื่อมต่อถึงกัน 3 ระดับตามลำดับชั้น: ชอร์ตบริดจ์ สำหรับการเชื่อมต่อระหว่าง FPGAs ที่อยู่ใกล้เคียง ซิสลิงค์ สำหรับการเชื่อมต่อสายเคเบิล FPGA แบนด์วิดธ์สูงและ ทรานส์ลิงค์ สำหรับการเชื่อมต่อระหว่าง FPGA SerDes ทางไกลผ่านสาย MCIO เพื่อลดความซับซ้อนของการเชื่อมต่อระหว่าง FPGA และเพิ่มมูลค่าของ ทรานส์ลิงค์โฟลว์การแบ่งพาร์ติชันของ S2C รองรับการส่งสัญญาณมัลติเพล็กซ์พินความเร็วสูงที่เพิ่งเปิดตัวของ Xilinx (HSTPM) ทำให้การถ่ายโอนสัญญาณที่แม่นยำตามรอบง่ายขึ้น การเชื่อมต่อแบบหลายจุดของพิน และการเชื่อมต่อ SerDes FPGA ที่มีความหน่วงต่ำ

เพื่อลดเวลาในการสร้างต้นแบบและเพิ่มผลผลิตในการสร้างต้นแบบ เครื่องมือเพิ่มประสิทธิภาพการสร้างต้นแบบอื่นๆ ของ S2C ได้รับการออกแบบโดยคำนึงถึง Logic Matrix ซึ่งรวมถึง ผู้เล่น Pro Runtime ซอฟต์แวร์ – และเครื่องมือสร้างต้นแบบ S2C เสริม รวมถึง โปรโตบริดจ์, เอ็มดีเอ็ม โปร, และ S2C's ต้นแบบพร้อม IP.

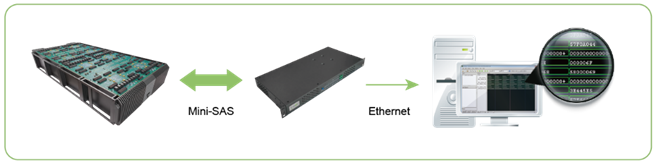

ผู้เล่น Pro Runtime ซอฟต์แวร์รวมอยู่ใน LX2โดยมีคุณสมบัติที่สะดวกสบาย เช่น การจัดการนาฬิกาขั้นสูง การทดสอบตัวเองในตัว การตรวจจับบอร์ดอัตโนมัติ การตั้งโปรแกรมแรงดันไฟฟ้า I/O การดาวน์โหลด FPGA หลายรายการ และการตรวจสอบและการจัดการระบบระยะไกล รวมถึง AXEVision ซึ่งเป็นเครื่องมือดีบัก AXI-over-Ethernet ในตัวเพื่อลดความซับซ้อนของการดีบักระยะไกลของการออกแบบที่เกี่ยวข้องกับ AXI

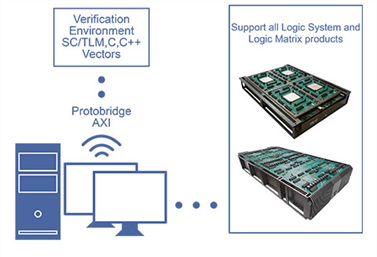

โปรโตบริดจ์ รองรับการถ่ายโอนข้อมูลความเร็วสูง (สูงสุด 1GB/s) ระหว่างโฮสต์พีซีและ LX2 – ช่วยให้ถ่ายโอนธุรกรรมที่เป็นแบบจำลองซอฟต์แวร์ สตรีมวิดีโอ หรือสิ่งกระตุ้นการทดสอบอื่นๆ สำหรับการตรวจสอบระบบจำนวนมาก

รูปที่ 3: ProtoBridge

เอ็มดีเอ็ม โปร มีการดีบักการติดตามเชิงลึกด้วยทริกเกอร์ข้ามสำหรับ FPGA สูงสุดแปด FPGA การดูการติดตามสัญญาณแบบหลาย FPGA จากหน้าต่างการดูเดียว พื้นที่จัดเก็บรูปคลื่นการติดตามภายนอก 64GB อัตราการสุ่มตัวอย่างร่องรอยสูงถึง 125MHz และรองรับภาษาเครื่องของสถานะทริกเกอร์สำหรับการจับการติดตามที่ซับซ้อน ความต้องการ.

รูปที่ 4: MDM Pro

S2C ยังมีห้องสมุดมากมายของ ต้นแบบพร้อม IP สำหรับ LX2 - การ์ดลูกสาวแบบปลั๊กแอนด์เพลย์ - ที่เร่งการสร้างสภาพแวดล้อมการสร้างต้นแบบรอบต้นแบบ FPGA

รูปที่ 5: Prototype Ready IP Daughter Cards

เมทริกซ์ลอจิกอัจฉริยะ LX2 สามารถใช้ได้ในขณะนี้ สำหรับข้อมูลเพิ่มเติม โปรดติดต่อตัวแทนขาย S2C ในพื้นที่ของคุณ หรือเยี่ยมชม www.s2ceda.com.

แชร์โพสต์นี้ผ่าน: ที่มา: https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/- 2020

- Add-on

- ประกาศ

- การประกาศ

- รอบ

- ASIC

- ความพร้อมใช้งาน

- พันล้าน

- คณะกรรมการ

- สายเคเบิ้ล

- ความจุ

- การเชื่อมต่อ

- การเชื่อมต่อ

- ลูกค้า

- ข้อมูล

- การส่งมอบ

- ออกแบบ

- การตรวจพบ

- ระยะทาง

- ก่อน

- สิ่งแวดล้อม

- ครอบครัว

- คุณสมบัติ

- มะเดื่อ

- ชื่อจริง

- ไหล

- FPGA

- เกม

- เกตส์

- เหตุการณ์ที่

- HTTPS

- รวมทั้ง

- ข้อมูล

- อินเทล

- IP

- คีย์

- ภาษา

- ใหญ่

- ล่าสุด

- ห้องสมุด

- ในประเทศ

- การจัดการ

- มดลูก

- ล้าน

- การตรวจสอบ

- การเสนอ

- เสนอ

- อื่นๆ

- PC

- การปฏิบัติ

- เวที

- แพลตฟอร์ม

- มือโปร

- ผลผลิต

- ผลผลิต

- การเขียนโปรแกรม

- การสร้างต้นแบบ

- ราคา

- ความต้องการ

- ขาย

- ไต่ขึ้น

- ซอฟต์แวร์

- โซลูชัน

- สถานะ

- แรงบันดาลใจ

- การเก็บรักษา

- กลยุทธ์

- ลำธาร

- สนับสนุน

- รองรับ

- ระบบ

- ทดสอบ

- การทำธุรกรรม

- ความคุ้มค่า

- วีดีโอ

- รอ

- WHO