ในการประชุมสุดยอด RISC-V เมื่อเร็ว ๆ นี้ เซสชั่นสุดท้ายคือการอภิปรายเกี่ยวกับชิปเล็ตที่เรียกว่า Chiplets ในระบบนิเวศ RISC-V. ดำเนินรายการโดย Calista Redmond ซีอีโอของ RISC-V International ผู้ร่วมอภิปรายได้แก่:

- โลรองต์ มอลล์ ซีโอโอของ Arteris

- อนิเกต์ สหะ รองประธานฝ่ายบริหารผลิตภัณฑ์ของ Tenstorrent

- Dale Greenley รองประธานฝ่ายวิศวกรรมของ Ventana Microsystems

- Rob Aitken สถาปนิกผู้มีชื่อเสียงของ Synopsys

นี่เป็นการผสมผสานหัวข้อที่แปลกเล็กน้อยสำหรับฉัน แน่นอนว่าคุณสามารถใส่โปรเซสเซอร์ RISC-V ลงบนชิปเล็ตได้ แต่ความท้าทายไม่ได้แตกต่างจากโปรเซสเซอร์อื่นๆ มากนัก แต่ RISC-V นั้นร้อนแรงและชิปเล็ตก็เช่นกัน และบริษัทอย่าง Ventana ก็รวมเข้าด้วยกัน

ฉันขอเล่าความเป็นมาเล็กน้อยเกี่ยวกับบริษัทต่างๆ เพื่อนำไปใช้ในบริบท:

- ดังที่คุณคงทราบแล้วว่า Arteris สร้างเครือข่ายบนชิป (NoC) เป็นบริษัทที่เป็นกลางในหมู่ผู้จำหน่ายชิปเล็ต (และผู้จำหน่าย IP)

- Tenstorrent กำลังออกแบบกลุ่มผลิตภัณฑ์ชิป RISC-V แบบมัลติคอร์ประสิทธิภาพสูงมาก

- Ventana มี RISC-V IP แต่ยังส่งเป็นชิปเล็ตด้วย

- เห็นได้ชัดว่า Synopsys เป็นบริษัท EDA แต่พวกเขาได้ประกาศแกน RISC-V ก่อนหน้านี้ในการประชุมสุดยอด

]

การสนทนาที่เกิดขึ้นจริง

คำถามแรกจากคาลิสต้าคือซอฟต์บอลถามว่าชิปเล็ตมีมูลค่าเท่าใด

Dale กล่าวว่าไม่มีอะไรเฉพาะเจาะจงเกี่ยวกับ RISC-V สำหรับชิปเล็ต แต่ตลาดจะเป็นผู้ตัดสินใจว่าเมื่อคุณทำสิ่งเสาหินขนาดใหญ่หรือชิปเล็ต ขึ้นอยู่กับว่าลูกค้าจะจ่ายเงินให้คุณทำอะไร “เราให้บริการทั้ง IP และ Chiplets ซึ่งมีพื้นที่สำหรับทั้งสองอย่าง”

Aniket กล่าวว่า “การทำชิปเล็ตนั้นไม่ถูก แต่การทำชิปเล็ตและ RISC-V นั้นมีความยืดหยุ่น และคุณสามารถสร้างผลิตภัณฑ์แบบสกัดได้อย่างรวดเร็ว”

Laurent ไปหาต้นทุนการผลิต NRE เป็นสิ่งสำคัญมากที่จะต้องอยู่ภายใต้การควบคุม เนื่องจากมีเพียงไม่กี่คนที่สร้างชิ้นส่วน 100 ล้านชิ้น จึงมีผู้ขายเข้ามาเกี่ยวข้องมากขึ้นและห่วงโซ่อุปทานที่ซับซ้อน SoC นั้นซับซ้อน แต่ชิปเล็ตนั้นแย่กว่า

Rob ชี้ให้เห็นความแตกต่าง เช่น การเพิ่มชิปเล็ตสำหรับ RF และแอนะล็อก การมีตัวเร่งความเร็วเสริม และอื่นๆ นี่อาจเป็นการเปิดตลาดใหม่

คาลิสต้าถามต่อว่าเราอยู่ตรงไหนในวงการยานยนต์

Aniket ชี้ให้เห็นว่ายานยนต์เป็นสิ่งที่อนุรักษ์นิยมมาก และตอนนี้พวกเขาก็มีความก้าวร้าวเกี่ยวกับแพลตฟอร์มที่สามารถปรับขนาดได้ตั้งแต่รถยนต์ระดับล่างไปจนถึงรถยนต์ระดับไฮเอนด์ ด้วยชิปเล็ต ไม่มีใครคำนึงถึงความปลอดภัยในการใช้งานจริงๆ

Rob ไปที่การบินและอวกาศ (ไม่ใช่ยานยนต์) และพูดคุยถึงวิธีที่โดยปกติแล้วปริมาตรทางกายภาพคงที่ซึ่งกำหนดไว้เมื่อหลายสิบปีก่อน มันยากที่จะจัดสิ่งของให้เข้าที่

Laurent: บริษัทยานยนต์คือนักช้อปในแคตตาล็อกขั้นสูงสุดและชิปเล็ตที่ช่วยให้พวกเขาใช้ประโยชน์จาก AI เรดาร์ ระบบสาระบันเทิง และอื่นๆ ได้อย่างเต็มที่

คุณจะทำให้ซอฟต์แวร์ทำงานได้อย่างไร?

Rob: ถ้าคุณทำให้ระบบมีขนาดเล็กก็ไม่เป็นไร แต่การซื้อแคตตาล็อกยานยนต์ทำให้ยากขึ้น

Aniket: เกี่ยวข้องกับข้อความ “ถ้าคุณเพิ่มเราจะไม่ใช้” กลุ่มซอฟต์แวร์ยานยนต์จะรองรับ RISC-V ในอีก 5 ปี ซึ่งถือว่าเร็วมาก อาร์มใช้เวลา 15 ปีจึงจะไปถึงที่นั่น

ถาม: เราต้องการอะไรในการเชื่อมต่อ?

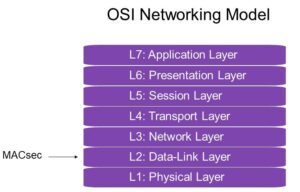

Laurent: มันซับซ้อนมากโดยเฉพาะกับผู้คนที่ไปจับจ่ายซื้อมันฝรั่งทอด PHY จากผู้ขายหลายรายอาจใช้งานร่วมกันได้ ทุกคนต่างสนใจ UCIe ผู้คนต้องการมาตรฐานที่ทำให้ชิปเล็ตเข้ากันได้ดีขึ้น

Aniket บ่นว่าไม่มีกระแสการออกแบบมาตรฐานสำหรับชิปเล็ต ขาดมาตรฐานอย่างมาก

Rob คิดว่าเราสามารถสร้างโฟลว์มาตรฐานได้ แต่ด้วยชิปเล็ตที่แตกต่างกัน เราไม่ต้องการโฟลว์การออกแบบที่แตกต่างกัน N N

ถาม: คุณมองเห็นอะไรใน 3-5 ปีข้างหน้าบ้าง?

Rob: เราจะก้าวไปอีกขั้นด้วยความแตกต่าง

“การซื้อแคตตาล็อกอาจขึ้นอยู่กับผู้ผลิตรถยนต์ OEM จะต้องอาศัยความพยายามอย่างมากในอุตสาหกรรม สิ่งที่แตกต่างกันจะใช้เวลานานกว่า

Aniket กล่าวว่าชิปเล็ตจะอยู่ในศูนย์ข้อมูลก่อนแล้วจึงยานยนต์ แต่คลื่นลูกแรกจะเป็นผู้ขายรายเดียว

สรุป

นี่เป็นการผสมผสานระหว่างสิ่งที่ผู้เข้าร่วมพูดและความคิดเห็นของฉันเอง

ฉันคิดว่าในขณะนี้ การออกแบบ RISC-V ที่ใช้ชิปเล็ตจะเป็นความพยายามของบริษัทเดียว (ยกเว้น บางที สำหรับหน่วยความจำแบนด์วิธสูง (HBM) มันซับซ้อนเกินไปที่จะสร้างการออกแบบที่มีชิปเล็ตหลายตัวจากบริษัทที่แตกต่างกัน ผู้แทรกแซง และเครือข่ายสำหรับเชื่อมต่อทั้งหมด โดยทั่วไปเรียกว่า RDL

การออกแบบจะเป็น 2.5D ไม่ใช่ 3D จริง (โดยที่แม่พิมพ์ซ้อนกันและสื่อสารกับผ่านซิลิคอน-เวียหรือ TSV) ในอนาคตอันใกล้

ยานยนต์มีความท้าทายในตัวเอง โดยเฉพาะอย่างยิ่งการทำให้การออกแบบที่ใช้ชิปเล็ตเชื่อถือได้ในสภาพแวดล้อมที่มีการสั่นสะเทือนมาก สิ่งนี้จะต้องมีการทดสอบอย่างละเอียด อีกประเด็นหนึ่งคือการรับรองความปลอดภัยในการทำงานในสภาพแวดล้อมแบบหลายแม่พิมพ์

UCIe มีแนวโน้มดีและค่อนข้างมีพื้นฐานมาจาก PCIe บริษัท PCIe รับประกันความน่าเชื่อถือผ่านปลั๊กอิน ฉันไม่เห็นว่าคุณจะสามารถรับประกันการทำงานร่วมกันของ UCIe ในชิปเล็ตในเชิงเศรษฐกิจได้อย่างไรผ่านกลไกที่คล้ายกัน

ท้ายที่สุด นอกเหนือจากความท้าทายทางเทคนิคแล้ว ยังมีความท้าทายทางการค้าหากเราต้องการไปสู่นิพพานของความสามารถในการซื้อชิปเล็ตที่มีจำหน่ายทั่วไปและประกอบเข้ากับระบบด้วยต้นทุนที่สมเหตุสมผล ความท้าทายที่ใหญ่ที่สุดคือใครจะเป็นผู้จ่ายเงินและถือครองสินค้าคงคลังของชิปเล็ต หากชิปเล็ตทั้งหมดต้องผลิตตามความต้องการ ข้อดีหลายประการของรอบเวลาที่รวดเร็วก็จะสูญเสียไป

แต่ชิปเล็ต RISC-V กำลังมาอย่างรวดเร็วอย่างแน่นอนในรูปแบบของการออกแบบหลายแม่พิมพ์บนอินเตอร์โพเซอร์ 2.5D ที่สร้างโดยบริษัทเดียว

ยังอ่าน:

NoC ช่วยให้สถาปนิกมีความยืดหยุ่นในการออกแบบระบบ RISC-V

การจับคู่คอร์ RISC-V กับ NoC จะเชื่อมโยงโปรโตคอล SoC เข้าด้วยกัน

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- PlatoData.Network Vertical Generative Ai เพิ่มพลังให้กับตัวเอง เข้าถึงได้ที่นี่.

- เพลโตไอสตรีม. Web3 อัจฉริยะ ขยายความรู้ เข้าถึงได้ที่นี่.

- เพลโตESG. คาร์บอน, คลีนเทค, พลังงาน, สิ่งแวดล้อม แสงอาทิตย์, การจัดการของเสีย. เข้าถึงได้ที่นี่.

- เพลโตสุขภาพ เทคโนโลยีชีวภาพและข่าวกรองการทดลองทางคลินิก เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/ip/arteris/338888-risc-v-and-chiplets-a-panel-discussion/

- :มี

- :เป็น

- :ไม่

- :ที่ไหน

- $ ขึ้น

- 100M

- 15%

- 167

- 200

- 300

- 3d

- a

- สามารถ

- เกี่ยวกับเรา

- คันเร่ง

- ที่เกิดขึ้นจริง

- เพิ่ม

- เพิ่ม

- นอกจากนี้

- ข้อได้เปรียบ

- การบินและอวกาศ

- ก้าวร้าว

- มาแล้ว

- AI

- ทั้งหมด

- ตาม

- ด้วย

- ในหมู่

- an

- และ

- ประกาศ

- อื่น

- ใด

- สถาปนิก

- เป็น

- ARM

- รอบ

- AS

- ถาม

- ขอให้

- At

- ยานยนต์

- พื้นหลัง

- ตาม

- BE

- กำลัง

- ที่ดีที่สุด

- ดีกว่า

- ใหญ่

- ที่ใหญ่ที่สุด

- บิต

- ทั้งสอง

- สร้าง

- การก่อสร้าง

- สร้าง

- แต่

- by

- ที่เรียกว่า

- CAN

- รถยนต์

- แค็ตตาล็อก

- ผู้บริหารสูงสุด

- อย่างแน่นอน

- โซ่

- ท้าทาย

- ความท้าทาย

- ถูก

- สี

- การผสมผสาน

- การรวมกัน

- อย่างไร

- มา

- เชิงพาณิชย์

- สื่อสาร

- บริษัท

- บริษัท

- ซับซ้อน

- ซับซ้อน

- เชื่อมต่อ

- การเชื่อมต่อ

- อนุรักษ์นิยม

- ถือว่า

- สิ่งแวดล้อม

- ควบคุม

- ขัน

- ราคา

- ค่าใช้จ่าย

- ลูกค้า

- วงจร

- ศูนย์ข้อมูล

- ทศวรรษที่ผ่านมา

- กำหนด

- มอบ

- ทั้งนี้ขึ้นอยู่กับ

- ขึ้นอยู่กับ

- ออกแบบ

- การออกแบบ

- การออกแบบ

- ตาย

- ต่าง

- กล่าวถึง

- การสนทนา

- โดดเด่น

- do

- การทำ

- Dont

- แต่ละ

- ก่อน

- ความพยายาม

- ปลาย

- ชั้นเยี่ยม

- ทำให้มั่นใจ

- มั่นใจ

- การสร้างความมั่นใจ

- สิ่งแวดล้อม

- โดยเฉพาะอย่างยิ่ง

- ทุกคน

- ยกเว้น

- กว้างขวาง

- FAST

- ปลาย

- ชื่อจริง

- พอดี

- การแก้ไข

- ความยืดหยุ่น

- มีความยืดหยุ่น

- ไหล

- กระแส

- สำหรับ

- มองไกลได้

- ฟอร์ม

- ราคาเริ่มต้นที่

- การทำงาน

- ต่อไป

- อนาคต

- ได้รับ

- ให้

- ยาก

- ยาก

- มี

- มี

- จุดสูง

- ประสิทธิภาพสูง

- ถือ

- ร้อน

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- HTTPS

- i

- if

- สำคัญ

- in

- อุตสาหกรรม

- International

- การทำงานร่วมกัน

- การทำงานร่วมกัน

- เข้าไป

- สินค้าคงคลัง

- ร่วมมือ

- IP

- ปัญหา

- IT

- ITS

- jpg

- กระตือรือร้น

- เก็บ

- ทราบ

- ที่รู้จักกัน

- ไม่มี

- ชื่อสกุล

- ให้

- กดไลก์

- อีกต่อไป

- สูญหาย

- Lot

- ต่ำ

- ทำ

- ทำให้

- การจัดการ

- ผลิต

- หลาย

- หลายคน

- ตลาด

- ตลาด

- ความกว้างสูงสุด

- อาจ..

- อาจจะ

- me

- กลไก

- เป็นเสาหิน

- ข้อมูลเพิ่มเติม

- หลาย

- my

- จำเป็นต้อง

- เครือข่าย

- เป็นกลาง

- ใหม่

- ไม่

- ไม่มีอะไร

- ตอนนี้

- of

- on

- ตามความต้องการ

- ONE

- เปิด

- ความคิดเห็น

- or

- อื่นๆ

- ออก

- ของตนเอง

- แผง

- อภิปราย

- ผู้เข้าร่วม

- ในสิ่งที่สนใจ

- ส่วน

- ชำระ

- คน

- บางที

- กายภาพ

- แพลตฟอร์ม

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- ผลงาน

- โพสต์

- ที่อาจเกิดขึ้น

- อาจ

- หน่วยประมวลผล

- ผลิตภัณฑ์

- การจัดการผลิตภัณฑ์

- การผลิต

- ผลิตภัณฑ์

- แวว

- โปรโตคอล

- ให้

- ซื้อ

- ใส่

- คำถาม

- ทีเดียว

- เรดาร์

- อ่าน

- จริงๆ

- เหมาะสม

- เมื่อเร็ว ๆ นี้

- ที่เกี่ยวข้อง

- ความเชื่อถือได้

- น่าเชื่อถือ

- ต้องการ

- ห้อง

- วิ่ง

- ความปลอดภัย

- กล่าวว่า

- ขนาด

- เห็น

- เซสชั่น

- ชุด

- ผู้ซื้อ

- ช้อปปิ้ง

- คล้ายคลึงกัน

- ตั้งแต่

- เดียว

- เล็ก

- So

- ซอฟต์แวร์

- ค่อนข้าง

- โดยเฉพาะ

- ซ้อนกัน

- สแต็ค

- มาตรฐาน

- มาตรฐาน

- คำแถลง

- ประชุมสุดยอด

- จัดหาอุปกรณ์

- ห่วงโซ่อุปทาน

- สนับสนุน

- ระบบ

- ระบบ

- เอา

- การพูดคุย

- วิชาการ

- การทดสอบ

- ที่

- พื้นที่

- พวกเขา

- แล้วก็

- ที่นั่น

- พวกเขา

- สิ่ง

- คิด

- คิดว่า

- นี้

- ตลอด

- ความสัมพันธ์

- เวลา

- ไปยัง

- เกินไป

- เอา

- ด้านบน

- หัวข้อ

- จริง

- ที่สุด

- ภายใต้

- บันทึก

- ใช้

- มักจะ

- ความคุ้มค่า

- ผู้ขาย

- ผู้ขาย

- มาก

- ผ่านทาง

- ปริมาณ

- vp

- ต้องการ

- คือ

- คลื่น

- we

- ไป

- คือ

- อะไร

- เมื่อ

- ที่

- WHO

- จะ

- กับ

- แย่ลง

- ปี

- เธอ

- ลมทะเล