วลีเก่าที่การรักษานั้นแย่กว่าโรคนั้นพอประมาณเมื่อพูดถึง MBIST สำหรับ SOC ขนาดใหญ่ ซึ่งการทดสอบ MBIST แบบคู่ขนานกันอาจใช้ความสามารถเกินความสามารถของเครือข่ายการกระจายพลังงาน (PDN) การทดสอบตัวเองในตัวของหน่วยความจำ (MBIST) มักจะทำงานโดยอัตโนมัติระหว่างเปิดเครื่องเหตุการณ์ เนื่องจากต้องการเร่งความเร็วในการทดสอบและเวลาบูตชิป การทดสอบเหล่านี้จึงมักดำเนินการควบคู่กัน ปัญหาคือพวกเขาสามารถสร้างกิจกรรมการสลับที่มีลำดับความสำคัญสูงกว่าระดับที่พบในระหว่างการทำงานของชิปปกติได้อย่างง่ายดาย อันที่จริง ระดับกิจกรรมการเปลี่ยนที่สูงขึ้นเหล่านี้ไม่เพียงแต่จะทำให้อุปทานลดลงซึ่งส่งผลต่อผลการทดสอบเท่านั้น แต่ความร้อนสูงที่เกิดขึ้นอาจเป็นอันตรายต่อชิปได้ ผลกระทบเหล่านี้สามารถนำไปสู่ความผิดพลาดหรือเหตุการณ์โดยตรงและความล้มเหลวแฝง

วิธีแก้ไขคือการจำลองกิจกรรม MBIST เพื่อทำนายภาระบน PDN และผลกระทบจากความร้อนที่เกี่ยวข้อง ด้วยผลการจำลองในมือ นักออกแบบสามารถตัดสินใจได้อย่างถูกต้องว่าจำนวนบล็อกหน่วยความจำใดที่สามารถทดสอบแบบคู่ขนานกันได้ อย่างไรก็ตาม สิ่งนี้ไม่สามารถทำได้ใน SOC ขนาดใหญ่ที่มีบล็อกหน่วยความจำจำนวนมาก เนื่องจากเวลาในการจำลองอาจเป็นสิ่งที่ห้ามปราม ด้วยระดับเกตและการจำลอง RTL ที่แม่นยำน้อยกว่า อาจเป็นไปไม่ได้ที่จะเรียกใช้รอบมากพอที่จะรับข้อมูลที่จำเป็น

ในเอกสารไวท์เปเปอร์เรื่อง “การวิเคราะห์ผลกระทบด้านพลังงานของการใช้ MBIST” ซีเมนส์ EDA พิจารณาว่านักออกแบบสามารถเรียกใช้การจำลองที่เพียงพอเพื่อตัดสินใจอย่างมีข้อมูลในกลยุทธ์การทดสอบก่อนออกเทปได้อย่างไร ซีเมนส์ทำงานร่วมกับ ARM ในชิปทดสอบตัวใดตัวหนึ่งเพื่อสร้างกรณีทดสอบที่พวกเขาสามารถใช้การจำลองฮาร์ดแวร์กับแอป DFT และ Power สำหรับ Veloce ตัวจำลองฮาร์ดแวร์ของ Siemens ขั้นแรก แอป Veloce DFT ใช้เพื่อส่งออกกิจกรรมภายในระหว่างการจำลอง MBIST แอปใช้ภาษาอินเทอร์เฟซการทดสอบมาตรฐาน (STIL) และสร้างไฟล์เอาต์พุตมาตรฐานอุตสาหกรรม

แอป Veloce Power ใช้ข้อมูลกิจกรรมจากการวิ่งของ MBIST เพื่อสร้างรูปคลื่น โปรไฟล์พลังงาน และแผนที่ความร้อนที่สามารถระบุได้เมื่อมีกระแสไฟเกินขีดจำกัดที่กำหนด ด้วยข้อมูลนี้ วิศวกรทดสอบสามารถตัดสินใจเกี่ยวกับการจัดลำดับของ MBIST ได้อย่างมีข้อมูล

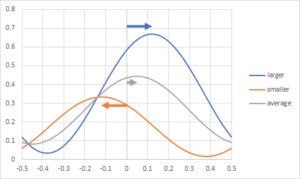

กรณีทดสอบ ARM ที่อธิบายไว้ในเอกสารไวท์เปเปอร์ของซีเมนส์มีประตู 176 ล้านประตู ซีเมนส์ใช้ระบบ Veloce พร้อมแผง Veloce Strato 6 แผ่นสำหรับกรณีทดสอบนี้ การรันโปรแกรมจำลอง Veloce ใช้เวลาเพียง 26 ชั่วโมง ซึ่งเร็วกว่าการจำลองระดับเกต 15,600 เท่า ประโยชน์อีกประการของโฟลว์ Veloce คือข้อมูลกิจกรรมถูกสตรีมโดยแอป Power ไปยังเครื่องมือไฟฟ้าในโฟลว์ ซึ่งช่วยประหยัดพื้นที่และเวลาในดิสก์ ผลลัพธ์จากกรณีทดสอบแสดงให้เห็นว่ามีไฟกระชากหลายจุดซึ่งละเมิดข้อกำหนดการออกแบบ SOC เอาต์พุตจากแอป Veloce Power จะแสดงระดับพลังงานทั้งหมดผ่านการจำลองพร้อมกับการจ่ายพลังงานที่แยกจากกันสำหรับนาฬิกา ตรรกะเชิงผสม และหน่วยความจำ ในทำนองเดียวกัน มีข้อมูลเกี่ยวกับตำแหน่งที่ใช้พลังงานจากแม่พิมพ์ ข้อมูลนี้ทำให้ง่ายต่อการระบุจุดที่มีปัญหา

การค้นหาปัญหาเหล่านี้ต้องใช้รอบนาฬิกาหลายล้านหรือพันล้านรอบ ข้อจำกัดของโปรแกรมจำลองซอฟต์แวร์ทำให้ไม่สามารถดำเนินการวิเคราะห์ที่จำเป็นได้ การจำลองเป็นช่องทางพิเศษในการตรวจสอบผลกระทบด้านพลังงานของ MBIST และการดำเนินการทดสอบอื่นๆ ก่อนเกิดซิลิคอนอย่างใกล้ชิด เอกสารไวท์เปเปอร์ของซีเมนส์ให้ข้อมูลเชิงลึกเกี่ยวกับวิธีการใช้พลังงานที่ใช้กับกรณีทดสอบจริง เอกสารไวท์เปเปอร์สามารถดาวน์โหลดได้จากเว็บไซต์ของซีเมนส์

แชร์โพสต์นี้ผ่าน: ที่มา: https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- เกี่ยวกับเรา

- การวิเคราะห์

- app

- ปพลิเคชัน

- ARM

- ใช้ได้

- กำลัง

- ก่อให้เกิด

- ชิป

- ชิป

- นาฬิกา

- มี

- ได้

- รักษา

- ออกแบบ

- โรค

- ในระหว่าง

- อย่างง่ายดาย

- วิศวกร

- เหตุการณ์

- เหตุการณ์

- เร็วขึ้น

- ชื่อจริง

- ไหล

- พบ

- เกตส์

- สร้าง

- ฮาร์ดแวร์

- จุดสูง

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- HTTPS

- อุตสาหกรรม

- ข้อมูล

- IT

- ภาษา

- ใหญ่

- นำ

- ชั้น

- ระดับ

- โหลด

- นาน

- แผนที่

- ล้าน

- ล้าน

- จำเป็น

- เครือข่าย

- เสนอ

- การดำเนินการ

- ใบสั่ง

- อื่นๆ

- กระดาษ

- อำนาจ

- ปัญหา

- ดูรายละเอียด

- การอ่าน

- ผลสอบ

- วิ่ง

- วิ่ง

- ประหยัด

- ซีเมนส์

- จำลอง

- ซอฟต์แวร์

- ช่องว่าง

- ความเร็ว

- กลยุทธ์

- สตรีม

- จัดหาอุปกรณ์

- ระบบ

- ทดสอบ

- การทดสอบ

- การทดสอบ

- ร้อน

- ตลอด

- เวลา

- เครื่องมือ

- เป็นเอกลักษณ์

- มักจะ

- Website

- กระดาษสีขาว

- ทำงาน