Universal Verification Methodology (UVM) เป็นวิธีที่ได้รับความนิยมในการช่วยตรวจสอบการออกแบบ SystemVerilog และประกอบด้วย ระบบการกำหนดค่า น่าเสียดายที่มีปัญหาด้านความเร็วและการใช้งานอยู่บ้าง Rich Edelman จาก Siemens EDA ได้เขียนรายงานที่มีรายละเอียดจำนวน 20 หน้าในหัวข้อวิธีหลีกเลี่ยงปัญหาเหล่านี้ และฉันได้อ่านบทความนี้เพื่อสรุปประเด็นสำคัญสำหรับคุณแล้ว วิศวกรตรวจสอบใช้ฐานข้อมูลการกำหนดค่า UVM เพื่อตั้งค่า จากนั้นจึงรับค่าในภายหลังในการทดสอบ UVM ตัวอย่างหนึ่งของการตั้งค่าและรับค่า 'T' คือ:

uvm_config#(T)::set(ขอบเขต, instance_path_name, field_name, ค่า); uvm_config#(T)::get(ขอบเขต, instance_path_name, field_name, ค่า);

การเชื่อมต่อม้านั่งทดสอบ UVM กับอุปกรณ์ที่ทดสอบจะใช้ฐานข้อมูลการกำหนดค่าเพื่อส่งผ่านอินเทอร์เฟซเสมือน มีปัญหาสามประการในการใช้การกำหนดค่า UVM:

- โค้ดขนาดใหญ่ โค้ดประมาณ 2,600 บรรทัด

- ต้องมีการจับคู่ประเภทที่ตรงกัน ดังนั้น 'int' และ 'bit' จึงไม่เหมือนกัน

- รหัสช้า

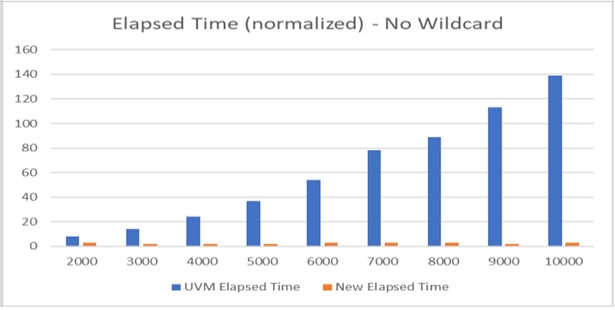

ลองพิจารณากรณีของโค้ดที่ช้า เนื่องจากการเรียกใช้ set() นับพันครั้งโดยใช้ชื่อที่มีไวด์การ์ดอาจใช้เวลานานถึง 30 นาทีในการทำให้เฟส 'set' และ 'get' เสร็จสมบูรณ์

Rich เสนอโซลูชันใหม่สำหรับการกำหนดค่า UVM ที่มีความเร็วที่เร็วกว่ามาก โดยใช้เวลาเพียงไม่กี่วินาทีในการเปรียบเทียบ

หากโค้ด UVM ของคุณหลีกเลี่ยงการใช้ไวด์การ์ดและมีคำสั่ง 'set' เพียงไม่กี่คำสั่ง โค้ดของคุณก็จะทำงานเร็วขึ้น

วิธีแก้ไขที่เป็นไปได้สำหรับปัญหาการกำหนดค่า UVM ได้แก่:

- ใช้ตัวแปรร่วมแทน

- ใช้การกำหนดค่า UVM กับหนึ่งชุด ()

- ใช้การกำหนดค่า UVM กับชุดไม่กี่ชุด ()

- ใช้แผนผังการกำหนดค่า

- ลองทำสิ่งที่แตกต่าง

วิธีสุดท้ายในการลองสิ่งที่แตกต่างออกไปคือโซลูชันใหม่ และยังคงใช้ set() และ get() API จากนั้นลดความซับซ้อนลงโดยลบการกำหนดพารามิเตอร์ของการกำหนดค่า ลบลำดับความสำคัญออก และลบการเปลี่ยนแปลงอัลกอริทึมการค้นหา ผลลัพธ์ของแนวทางใหม่นี้คือความเร็วที่รวดเร็ว

รายการการกำหนดค่าใหม่ของคุณถูกกำหนดไว้ในคลาสที่ได้รับจาก 'config_item' และตัวอย่างด้านล่างแสดง 'int value' เป็นคุณสมบัติที่กำลังตั้งค่า เพื่อวัตถุประสงค์ในการแก้ไขข้อบกพร่อง คุณจะต้องเพิ่มฟังก์ชัน Pretty-print

คลาส my_special_config_item ขยาย config_item;

ฟังก์ชั่นใหม่ (ชื่อสตริง = "my_special_config_item");

super.ใหม่ (ชื่อ);

ฟังก์ชั่นสุดท้าย

ค่า int;

สตริงฟังก์ชันเสมือน Convert2string();

กลับ $sformatf("%s - value=%0d ", get_name(), value, super.convert2string());

ฟังก์ชั่นสุดท้าย

คลาสสุดท้าย

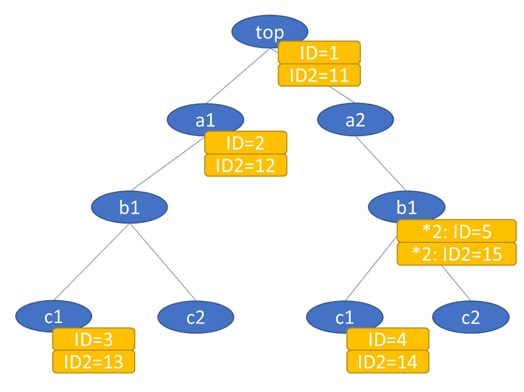

'config_item' มีแอตทริบิวต์ชื่อ และชื่อนี้จะถูกค้นหา บวกกับชื่ออินสแตนซ์ วัตถุการกำหนดค่ายังมีฟังก์ชัน get_name() เพื่อส่งคืนชื่อ หากต้องการค้นหา “instance_name.field_name” ใดๆ ฐานข้อมูลการกำหนดค่าจะใช้อาร์เรย์ที่เชื่อมโยงเพื่อความเร็วในการค้นหาและการสร้างที่รวดเร็ว

สำหรับการตรวจสอบย้อนกลับ คุณสามารถค้นหาได้ว่าใครเป็นคนตั้งค่าหรือใครเป็นผู้เรียก get เนื่องจากชื่อไฟล์และหมายเลขบรรทัดเป็นฟิลด์ในการเรียกใช้ฟังก์ชัน set() และ get()

ชุด (null, "top.a.b.*", "ความเร็ว", my_speed_config, `__FILE__, `__LINE__) รับ (null, "top.a.b.c.d.monitor1", "ความเร็ว", speedconfig, `__FILE__, `__LINE__)

สามารถพิมพ์คิวตัวเข้าถึงได้ในระหว่างการดีบักเพื่อดูว่าใครเป็นผู้เรียก set() และ get()

เพื่อรองรับไวด์การ์ด จำเป็นต้องเพิ่มกลไกการค้นหาโดยใช้คอนเทนเนอร์ พิจารณาชื่ออินสแตนซ์ 'top.a.b.c.d.*_0'

ส่วนไวด์การ์ดของชื่ออินสแตนซ์ได้รับการจัดการโดยใช้แผนผังคอนเทนเนอร์ แทนอาร์เรย์ที่เชื่อมโยง

สรุป

การแบ่งปันข้อมูลระหว่างโมดูล/อินสแตนซ์และโลกตามคลาสในเครื่องทดสอบ UVM สามารถทำได้โดยใช้ฐานข้อมูลการกำหนดค่า UVM เพียงระวังการชะลอตัวของความเร็ว หากวิธีการของคุณใช้การกำหนดค่าจำนวนมาก ให้ลองใช้แนวทางใหม่ที่นำเสนอซึ่งมีแพ็คเกจที่ใช้โค้ดประมาณ 300 บรรทัด แทนที่จะเป็นโค้ด 2,600 บรรทัดในไฟล์ฐานข้อมูลการกำหนดค่า UVM

อ่านบทความเต็ม 20 หน้า หลีกเลี่ยงความบ้าคลั่งในการกำหนดค่าด้วยวิธีง่ายๆ ที่ Siemens EDA

บล็อกที่เกี่ยวข้อง

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- PlatoData.Network Vertical Generative Ai เพิ่มพลังให้กับตัวเอง เข้าถึงได้ที่นี่.

- เพลโตไอสตรีม. Web3 อัจฉริยะ ขยายความรู้ เข้าถึงได้ที่นี่.

- เพลโตESG. คาร์บอน, คลีนเทค, พลังงาน, สิ่งแวดล้อม แสงอาทิตย์, การจัดการของเสีย. เข้าถึงได้ที่นี่.

- เพลโตสุขภาพ เทคโนโลยีชีวภาพและข่าวกรองการทดลองทางคลินิก เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/eda/339885-making-uvm-faster-through-a-new-configuration-system/

- :มี

- :เป็น

- :ไม่

- $ ขึ้น

- 30

- 300

- 600

- a

- เกี่ยวกับเรา

- เพิ่ม

- เพิ่ม

- ขั้นตอนวิธี

- ด้วย

- an

- และ

- ใด

- API

- เข้าใกล้

- เป็น

- แถว

- AS

- At

- หลีกเลี่ยง

- ทราบ

- b

- BE

- เพราะ

- กำลัง

- ด้านล่าง

- ระหว่าง

- by

- ที่เรียกว่า

- โทร

- CAN

- กรณี

- เปลี่ยนแปลง

- ชั้น

- รหัส

- การเปรียบเทียบ

- สมบูรณ์

- องค์ประกอบ

- พิจารณา

- ภาชนะ

- ภาชนะบรรจุ

- อย่างต่อเนื่อง

- การสร้าง

- ข้อมูล

- ฐานข้อมูล

- กำหนด

- ที่ได้มา

- การออกแบบ

- รายละเอียด

- เครื่อง

- ต่าง

- ทำ

- ในระหว่าง

- ง่าย

- วิศวกร

- อีเธอร์ (ETH)

- ตัวอย่าง

- ขยาย

- FAST

- เร็วขึ้น

- สองสาม

- สาขา

- เนื้อไม่มีมัน

- หา

- สำหรับ

- ราคาเริ่มต้นที่

- เต็ม

- ฟังก์ชัน

- ได้รับ

- ได้รับ

- เหตุการณ์ที่

- ไป

- ช่วย

- ไฮไลท์

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- ทำอย่างไร

- HTTPS

- if

- in

- รวมถึง

- ตัวอย่าง

- แทน

- อินเตอร์เฟซ

- แนะนำ

- ปัญหา

- IT

- jpg

- เพียงแค่

- ชื่อสกุล

- ต่อมา

- Line

- เส้น

- มอง

- ค้นหา

- จำนวนมาก

- การทำ

- การจับคู่

- ความกว้างสูงสุด

- กลไก

- ระเบียบวิธี

- นาที

- นาที

- มาก

- ชื่อ

- ชื่อ

- ใหม่

- โซลูชั่นใหม่

- จำนวน

- วัตถุ

- of

- on

- ONE

- เพียง

- or

- ออก

- แพ็คเกจ

- กระดาษ

- ส่วนหนึ่ง

- ส่ง

- ระยะ

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- บวก

- ยอดนิยม

- โพสต์

- ลำดับความสำคัญ

- ปัญหาที่เกิดขึ้น

- คุณสมบัติ

- เสนอ

- วัตถุประสงค์

- ลบ

- ลบ

- จำเป็นต้องใช้

- ผลสอบ

- กลับ

- รวย

- วิ่ง

- ขอบเขต

- วินาที

- เห็น

- ชุด

- การตั้งค่า

- แสดงให้เห็นว่า

- ซีเมนส์

- ช่วยลดความยุ่งยาก

- ช้า

- ชะลอตัว

- So

- ทางออก

- โซลูชัน

- บาง

- บางสิ่งบางอย่าง

- ความเร็ว

- ความเร็ว

- เชือก

- สรุป

- ยิ่งใหญ่

- สนับสนุน

- ระบบ

- T

- เอา

- การ

- ทดสอบ

- ที่

- พื้นที่

- ของพวกเขา

- แล้วก็

- ที่นั่น

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- นี้

- พัน

- สาม

- ตลอด

- เวลา

- ไปยัง

- ด้านบน

- หัวข้อ

- ตรวจสอบย้อนกลับ

- ต้นไม้

- พยายาม

- ชนิด

- ภายใต้

- น่าเสียดาย

- สากล

- การใช้

- ใช้

- ใช้

- การใช้

- ความคุ้มค่า

- ความคุ้มค่า

- ตัวแปร

- การตรวจสอบ

- ตรวจสอบ

- ผ่านทาง

- เสมือน

- ทาง..

- ที่

- WHO

- จะ

- กับ

- โลก

- เขียน

- เธอ

- ของคุณ

- ลมทะเล