การกัดด้วยพลาสมาอาจเป็นกระบวนการที่สำคัญที่สุดในการผลิตเซมิคอนดักเตอร์ และอาจเป็นกระบวนการที่ซับซ้อนที่สุดในบรรดาการทำงานที่ยอดเยี่ยมรองจากโฟโต้ลิโทกราฟี เกือบครึ่งหนึ่งของขั้นตอน fab ทั้งหมดอาศัยพลาสม่าซึ่งเป็นก๊าซไอออไนซ์ที่มีพลังในการทำงาน

แม้ว่าทรานซิสเตอร์และเซลล์หน่วยความจำจะลดขนาดลงเรื่อยๆ แต่วิศวกรยังคงนำเสนอกระบวนการแกะสลักที่เชื่อถือได้

“เพื่อสร้างชิปอย่างยั่งยืนด้วยความแม่นยำระดับนาโนและโครงสร้างต้นทุนที่เหมาะสม ผู้ผลิตอุปกรณ์ wafer fab จำเป็นต้องผลักดันขอบเขตของฟิสิกส์พลาสมา วิศวกรรมวัสดุ และวิทยาศาสตร์ข้อมูล เพื่อส่งมอบโซลูชั่นอุปกรณ์ที่จำเป็น” กล่าวโดย Thomas Bondur รองประธานบริษัท Etch Product Group ทำการตลาดที่ การวิจัยลำ. ไม่มีที่ใดจะชัดเจนไปกว่าการกัดด้วยพลาสมา ซึ่งทำงานร่วมกับการพิมพ์หินเพื่อสร้างคุณสมบัติที่แม่นยำและทำซ้ำได้บนแผ่นเวเฟอร์

รายงานนี้ตรวจสอบขั้นตอนการจำหลักที่สำคัญใน 3D NAND, DRAM, nanosheet FET และการเชื่อมต่อระหว่างกัน โดยมองไปข้างหน้าที่อุปกรณ์ 2 มิติและการประมวลผลแบ็คเอนด์ที่มีงบประมาณต่ำ อุตสาหกรรมนี้กำลังแสวงหาเคมีกัดกรดที่ยั่งยืนมากขึ้นเพื่อลด COXNUMX ที่เทียบเท่า2 การปล่อยมลพิษจาก fabs

สำหรับผู้ผลิตเครื่องมือจำนวนมาก การสร้างแบบจำลองกระบวนการมีบทบาทสำคัญในการพัฒนากระบวนการแกะสลัก เป้าหมายคือเพื่อลดระยะเวลาในการวางตลาดในขณะที่ลดต้นทุนแผ่นเวเฟอร์และหน้ากาก

Barrett Finch ผู้อำนวยการอาวุโสฝ่ายการตลาดของ Lam Research กล่าวว่า "การปรับแต่งกระบวนการ Etch ในขั้นตอนที่ยุ่งยากที่สุดบางขั้นตอนอาจใช้เวลาหนึ่งปีหรือมากกว่านั้นจึงจะเสร็จสมบูรณ์ “เมื่อเร็วๆ นี้ เราเสร็จสิ้นงานจำลองกระบวนการบางอย่างภายในสามสัปดาห์ ซึ่งคาดว่าจะใช้เวลาสามเดือนโดยใช้การทดสอบและพัฒนาที่ใช้ซิลิคอนโดยทั่วไป”

จำนวนเงินนี้อาจสูงถึงหลายแสนหรือแม้แต่หลายล้านดอลลาร์สำหรับค่าหน้ากากและเวเฟอร์สำหรับผู้ผลิตอุปกรณ์เท่านั้น

พื้นฐานการแกะสลัก

กระบวนการแกะสลักทำงานร่วมกับการพิมพ์หิน การกัดโดยทั่วไปจะนำหน้าด้วยการทับถมของฟิล์ม (โดยการสะสมของ epitaxy, สารเคมีหรือไอกายภาพ เป็นต้น) โดยทั่วไป ก ซีวีดี ฟิล์มถูกเคลือบด้วย ช่างถ่ายภาพ แล้วนำมาตีแผ่ผ่านลวดลาย เส้นเล็ง (หน้ากาก)โดยใช้ การพิมพ์หินด้วยแสง (248nm หรือ 193nm UV, 13.5nm EUV) ต่อต้านการพัฒนาแล้วเผยให้เห็นรูปแบบ ในห้องกัดพลาสมาเวเฟอร์เดี่ยว โดยทั่วไปแล้วสารเคมีที่ใช้กัดและไอออนจะระดมยิงและนำฟิล์ม CVD ออกโดยที่ช่างภาพขาดหายไป (ในการต้านทานโทนบวก) หลังจากการกัดกรด ให้ต้านทานขี้เถ้า การทำความสะอาดด้วยสารเคมีแบบเปียก และ/หรือการกัดแบบเปียกเพื่อขจัดสิ่งตกค้าง

กระบวนการกัดด้วยพลาสมาสามารถจัดกลุ่มคร่าวๆ ได้ว่าเป็นอิเล็กทริก ซิลิกอน หรือตัวนำกัดกรด ไดอิเล็กทริก เช่น ซิลิกอนไดออกไซด์และซิลิกอนไนไตรด์จะกัดได้ดีที่สุดโดยใช้ก๊าซฟลูออรีน ในขณะที่ชั้นซิลิกอนและโลหะจะทำปฏิกิริยากับสารเคมีคลอรีนได้ดีที่สุด โดยพื้นฐานแล้วมีโหมดการกัดแบบแห้งสามโหมด ได้แก่ การกัดด้วยไอออนแบบรีแอกทีฟ การกัดด้วยพลาสมา และการกัดแบบสปัตเตอร์ (ลำแสงไอออน) กระบวนการแกะสลักนั้นเกี่ยวกับปฏิสัมพันธ์ที่ซับซ้อนระหว่างสารตั้งต้นทางเคมี พลาสมา และวัสดุแผ่นเวเฟอร์ เมื่อใช้ RF bias กับก๊าซปฏิกิริยา อิเล็กตรอนและไอออนที่มีประจุบวกจะโจมตีแผ่นเวเฟอร์เพื่อกำจัดวัสดุ (กัด) ในขณะที่สารเคมีและอนุมูลอิสระทำปฏิกิริยากับวัสดุที่สัมผัสเพื่อสร้างผลพลอยได้ที่ระเหยได้ การกัดสามารถเป็นได้ทั้งแบบไอโซทรอปิก (ทำปฏิกิริยาเท่ากันในแนวตั้งและแนวนอน) แบบแอนไอโซทรอปิก (เฉพาะในแนวตั้ง) หรือที่ไหนสักแห่งในระหว่างนั้น

รูปที่ 1: การเปลี่ยนจาก finFET เป็น GAA ทำให้เกิดข้อกำหนดการเลือกกัดแบบไอโซโทรปิกที่สำคัญ ที่มา: วิจัยลำ

เมตริกที่วิศวกรจำหลักให้ความสำคัญที่สุดคืออัตราการกัด การควบคุมโปรไฟล์ ความสม่ำเสมอ (ทั่วทั้งแผ่นเวเฟอร์) และการเลือกจำหลัก เนื่องจากสิ่งเหล่านี้ส่งผลต่อผลผลิตและผลผลิต ความสามารถในการกัดกัดเป็นเพียงอัตราส่วนของการนำวัสดุที่คุณต้องการกัดออกโดยสัมพันธ์กับเลเยอร์ด้านล่าง ตัวอย่างเช่น SiO2 บนซิลิกอน ระหว่างการกัดลาย ข้อดีอีกอย่างคือการไม่ดึงช่างภาพออกมากเกินไป แต่เมื่อเป็นกรณีนี้ รูปแบบมักจะถูกถ่ายโอนไปยังหน้ากากแข็ง (ซิลิกอนไดออกไซด์, ซิลิกอนไนไตรด์, SiOC, TiN) ก่อนที่จะถูกถ่ายโอนไปยังฟิล์มด้านล่าง

ข้อกำหนดการเลือกใช้หัวกะทิแตกต่างกันไปตั้งแต่ 2:1 ถึง 1,000:1 (จำหลักแบบเลือกสูง) ด้วยโหนดใหม่แต่ละโหนด ข้อกำหนดเหล่านี้จะเข้มงวดยิ่งขึ้น Philippe Bézard วิศวกร R&D R&D ของ Dry etch กล่าวว่า “เมื่อค่า NA EUV สูงเริ่มเข้ามาแทนที่ EUV ปกติภายในสี่ปีข้างหน้า โฟกัสจะต่ำกว่ามาก ดังนั้นคุณจึงไม่สามารถเปิดรับช่างภาพที่มีความหนาได้อีกต่อไป และโดยความหนาหมายถึง 30 นาโนเมตร” Philippe Bézard วิศวกร R&D ของ dry etch ที่ อิมเมค “แต่คุณยังต้องสร้างความหนาของฟิล์มด้านล่างให้เท่ากัน ดังนั้นตอนนี้คุณกำลังขอให้มีการเลือกที่สูงขึ้นมากในแง่ที่ว่าแทนที่จะเป็น 2:1 เราต้องไปให้ถึงมากขึ้นเช่น 10:1 ซึ่งเป็นการปรับปรุงการเลือกอย่างฉับพลัน 4X ถึง 5X”

ตั้งแต่การพิสูจน์แนวคิด (POC) ไปจนถึงการผลิตในปริมาณมาก (HVM)

เบซาร์ดอธิบายถึงสามขั้นตอนของการพัฒนากระบวนการแกะสลัก:

- การพิจารณาว่าอีทเชอร์ ก๊าซ ชั้นเสริม ฯลฯ ใดที่จำเป็นในการกัดกัด

- การสาธิตประสิทธิภาพการลอกฟิล์มออกทั้งหมดตามข้อกำหนดด้วยความสม่ำเสมอของกระบวนการในเวเฟอร์หนึ่งแผ่น และ

- การพิจารณาว่ากระบวนการสามารถทำซ้ำในเวเฟอร์หลายพันแผ่นใน HVM ด้วยผลตอบแทนสูงและการเลื่อนลอยเพียงเล็กน้อยได้อย่างไร

โดยทั่วไปแล้ว วิศวกรการแกะสลักและการบูรณาการที่มีทักษะจะจัดการกับสองขั้นตอนแรกของการพัฒนา ขั้นตอนที่สามอาจใช้ความเชี่ยวชาญด้านวิศวกรรมอีกครั้ง แต่แมชชีนเลิร์นนิงอาจช่วยได้

“โดยทั่วไปการเรียนรู้ของเครื่องและการวิเคราะห์ข้อมูลจะมีประโยชน์ในระยะที่สามเท่านั้น” เขากล่าว “มันทรงพลังมากเพราะสามารถเข้าถึงข้อมูลได้มากมายและเข้าใจถึงสิ่งเล็กๆ ง่ายๆ นับล้านที่ล้วนมีปฏิสัมพันธ์กัน ดังนั้นการที่สมองของมนุษย์จะพยายามหาสิ่งนี้จึงเป็นเรื่องยากมาก แต่โปรแกรมคอมพิวเตอร์สามารถจัดการได้ง่ายกว่า แต่ในกรณีที่คุณมีแอปพลิเคชันใหม่ มีการแกะสลักวัสดุใหม่ หรือการผสานรวมใหม่ ก็ไม่ได้แสดงว่ามีการปรับปรุงใด ๆ เหนือมนุษย์”

การใช้ ML ยังเกี่ยวข้องกับต้นทุนการผลิตอีกด้วย เนื่องจากเวเฟอร์หลายพันชิ้นถูกใช้ในเฟสที่สาม — อย่างน้อยลำดับความสำคัญก็ใหญ่กว่าที่ใช้ในเฟสหนึ่งและสอง

Barrett Finch ผู้อำนวยการอาวุโสของ Etch Product Group ที่ Lam Research อธิบายถึงกระบวนการค้นหาเส้นทางใหม่ว่าเป็นการพิสูจน์แนวคิดจากโฟลว์และเลย์เอาต์ของกระบวนการที่ระบุ และการพัฒนาอุปกรณ์ทำงานอย่างน้อยหนึ่งอย่างบนแผ่นเวเฟอร์ จากนั้น POC นี้จะถูกโอนไปยังทีมพัฒนาผลิตภัณฑ์ใน fab เพื่อขยายขนาดกระบวนการและปรับปรุงผลผลิต

Finch กล่าวว่า "ปริมาณงานที่ต้องใช้ในการแปลงแนวคิดการพิสูจน์เพียงเล็กน้อยให้เป็นผลิตภัณฑ์ที่ให้ผลตอบแทนจริงมักถูกประเมินต่ำเกินไป และสิ่งนี้ทำให้เกิดช่องว่างขนาดใหญ่ในการทำกำไร" Finch กล่าว “การสร้างแบบจำลองหน้าต่างกระบวนการพยายามปิดช่องว่างนี้โดยแนะนำการเปลี่ยนแปลงที่ยอดเยี่ยมในช่วงเริ่มต้นของการค้นหาเส้นทาง R&D” เขาแนะนำว่า DOE เสมือนและการวิเคราะห์ตามมอนติคาร์โลในพารามิเตอร์กระบวนการจำนวนหนึ่งทดสอบ POC โดยการจำลองความแปรปรวนที่คาดไว้

“การสร้างแบบจำลองหน้าต่างกระบวนการสามารถตอบคำถามที่ว่า 'ฉันต้องรักษาซีดีหรือระดับความแปรปรวนใดเพื่อให้ได้ประสิทธิภาพและผลผลิตของอุปกรณ์ขั้นต่ำ' เราได้เสร็จสิ้นการทดสอบหน้าต่างกระบวนการเสมือนด้วยเวเฟอร์เสมือนมากกว่า 1 ล้านแผ่นในเวลาไม่กี่วัน ซึ่งคงเป็นไปไม่ได้ที่จะทำสำเร็จในชีวิตจริง” เขากล่าว

พารามิเตอร์หลายตัวส่งผลต่ออัตราการกัด โปรไฟล์ และการเลือก กุญแจสำคัญคืออุณหภูมิ “ลูกค้าของเรามองเห็นผลกระทบของผลกระทบจากความร้อนในกระบวนการกัดกรด เนื่องจากพวกเขาควบคุมอัตราการกัด การเลือก และโปรไฟล์การกัด พารามิเตอร์ทั้งหมดเหล่านี้สามารถส่งผลกระทบต่อทั้งผลผลิตของอุปกรณ์และผลผลิตที่ยอดเยี่ยม” เบนจามิน วินเซนต์ ผู้จัดการอาวุโสด้านวิศวกรรมกระบวนการเซมิคอนดักเตอร์และบูรณาการของ Lam Research กล่าว เขาเชื่อว่าการจำลองอาจมีประโยชน์อย่างยิ่งเมื่อขั้นตอนของกระบวนการมีการกำหนดค่าที่เป็นไปได้หลายรายการ (พื้นที่ของกระบวนการมีขนาดใหญ่) หรือในกรณีที่ผลลัพธ์ปลายทางจากขั้นตอนนั้นคาดเดาไม่ได้อย่างมาก

Alex Guermouche ผู้จัดการฝ่ายการตลาดผลิตภัณฑ์ของ Esgee Technologies กล่าวว่า "กระบวนการกัดนั้นขึ้นอยู่กับอุณหภูมิพื้นผิวของแผ่นเวเฟอร์ ซึ่งขึ้นอยู่กับฟลักซ์ความร้อนหลายชนิด เช่น การนำความร้อน พลังงานไอออนกระทบ ปฏิกิริยาที่พื้นผิว และฟลักซ์ความร้อนที่แผ่รังสีจากพลาสมา" บริษัท แลม รีเสิร์ช. “ด้วยเหตุนี้ แบบจำลองพลาสมาจึงจำเป็นต้องรวมคุณสมบัติทางฟิสิกส์เหล่านี้ทั้งหมดเพื่อแสดงให้เห็นการเปลี่ยนแปลงของอุณหภูมิบนพื้นผิวของแผ่นเวเฟอร์ได้อย่างแม่นยำ ซอฟต์แวร์จำลองกระบวนการสามารถสร้างแบบจำลองคุณลักษณะการกัดได้หลากหลาย ทำให้เราได้ผลลัพธ์การกัดที่ดีขึ้นเร็วขึ้น และเร่งความสามารถของลูกค้าในการเพิ่มการผลิตหรือเพิ่มผลผลิตให้เหมาะสม”

ระยะเวลาที่แม่นยำของกระบวนการแกะสลัก

ด้วยรูปทรงเรขาคณิตที่แน่นขึ้นและฟิล์มที่บางลง จึงจำเป็นต้องรักษาสมดุลของอัตราการกัดด้วยการควบคุมที่ยอดเยี่ยมเหนือพารามิเตอร์การทำงานอื่นๆ

“ด้วยกฎการออกแบบที่หดตัว กระบวนการแกะสลักจำนวนมากกำลังก้าวไปสู่ขั้นตอนกระบวนการกัดด้วยพลาสมาที่รวดเร็วมาก ซึ่งต้องการการควบคุมที่แม่นยำสูงของอินพุตปฏิกิริยาทั้งหมด: พลังงาน ความดัน เคมี และอุณหภูมิ” ฟินช์กล่าว พร้อมสังเกตว่ายังมีแนวโน้มไปสู่พลาสมาที่เหมาะสมที่สุด พฤติกรรมการเต้นเป็นจังหวะเพื่อสร้างอัตราส่วนไอออนต่อความเป็นกลาง จากนั้นกวาดเอาผลพลอยได้ออกไป “การสร้างแบบจำลองขั้นสูงของเงื่อนไขดังกล่าวจะมีความสำคัญต่อการเปิดใช้งานการปรับขนาดอุปกรณ์เพิ่มเติม”

ผู้ผลิตระบบการแกะสลักได้ใช้ซอฟต์แวร์การสร้างแบบจำลองมาระยะหนึ่งแล้วเพื่อเพิ่มความเร็วในการพัฒนาโหนดถัดไปหรือเพิ่มผลผลิตทางลาด ไม่น่าแปลกใจเลย เนื่องจากความซับซ้อนของกระบวนการและตัวแปรทั้งหมด

“มีเวลาหรือเวเฟอร์ไม่เพียงพอที่จะดำเนินการทดลองกระบวนการที่เป็นไปได้ทั้งหมดเมื่อพัฒนาเทคโนโลยีโหนดถัดไป” Finch กล่าว “จำนวนชุดค่าผสมการตั้งค่าอุปกรณ์กัดอาจสูงถึงหลายล้านหรือหลายพันล้าน และการพัฒนาแผ่นเวเฟอร์แบบ brute force โดยใช้ความเป็นไปได้ของกระบวนการทั้งหมดนั้นเป็นไปไม่ได้เลย”

แน่นอนว่าโมเดลที่ดีทั้งหมดได้รับการตรวจสอบบนชิปจริง “แบบจำลองที่แม่นยำควรคาดการณ์ได้ และควรแก้ปัญหาเป้าหมายที่ผู้ใช้ต้องการแก้ไข” Finch กล่าว “ทุกครั้งที่มีการแนะนำการเปลี่ยนแปลงกระบวนการหรือการออกแบบตามงานจำลอง ข้อมูล fab จริงควรสะท้อนถึงผลลัพธ์ของคำแนะนำ ในกรณีของเรา เราสามารถคาดการณ์ผลกระทบของการเปลี่ยนแปลงกระบวนการได้อย่างแม่นยำโดยใช้ผลลัพธ์ตามแบบจำลอง และแก้ปัญหาการพัฒนาเทคโนโลยีและกระบวนการที่ยากได้อย่างรวดเร็ว”

ซัพพลายเออร์เครื่องมือกำลังทำงานบนกระบวนการแกะสลักขั้นสูงเพื่อรวมเส้นอย่างใกล้ชิดยิ่งขึ้นและเปลี่ยนสิ่งที่ครั้งหนึ่งเคยเป็นกระบวนการระดับสองหน้ากาก (สองขั้นตอนการพิมพ์หิน) ให้เป็นหนึ่งเดียวเพื่อลดความซับซ้อนของกระบวนการและลดต้นทุน

“แทนที่จะปรับฮาร์ดแวร์ที่มีอยู่เพื่อทำให้มีด Swiss Army มีอุปกรณ์ครบครันยิ่งขึ้น บริษัทต่าง ๆ กลับแนะนำเทคโนโลยีที่ใช้งานได้เฉพาะ เช่น ระบบใหม่เพื่อแก้ไขปัญหาแบบปลายต่อปลาย” เบซาร์ดกล่าว จุดมุ่งหมายคือการทำให้เส้นสองเส้นหันเข้าหากันใกล้กันมากขึ้น ซึ่งปัจจุบันเกี่ยวข้องกับขั้นตอนการวาดเส้นตามด้วยการตัดมาสก์ “สิ่งที่ Applied Materials และอื่น ๆ กำลังแนะนำคือวิธีการกัดโดยตรงในแนวนอน” กระบวนการดังกล่าวสามารถขยายผ่านรูได้เช่นกัน

ขั้นตอนจำหลักสำหรับนาโนชีต FET

ขั้นตอนจำหลักที่สำคัญที่สุดใน นาโนชีต โฟลว์ของกระบวนการรวมถึง Dummy Gate etch, anisotropicpillar etch, isotropic spacer etch และ channel release step [1] โปรไฟล์กัดผ่านชั้นสลับของซิลิคอนและ SiGe เป็นแอนไอโซโทรปิกและใช้เคมีฟลูออรีน การกัดสเปเซอร์ด้านใน (การเยื้อง) และขั้นตอนการปล่อยช่องได้รับการปรับให้เหมาะสมเพื่อกำจัด SiGe ด้วยการสูญเสียซิลิกอนที่ต่ำมาก

ขั้นตอนการเผยแพร่ช่องเป็นสิ่งสำคัญ Bézard กล่าวว่า "การเปิดตัวแผ่นนาโนต้องใช้การคัดเลือกที่สูงมาก “แผ่นนาโนส่วนใหญ่เป็นซิลิกอน จากนั้นเป็นซิลิกอน-เจอร์เมเนียมและซิลิกอน คุณมีเลเยอร์ที่สลับกัน และคุณต้องลบเลเยอร์หนึ่งออกโดยไม่แก้ไขเลเยอร์อื่นเลย” สิ่งพิมพ์บางฉบับได้กล่าวถึงการดำเนินการกัด SiGe แบบหลายขั้นตอนเพื่อลดความเครียดต่อโครงสร้างที่เกิดจากขั้นตอนการกัดเพียงครั้งเดียว

ถัดไปในกระบวนการคือการก่อตัวของหน้าสัมผัสที่จัดแนวเอง “นี่คือสิ่งที่เรากำลังพยายามทำโดยพื้นฐานแล้วกัดซิลิกอนไดออกไซด์และไม่สัมผัสหรือปิดซิลิกอนไนไตรด์ สมมุติว่าสเป็คปัจจุบันคือ 3nm ของร่อง แต่ผู้คนต่างร้องขอให้ไม่มีการสูญเสีย” Bézard กล่าว “ในกรณีนี้ เราไม่ได้ใช้คำว่าการเลือกสรรด้วยซ้ำ เราแค่พูดถึงการปิดภาคเรียน – และไม่มีการพักเลย”

3D NAND

สำหรับ 3D NAND แฟลชจำนวนเลเยอร์ยังคงเพิ่มขึ้นและจำเป็นต้องมีการใช้เลเยอร์ซ้อนกันหลายชั้นในอนาคต ในที่สุดก็สร้างสตริงแนวตั้งของอุปกรณ์ที่เรียงซ้อนกัน “นอกจากนี้ยังมีแรงผลักดันอีกมากในการปรับขนาด word line pitch หรือแนวตั้ง/Z-pitch ของเลเยอร์ เนื่องจากจำนวนเลเยอร์เพิ่มขึ้นเพื่อเพิ่มความหนาแน่นบิตต่อไป” Robert Clark สมาชิกอาวุโสของเจ้าหน้าที่ด้านเทคนิคและ ผู้อำนวยการฝ่ายเทคโนโลยี ที่ โทร. “จากมุมมองของกระบวนการ กระบวนการกัดและการสะสมจะต้องได้รับการปรับปรุงอย่างต่อเนื่องเพื่อรองรับอัตราส่วนภาพที่สูงขึ้นเรื่อย ๆ ในมิติวิกฤตที่เล็กลงเรื่อย ๆ ซึ่งจำเป็นต้องปรับขนาดอย่างต่อเนื่อง”

คลาร์กอธิบายการเปลี่ยนแปลงในอนาคต “เมื่อมองไปที่โหนดขั้นสูงของอุปกรณ์ดักจับประจุที่มีหลายชั้น จำเป็นต้องมีวิศวกรรมของสแต็กประตูเพื่อให้ได้ความยาวเกทที่สั้นลง ระดับต่อเซลล์ที่มากขึ้น และการปรับปรุงประสิทธิภาพการเขียนโปรแกรม ซึ่งอาจผ่านการใช้วัสดุคุณภาพสูง มีแนวโน้มว่าจะต้องใช้ช่องการนำไฟฟ้าที่สูงขึ้นเพื่อแทนที่ช่องโพลีศรีในอนาคตเช่นกัน” เขากล่าว

หนึ่งในการกัดที่สำคัญที่สุดใน 3D NAND เกี่ยวข้องกับการกัดลึกประมาณ 100 นาโนเมตรผ่านชั้นออกไซด์-ไนไตรด์หลายชั้น (200+ ชั้น) ซึ่งสามารถลึกได้ถึง 10µm Bézardจาก Imec กล่าวว่าขั้นตอนการจำหลักนี้มีราคาแพงเป็นพิเศษ

“เรามีปรากฏการณ์ทางกายภาพเกิดขึ้น ซึ่งเรียกว่าเอฟเฟกต์การชาร์จแบบดิฟเฟอเรนเชียล” เขากล่าว “ในพลาสมาเรามีอิเล็กตรอน ไอออน และสปีชีส์ที่เป็นกลางเพื่อทำให้ง่ายขึ้นมาก อิเล็กตรอนเคลื่อนที่ไปทุกทิศทุกทาง แต่ไอออนจะถูกเร่งในแนวตั้งฉากกับพื้นผิว ดังนั้นคุณจึงมีประจุบวกที่ด้านล่างของหลุมและประจุลบที่ด้านบน และคุณจะได้รับสนามไฟฟ้าที่พยายามขับไล่ไอออนที่เข้ามา”

ด้วยเหตุนี้ จึงจำเป็นต้องใช้ระดับพลังงานสูงในการกัดเซาะร่องลึกทั้งหมด “เรากำลังพยายามรักษากำลังไฟ 30 ถึง 50 กิกะวัตต์โดยไม่เกิดประกายไฟ ดังนั้นหัวจับจึงต้องได้รับการขัดเงาเป็นอย่างดีและผลิตมาอย่างดี” เขากล่าว

การกัดลึกยังทำให้เกิดแรงเค้นที่ต้องลดให้เหลือน้อยที่สุด โดยเฉพาะอย่างยิ่งเนื่องจากการผลิต NAND แบบหลายชั้นในภายหลังต้องใช้แผ่นเวเฟอร์ที่บางลง การจัดตำแหน่งที่แม่นยำ และการเชื่อมแบบไฮบริดไปยังระดับถัดไป

กระบวนการอื่นๆ

ไม่ใช่ผู้ผลิตชิปทุกรายที่ผลิตชิประดับแนวหน้าที่ต้องใช้การพิมพ์หิน EUV fabs จำนวนมากกำลังขยายกระบวนการ litho และ etch 193nm ของพวกเขา

Brian Wilbur ผู้อำนวยการฝ่ายกระจายผลิตภัณฑ์เซมิคอนดักเตอร์ที่ วิทยาศาสตร์การต้มเบียร์.

BEOL นามสกุล สำหรับเส้นโลหะที่แน่นที่สุดคาดว่าจะมีการเปลี่ยนแปลงอย่างมากจากแผนการรวมดามัสซีนแบบคู่ไปสู่การทับถมแบบลบและการแกะสลักของการเชื่อมต่อระหว่างกันนอกเหนือจากทองแดง ที่นี่ โลหะสองชนิด ได้แก่ รูทีเนียมและโมลิบดีนัม ได้รับการพัฒนาอย่างละเอียดถี่ถ้วนที่สุด อย่างไรก็ตาม โมลิบดีนัมมีแนวโน้มที่จะเกิดปฏิกิริยาออกซิไดซ์ระหว่างการแกะสลัก ทำให้เข้ากันได้กับโครงสร้างดามัสซีนคู่ รูทีเนียมเป็นโลหะมีตระกูล ดังนั้นจึงไม่มีปัญหาการกัดกร่อนเช่นเดียวกัน แต่มีราคาแพงกว่า

โครงสร้างอุปกรณ์ก็เริ่มไม่ทนทานเช่นกัน ข้อผิดพลาดในการวางขอบ. จำเป็นต้องมีแผนการใหม่สำหรับการปรับแนวตัวเองจากเลเยอร์หนึ่งไปยังอีกเลเยอร์หนึ่งและระหว่างจุดแวะกับเส้นตามข้อมูลของ TEL's Clark “การใช้งานครั้งแรกน่าจะเป็นสำหรับสิ่งต่าง ๆ เช่น บรรทัดคำที่ฝังอยู่ใน DRAM และชั้นโลหะ MOL พิทช์ขนาดเล็กสำหรับลอจิกที่ต้องการความเสถียรทางความร้อนที่สูงขึ้น รวมถึงความต้านทานต่ำหรือโลหะที่ไม่มีซับใน”

การพัฒนารุ่นต่อไป

ในระยะยาว อุตสาหกรรมจะเปลี่ยนไปใช้กระบวนการแบ็คเอนด์ที่มีงบประมาณด้านความร้อนต่ำกว่า (ใกล้ 300°C มากกว่า 400°C) เพื่อรวมอุปกรณ์เข้ากับเลเยอร์การเชื่อมต่อระหว่างแบ็คเอนด์

“อุตสาหกรรมมีความต้องการอย่างแท้จริงในการเริ่มสร้างอุปกรณ์ในชั้นต่างๆ มากขึ้น” Clark จาก TEL กล่าว “นั่นหมายความว่าเราต้องการหน่วยความจำและอุปกรณ์ลอจิกที่สร้างขึ้นภายใน BEOL ตามงบประมาณด้านความร้อนของ BEOL”

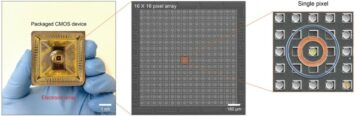

จนถึงตอนนี้ อุปกรณ์ที่ผลิตขึ้นโดยใช้สารกึ่งตัวนำออกไซด์ดูเหมือนจะมีแนวโน้มที่ดี ทั้งสำหรับการรวมอุปกรณ์หน่วยความจำเข้ากับโฟลว์ BEOL แบบลอจิก หรือสำหรับการสร้างอาร์เรย์ CMOS บนอาร์เรย์หน่วยความจำใน DRAM

การเปลี่ยนแปลงที่สำคัญอีกอย่างหนึ่งเกี่ยวข้องกับการรวมวัสดุ 2 มิติ ซึ่งสำนักวิจัยและผู้ผลิตชิปชั้นนำกำลังเริ่มทำการทดสอบแล้ว กำลังพิจารณากระบวนการกัดสำหรับวัสดุ เช่น ทังสเตนไดซัลไฟด์หรือโมลิบดีนัมไดซัลไฟด์ ภาพยนตร์ประกอบด้วยวัสดุเพียงชั้นเดียว ดังนั้นการพัฒนากระบวนการ fab เพื่อรวมเข้าด้วยกันจึงเป็นสิ่งที่ท้าทายอย่างยิ่ง

การพัฒนาอย่างยั่งยืน

ผู้ผลิตชิปและซัพพลายเออร์วัสดุกำลังตามหานักเคมีทางเลือกเพื่อลดการปล่อยคาร์บอน ในการแกะสลัก สาเหตุหลักคือก๊าซฟลูออรีนที่มีศักยภาพในการทำให้โลกร้อนสูง

“สาเหตุที่คุณมี PFOS (กรดเปอร์ฟลูออโรออคเทนซัลโฟนิก) ซึ่งเป็นปัญหา เป็นเพราะโมเลกุลมีความเสถียรมาก” เบซาร์ดจาก imec กล่าว “แสงหรือปฏิกิริยาทางเคมีในชั้นบรรยากาศไม่เพียงพอที่จะทำลายมันลงได้”

เขากล่าวว่าส่วนผสมของก๊าซทางเลือกจำนวนหนึ่งที่มีปริมาณออกซิเจนสูงกว่านั้นแยกตัวได้ง่ายกว่าและมี GWP ต่ำกว่า “อย่างไรก็ตาม ผู้สมัครทุกคนจะต้องทำผลงานให้ดีหรือสูงกว่านั้นจึงจะเริ่มต้นได้”

แต่ความยั่งยืนไม่ใช่ความท้าทายในการกัดเซาะหรือการทับถม เป็นความท้าทายของอุตสาหกรรมแบบองค์รวมตั้งแต่การพิมพ์หินไปจนถึงบรรจุภัณฑ์ ซึ่งผลกระทบของวัสดุใหม่จะส่งผลต่อการประมวลผลอุปกรณ์ทั้งหมด

อ้างอิง

1. เค. เดอร์บีเชียร์ “ความแตกต่างของทรานซิสเตอร์ยุคหน้า”, วิศวกรรมเซมิคอนดักเตอร์ 20 ตุลาคม 2022

เรื่องที่เกี่ยวข้อง

Etch คัดเลือกขั้นสูงเปิดตัวสำหรับชิป Next-Gen

การผลิตโครงสร้าง 3 มิติจะต้องมีการควบคุมระดับอะตอมของสิ่งที่ถูกลบออกและสิ่งที่อยู่บนเวเฟอร์

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- เพลโตไอสตรีม. ข้อมูลอัจฉริยะ Web3 ขยายความรู้ เข้าถึงได้ที่นี่.

- การสร้างอนาคตโดย Adryenn Ashley เข้าถึงได้ที่นี่.

- ซื้อและขายหุ้นในบริษัท PRE-IPO ด้วย PREIPO® เข้าถึงได้ที่นี่.

- ที่มา: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- :มี

- :เป็น

- :ไม่

- :ที่ไหน

- $ ขึ้น

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- วัสดุ 2 มิติ

- 30

- 3d

- 50

- a

- ความสามารถ

- สามารถ

- เกี่ยวกับเรา

- เร่งความเร็ว

- เร่ง

- เข้า

- อำนวยความสะดวก

- บรรลุผล

- ตาม

- ถูกต้อง

- แม่นยำ

- ข้าม

- ที่เกิดขึ้นจริง

- ที่อยู่

- การนำมาใช้

- สูง

- ได้เปรียบ

- มีผลต่อ

- อีกครั้ง

- จุดมุ่งหมาย

- อเล็กซ์

- ทั้งหมด

- การอนุญาต

- แล้ว

- ด้วย

- ทางเลือก

- จำนวน

- an

- การวิเคราะห์

- และ

- อื่น

- คำตอบ

- ใด

- ปรากฏ

- การใช้งาน

- เฉพาะแอปพลิเคชัน

- ประยุกต์

- เป็น

- กองทัพบก

- แถว

- AS

- แง่มุม

- ช่วยเหลือ

- At

- บรรยากาศ

- แอตทริบิวต์

- ไป

- Back-end

- ยอดคงเหลือ

- ตาม

- เป็นพื้น

- BE

- คาน

- เพราะ

- สมควร

- รับ

- ก่อน

- การเริ่มต้น

- กำลัง

- ด้านล่าง

- เบนจามิน

- ที่ดีที่สุด

- ดีกว่า

- ระหว่าง

- อคติ

- ใหญ่

- พันล้าน

- บิต

- ทั้งสอง

- ด้านล่าง

- เขตแดน

- ของเล่นเพิ่มพัฒนาสมอง

- ทำลาย

- ไบรอัน

- กำลังดุร้าย

- งบ

- งบประมาณ

- การก่อสร้าง

- สร้าง

- แต่

- by

- ที่เรียกว่า

- CAN

- ผู้สมัคร

- คาร์บอน

- การปล่อยก๊าซคาร์บอน

- ซึ่ง

- กรณี

- กรณี

- CD

- เซลล์

- ท้าทาย

- ท้าทาย

- ห้อง

- เปลี่ยนแปลง

- การเปลี่ยนแปลง

- ช่อง

- ช่อง

- รับผิดชอบ

- การเรียกเก็บเงิน

- โหลด

- การเรียกเก็บเงิน

- สารเคมี

- สารเคมี

- เคมี

- ชิป

- การทำความสะอาด

- ปิดหน้านี้

- อย่างใกล้ชิด

- ใกล้ชิด

- รวม

- บริษัท

- บริษัท

- เข้ากันได้

- สมบูรณ์

- เสร็จ

- ซับซ้อน

- ความซับซ้อน

- คอมพิวเตอร์

- แนวคิด

- เงื่อนไข

- การนำ

- ตัวนำ

- ถือว่า

- คงที่

- รายชื่อผู้ติดต่อ

- เนื้อหา

- ต่อ

- อย่างต่อเนื่อง

- อย่างต่อเนื่อง

- ควบคุม

- ทองแดง

- ไทม์ไลน์การ

- การกร่อน

- ราคา

- ลดต้นทุน

- ค่าใช้จ่าย

- ได้

- หลักสูตร

- สร้าง

- สร้าง

- การสร้าง

- วิกฤติ

- ปัจจุบัน

- ขณะนี้

- ลูกค้า

- ตัด

- ข้อมูล

- การวิเคราะห์ข้อมูล

- วิทยาศาสตร์ข้อมูล

- วัน

- ลึก

- ส่งมอบ

- ขึ้นอยู่กับ

- อธิบาย

- ออกแบบ

- พัฒนา

- ที่กำลังพัฒนา

- พัฒนาการ

- เครื่อง

- อุปกรณ์

- ต่าง

- ยาก

- มิติ

- ทิศทาง

- โดยตรง

- ผู้อำนวยการ

- กล่าวถึง

- การเปลี่ยน

- do

- ทำ

- ดอลลาร์

- ลง

- อย่างมาก

- ขับรถ

- แห้ง

- ในระหว่าง

- แต่ละ

- ก่อน

- อย่างง่ายดาย

- ผล

- ผลกระทบ

- อย่างมีประสิทธิภาพ

- ทั้ง

- ติดตั้งระบบไฟฟ้า

- อิเล็กตรอน

- ปล่อยก๊าซเรือนกระจก

- การเปิดใช้งาน

- วิศวกร

- ชั้นเยี่ยม

- วิศวกร

- พอ

- พอ ๆ กัน

- อุปกรณ์

- พร้อม

- เท่ากัน

- โดยเฉพาะอย่างยิ่ง

- จำเป็น

- เป็นหลัก

- ฯลฯ

- แม้

- ในที่สุด

- ทุกๆ

- เข้มงวด

- วิเคราะห์

- ดำเนินการ

- ที่มีอยู่

- ที่คาดหวัง

- แพง

- การทดลอง

- ความชำนาญ

- ที่เปิดเผย

- การขยาย

- อย่างยิ่ง

- หันหน้าไปทาง

- ไกล

- FAST

- เร็วขึ้น

- คุณสมบัติ

- สองสาม

- สนาม

- รูป

- ฟิล์ม

- ภาพยนตร์

- ชื่อจริง

- แฟลช

- ไหล

- กระแส

- โฟกัส

- ตาม

- ดังต่อไปนี้

- สำหรับ

- บังคับ

- ฟอร์ม

- การสร้าง

- ข้างหน้า

- สี่

- ฟรี

- ราคาเริ่มต้นที่

- อย่างเต็มที่

- ต่อไป

- อนาคต

- ช่องว่าง

- GAS

- General

- สร้าง

- ได้รับ

- กำหนด

- เหตุการณ์ที่

- ภาวะโลกร้อน

- เป้าหมาย

- ดี

- ยิ่งใหญ่

- บัญชีกลุ่ม

- ขึ้น

- เติบโต

- ครึ่ง

- จัดการ

- ยาก

- ฮาร์ดแวร์

- มี

- he

- เป็นประโยชน์

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- จุดสูง

- ให้ผลตอบแทนสูง

- สูงกว่า

- อย่างสูง

- รู

- หลุม

- แบบองค์รวม

- ตามแนวนอน

- บ้าน

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- อย่างไรก็ตาม

- HTTPS

- เป็นมนุษย์

- มนุษย์

- ร้อย

- เป็นลูกผสม

- i

- ส่งผลกระทบ

- เป็นไปไม่ได้

- ปรับปรุง

- การปรับปรุง

- การปรับปรุง

- in

- ประกอบด้วย

- รวมทั้ง

- ขาเข้า

- รวมเข้าด้วยกัน

- ที่เพิ่มขึ้น

- อุตสาหกรรม

- ปัจจัยการผลิต

- ตัวอย่าง

- แทน

- รวบรวม

- การบูรณาการ

- บูรณาการ

- การมีปฏิสัมพันธ์

- ปฏิสัมพันธ์

- การเชื่อมต่อระหว่างกัน

- เข้าไป

- แนะนำ

- ปัญหา

- IT

- ITS

- jpg

- เพียงแค่

- คีย์

- หวด

- ใหญ่

- ที่มีขนาดใหญ่

- ชั้น

- ชั้น

- แบบ

- ชั้นนำ

- การเรียนรู้

- น้อยที่สุด

- ชั้น

- ระดับ

- ชีวิต

- กดไลก์

- น่าจะ

- Line

- เส้น

- ลิธู

- น้อย

- ตรรกะ

- อีกต่อไป

- ดู

- ปิด

- Lot

- ต่ำ

- เครื่อง

- เรียนรู้เครื่อง

- ทำ

- หลัก

- เก็บรักษา

- ทำ

- ผู้ผลิต

- การทำ

- ผู้จัดการ

- ผลิต

- ผู้ผลิต

- การผลิต

- หลาย

- ตลาด

- การตลาด

- Marketing Director

- หน้ากาก

- วัสดุ

- วัสดุ

- ความกว้างสูงสุด

- อาจ..

- หมายความ

- วิธี

- สมาชิก

- หน่วยความจำ

- โลหะ

- โลหะมีค่า

- ตัวชี้วัด

- อาจ

- ล้าน

- ล้าน

- ขั้นต่ำ

- หายไป

- แบบ

- การสร้างแบบจำลอง

- โมเดล

- โหมด

- MOL

- อณู

- เดือน

- ข้อมูลเพิ่มเติม

- มากที่สุด

- ย้าย

- การย้าย

- มาก

- หลาย

- เกือบทั้งหมด

- จำเป็นต้อง

- จำเป็น

- ความต้องการ

- เชิงลบ

- เป็นกลาง

- ใหม่

- ถัดไป

- ไม่

- ชั้นสูง

- ปม

- โหนด

- ตอนนี้

- จำนวน

- ตุลาคม

- of

- มักจะ

- on

- ครั้งเดียว

- ONE

- เพียง

- การดำเนินงาน

- การดำเนินการ

- การเพิ่มประสิทธิภาพ

- เพิ่มประสิทธิภาพ

- การปรับให้เหมาะสม

- or

- ใบสั่ง

- อื่นๆ

- ผลิตภัณฑ์อื่นๆ

- ของเรา

- ออก

- เกิน

- ออกซิเจน

- บรรจุภัณฑ์

- พารามิเตอร์

- ในสิ่งที่สนใจ

- โดยเฉพาะ

- แบบแผน

- คน

- ดำเนินการ

- การปฏิบัติ

- ที่มีประสิทธิภาพ

- บางที

- มุมมอง

- ระยะ

- ปรากฏการณ์

- ฟิลิปป์

- กายภาพ

- ทางร่างกาย

- ฟิสิกส์

- เสา

- ขว้าง

- เป็นจุดสำคัญ

- พลาสมา

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- เล่น

- PoC

- บวก

- ความเป็นไปได้

- เป็นไปได้

- อาจ

- ที่มีศักยภาพ

- ที่อาจเกิดขึ้น

- อำนาจ

- ที่มีประสิทธิภาพ

- จำเป็นต้อง

- ความแม่นยำ

- คาดการณ์

- ประธาน

- ความดัน

- ปัญหา

- ปัญหาที่เกิดขึ้น

- กระบวนการ

- กระบวนการ

- การประมวลผล

- ก่อ

- ผลิตภัณฑ์

- การพัฒนาผลิตภัณฑ์

- การผลิต

- ผลผลิต

- ผลิตภัณฑ์

- โปรไฟล์

- ดูรายละเอียด

- ทำกำไรได้

- โครงการ

- การเขียนโปรแกรม

- แวว

- พิสูจน์

- พิสูจน์แนวคิด

- สิ่งพิมพ์

- ผลัก

- คำถาม

- อย่างรวดเร็ว

- วิจัยและพัฒนา

- ทางลาด

- พิสัย

- คะแนน

- ราคา

- อัตราส่วน

- มาถึง

- เกิดปฏิกิริยา

- ปฏิกิริยา

- ปฏิกิริยา

- จริง

- ชีวิตจริง

- เหตุผล

- เมื่อเร็ว ๆ นี้

- แนะนำ

- แนะนำ

- ลด

- ลด

- การลดลง

- สะท้อน

- ปกติ

- ปล่อย

- น่าเชื่อถือ

- วางใจ

- การกำจัด

- เอาออก

- ลบออก

- ลบ

- ทำซ้ำได้

- ซ้ำแล้วซ้ำอีก

- แทนที่

- รายงาน

- ต้องการ

- จำเป็นต้องใช้

- ความต้องการ

- ต้อง

- การวิจัย

- ผล

- ผลสอบ

- เผย

- ขวา

- โรเบิร์ต

- บทบาท

- ม้วน

- ลวก

- กฎระเบียบ

- วิ่ง

- กล่าวว่า

- เดียวกัน

- กล่าว

- ขนาด

- ปรับ

- รูปแบบ

- วิทยาศาสตร์

- แสวงหา

- เห็น

- เลือก

- สารกึ่งตัวนำ

- ระดับอาวุโส

- ความรู้สึก

- การตั้งค่า

- หลาย

- เปลี่ยน

- น่า

- ซิลิคอน

- ง่าย

- ลดความซับซ้อน

- ง่ายดาย

- จำลอง

- เดียว

- มีฝีมือ

- เล็ก

- So

- ซอฟต์แวร์

- โซลูชัน

- แก้

- บาง

- บางแห่ง

- แหล่ง

- ช่องว่าง

- โดยเฉพาะ

- ข้อกำหนด

- รายละเอียด

- ความเร็ว

- Stability

- มั่นคง

- ซ้อนกัน

- สแต็ค

- ทักษะ

- ขั้นตอน

- เริ่มต้น

- ข้อความที่เริ่ม

- ขั้นตอน

- ขั้นตอน

- ยังคง

- ความเครียด

- โครงสร้าง

- ต่อจากนั้น

- เป็นกอบเป็นกำ

- อย่างเช่น

- ฉับพลัน

- เพียงพอ

- ชี้ให้เห็นถึง

- ซัพพลายเออร์

- พื้นผิว

- แปลกใจ

- การพัฒนาอย่างยั่งยืน

- ที่ยั่งยืน

- กวาด

- สวิสเซอร์แลนด์

- ระบบ

- เอา

- การ

- คุย

- เป้าหมาย

- ทีม

- วิชาการ

- เทคโนโลยี

- เทคโนโลยี

- การพัฒนาเทคโนโลยี

- ระยะ

- ทดสอบ

- การทดสอบ

- การทดสอบ

- กว่า

- ที่

- พื้นที่

- ก้าวสู่อนาคต

- ของพวกเขา

- พวกเขา

- แล้วก็

- ที่นั่น

- ร้อน

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- พวกเขา

- สิ่ง

- ที่สาม

- นี้

- อย่างถี่ถ้วน

- พัน

- สาม

- ตลอด

- ชั้น

- ที่เข้มงวดมากขึ้น

- เวลา

- ระยะเวลา

- ไปยัง

- ร่วมกัน

- ต้น

- TONE

- เกินไป

- ด้านบน

- แตะ

- ไปทาง

- โอน

- แปลง

- การเปลี่ยนแปลง

- เทรนด์

- ลอง

- สอง

- ตามแบบฉบับ

- เป็นปกติ

- พื้นฐาน

- ทายไม่ถูก

- เมื่อ

- สูงกว่า

- us

- ใช้

- มือสอง

- ผู้ใช้งาน

- การใช้

- นำไปใช้

- การตรวจสอบแล้ว

- แนวตั้ง

- ดิ่ง

- มาก

- ผ่านทาง

- ทำงานได้

- Vice President

- vincent

- เสมือน

- ระเหย

- ต้องการ

- ต้องการ

- คือ

- ทาง..

- we

- สัปดาห์ที่ผ่านมา

- ดี

- อะไร

- เมื่อ

- ว่า

- ที่

- ในขณะที่

- ทั้งหมด

- ทำไม

- จะ

- กับ

- ภายใน

- ไม่มี

- คำ

- งาน

- การทำงาน

- โรงงาน

- จะ

- ปี

- ปี

- ผล

- ยอมให้

- อัตราผลตอบแทน

- เธอ

- ลมทะเล

- เป็นศูนย์