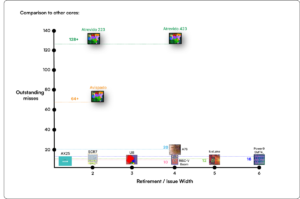

Chiplets ได้ทำให้การออกแบบด้านหนึ่งเรียบง่ายขึ้น แต่กลับเปิดกล่องแพนโดร่าไว้ที่ด้านหน้าอีกด้าน ความซับซ้อนในการจำลองของแต่ละอย่าง ชิปเล็ต ต่ำกว่า แต่ตอนนี้การเชื่อมต่อระหว่างชิปเล็ตกับชิปเล็ตมีความซับซ้อน ผู้คนกำลังทดลองใช้โปรโตคอลการเชื่อมต่อระหว่างกัน รูปแบบของ UCIe การปรับเปลี่ยนการตั้งค่า UCIe ความเร็วอินเทอร์เฟซ จำนวนเลเยอร์ทางกายภาพ และอื่นๆ ตอนนี้เพิ่มมาตรฐานเดิม เช่น AXI, โปรโตคอลใหม่ เช่น PICe6.0 และการเชื่อมโยงกันของแคชเข้าด้วยกัน

โดยรวมแล้ว สิ่งนี้ทำให้เกิดการทดลองชุดใหม่ทั้งหมด สิ่งหนึ่งที่การจำลองแบบดั้งเดิมและการสร้างแบบจำลอง RTL จะไม่ทำงาน คุณต้องใช้ความพยายามในการแลกเปลี่ยนทางสถาปัตยกรรมก่อน ไม่ใช่แค่การเลือกส่วนประกอบเท่านั้น ซึ่งหมายความว่าคุณจะต้องดำเนินการวิเคราะห์การรับส่งข้อมูล การแบ่งพาร์ติชันแอปพลิเคชัน ขนาดของระบบ และผลกระทบของเลเยอร์ทางกายภาพประเภทต่างๆ นอกจากนี้เกณฑ์มาตรฐานจะแตกต่างกันมากขึ้นอยู่กับแอปพลิเคชัน

ข้อกำหนด UCIe เป็นข้อกำหนดใหม่และไม่มีเกณฑ์มาตรฐานที่ชัดเจน นอกจากนี้ ข้อกำหนด UCIe ยังให้คำแนะนำเกี่ยวกับเวลาแฝงและพลังงานเท่านั้น ทั้งสองเป็นข้อกำหนดที่เข้มงวด ซึ่งหมายความว่าการศึกษาด้านกำลัง-ประสิทธิภาพ-พื้นที่เป็นสิ่งที่หลีกเลี่ยงไม่ได้ เนื่องจากคุณมีการแปลงโปรโตคอล-โปรโตคอล-โปรโตคอล เช่น PCIe 6.0 เป็น UCIe เป็น AXI การตั้งค่าการสร้างแบบจำลองจึงซับซ้อน

ทางออกหนึ่งคือการดูการสร้างแบบจำลองระบบโดยใช้ วิชวลซิม ราคาเริ่มต้นที่ มิราบิลิส ออกแบบ. พวกเขาเพิ่งเปิดตัวโมเดล IP ระดับระบบ UCIe และจะสาธิตกรณีการใช้งานต่างๆ ของการเชื่อมต่อระหว่างกันที่ การประชุมสุดยอด Chiplet. เพื่อเป็นแนวทางแก่นักออกแบบ พวกเขาได้เผยแพร่คู่มือพร้อมกรณีการใช้งานจำนวนมาก ผลลัพธ์ประสิทธิภาพพลังงานที่คาดหวัง และตัวเลือกสำหรับการเพิ่มประสิทธิภาพ พวกเขามีทั้งการนำเสนอกระดาษและบูธในการประชุมสุดยอด ฉันหวังว่าจะได้พบคุณที่นั่น!

นี่คือลิงค์สำหรับบทความที่ผู้คนสามารถรับได้: การสร้างแบบจำลองประสิทธิภาพของระบบคอมพิวเตอร์ที่แตกต่างกันตามสถาปัตยกรรม UCIe Interconnect

นามธรรม:

การออกแบบชิปที่ซับซ้อนในปัจจุบันที่โหนดระดับแนวหน้าโดยทั่วไปประกอบด้วยแม่พิมพ์หลายตัว (หรือชิปเล็ต) แนวทางดังกล่าวช่วยให้สามารถผลิตแม่พิมพ์จากผู้ผลิตหรือกระบวนการต่างๆ ได้ เช่นเดียวกับ IP ที่นำมาใช้ซ้ำได้ นักออกแบบจำเป็นต้องมีแบบจำลองระดับระบบเพื่อประเมินการใช้งานที่แตกต่างกันของสถานการณ์ที่ซับซ้อนดังกล่าว

ระบบตัวอย่างประกอบด้วยชิปเล็ต I/O, ชิปเล็ตคอร์พลังงานต่ำ, ชิปเล็ตคอร์ประสิทธิภาพสูง, ชิปเล็ตเสียงและวิดีโอ และชิปเล็ตแอนะล็อก ที่เชื่อมต่อถึงกันโดยใช้มาตรฐาน Universal Chiplet Interconnect Express (UCIe)

ทีมของเราพิจารณาสถานการณ์และการกำหนดค่าหลายประการ รวมถึงแพ็คเกจขั้นสูงและมาตรฐาน โปรไฟล์การรับส่งข้อมูลและทรัพยากรที่หลากหลาย และตัวจับเวลาเพื่อขยายขอบเขตการเข้าถึงและประเมินเหตุการณ์เมื่อหมดเวลา การระบุจุดแข็งและจุดอ่อนของการเชื่อมต่อ UCIe สำหรับการใช้งานภารกิจช่วยให้เราได้รับการกำหนดค่าที่เหมาะสมที่สุดสำหรับแต่ละระบบย่อยเพื่อให้ตรงตามข้อกำหนดด้านประสิทธิภาพ กำลัง และฟังก์ชัน

เกี่ยวกับมิราบิลิส ดีไซน์ อิงค์

Mirabilis Design เป็นบริษัทซอฟต์แวร์ใน Silicon Valley ที่ให้บริการซอฟต์แวร์และโซลูชันการฝึกอบรมเพื่อระบุและขจัดความเสี่ยงในข้อมูลจำเพาะของผลิตภัณฑ์ คาดการณ์ทรัพยากรบุคคลและเวลาที่จำเป็นในการพัฒนาผลิตภัณฑ์ได้อย่างแม่นยำ และปรับปรุงการสื่อสารระหว่างวิศวกรรมที่หลากหลาย

ทีม

VisualSim Architect ผสมผสานทรัพย์สินทางปัญญา การสร้างแบบจำลองระดับระบบ การจำลอง การวิเคราะห์สภาพแวดล้อม และเทมเพลตแอปพลิเคชัน เพื่อปรับปรุงการสร้างแบบจำลอง การจำลอง การวิเคราะห์ และการตรวจสอบ RTL อย่างมีนัยสำคัญ สภาพแวดล้อมช่วยให้นักออกแบบสามารถรวมเข้ากับการออกแบบได้อย่างรวดเร็ว ซึ่งตรงตามข้อกำหนดด้านเวลาและพลังงานที่พึ่งพาซึ่งกันและกัน ใช้ตั้งแต่เนิ่นๆ ในกระบวนการออกแบบควบคู่ไปกับ (และเป็นตัวช่วย) ข้อกำหนดที่เป็นลายลักษณ์อักษรและก่อนการใช้งาน (เช่น RTL, รหัสซอฟต์แวร์ หรือแผนผัง) ของผลิตภัณฑ์

ยังอ่าน:

การสัมมนาออนไลน์: วิธีบรรลุการวัดพลังงานที่แม่นยำ 95%+ ในระหว่างการสำรวจสถาปัตยกรรม

การแมป SysML กับสถาปัตยกรรมฮาร์ดแวร์

หลักสูตรการออกแบบตามแบบจำลองสำหรับนักศึกษา

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- PlatoData.Network Vertical Generative Ai เพิ่มพลังให้กับตัวเอง เข้าถึงได้ที่นี่.

- เพลโตไอสตรีม. Web3 อัจฉริยะ ขยายความรู้ เข้าถึงได้ที่นี่.

- เพลโตESG. คาร์บอน, คลีนเทค, พลังงาน, สิ่งแวดล้อม แสงอาทิตย์, การจัดการของเสีย. เข้าถึงได้ที่นี่.

- เพลโตสุขภาพ เทคโนโลยีชีวภาพและข่าวกรองการทดลองทางคลินิก เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- :มี

- :เป็น

- :ไม่

- a

- ถูกต้อง

- แม่นยำ

- บรรลุ

- เพิ่ม

- สูง

- ช่วย

- ช่วยให้

- ตาม

- ด้วย

- an

- การวิเคราะห์

- และ

- อื่น

- การใช้งาน

- การใช้งาน

- เข้าใกล้

- สถาปัตยกรรม

- เป็น

- AREA

- AS

- At

- ตาม

- BE

- กลายเป็น

- ก่อน

- มาตรฐาน

- มาตรฐาน

- ระหว่าง

- ทั้งสอง

- กล่อง

- แต่

- แคช

- CAN

- สามารถรับ

- กรณี

- ชิป

- ชัดเจน

- รหัส

- รวม

- การสื่อสาร

- บริษัท

- อย่างสมบูรณ์

- ซับซ้อน

- ความซับซ้อน

- ส่วนประกอบ

- การคำนวณ

- ความประพฤติ

- องค์ประกอบ

- ถือว่า

- ประกอบ

- การก่อสร้าง

- ลู่

- การแปลง

- แกน

- หลักสูตร

- สร้าง

- แสดงให้เห็นถึง

- ทั้งนี้ขึ้นอยู่กับ

- ออกแบบ

- กระบวนการออกแบบ

- นักออกแบบ

- การออกแบบ

- พัฒนา

- ต่าง

- หลาย

- ในระหว่าง

- แต่ละ

- ก่อน

- ความพยายาม

- กำจัด

- การแข่งขัน

- ช่วยให้

- สิ่งแวดล้อม

- ประเมินค่า

- เหตุการณ์

- ตัวอย่าง

- ที่คาดหวัง

- ทดลอง

- การทดลอง

- ด่วน

- ขยายออก

- ชื่อจริง

- สำหรับ

- ราคาเริ่มต้นที่

- ด้านหน้า

- การทำงาน

- โดยทั่วไป

- ได้รับ

- คำแนะนำ

- ให้คำแนะนำ

- ฮาร์ดแวร์

- มี

- ช่วย

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- ประสิทธิภาพสูง

- ความหวัง

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- ทำอย่างไร

- HTTPS

- เป็นมนุษย์

- i

- แยกแยะ

- ระบุ

- ส่งผลกระทบ

- การดำเนินงาน

- การใช้งาน

- ปรับปรุง

- in

- รวมทั้ง

- ทางปัญญา

- ทรัพย์สินทางปัญญา

- เชื่อมต่อถึงกัน

- อินเตอร์เฟซ

- IP

- IT

- jpg

- เพียงแค่

- ความแอบแฝง

- เปิดตัว

- ชั้น

- ชั้น

- มรดก

- ชั้น

- กดไลก์

- LINK

- ดู

- จำนวนมาก

- ต่ำ

- ลด

- ผู้ผลิตยา

- ความกว้างสูงสุด

- หมายความ

- วิธี

- การวัด

- พบ

- มีคุณสมบัติตรงตาม

- ภารกิจ

- ผสม

- แบบ

- การสร้างแบบจำลอง

- การสร้างแบบจำลอง

- หลาย

- จำเป็นต้อง

- ใหม่

- ไม่

- โหนด

- ตอนนี้

- จำนวน

- ได้รับ

- of

- on

- ONE

- เพียง

- เปิด

- เปิด

- ดีที่สุด

- การเพิ่มประสิทธิภาพ

- Options

- or

- แพคเกจ

- กระดาษ

- Parallel

- การปฏิบัติ

- กายภาพ

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- โพสต์

- อำนาจ

- ทำนาย

- การเสนอ

- กระบวนการ

- กระบวนการ

- ผลิตภัณฑ์

- ดูรายละเอียด

- คุณสมบัติ

- โปรโตคอล

- ให้

- การให้

- การตีพิมพ์

- อย่างรวดเร็ว

- มาถึง

- อ่าน

- เมื่อเร็ว ๆ นี้

- จำเป็นต้องใช้

- ความต้องการ

- แหล่งข้อมูล

- ผลสอบ

- นำมาใช้ใหม่

- ความเสี่ยง

- สถานการณ์

- เห็น

- การเลือก

- ชุด

- การตั้งค่า

- การติดตั้ง

- หลาย

- อย่างมีความหมาย

- ซิลิคอน

- หุบเขาซิลิคอน

- ที่เรียบง่าย

- จำลอง

- สถานการณ์

- So

- ซอฟต์แวร์

- ทางออก

- โซลูชัน

- สเปค

- ความเร็ว

- ใช้จ่าย

- มาตรฐาน

- มาตรฐาน

- จุดแข็ง

- เข้มงวด

- ศึกษา

- อย่างเช่น

- ประชุมสุดยอด

- ระบบ

- ทีม

- แม่แบบ

- ที่

- พื้นที่

- ที่นั่น

- พวกเขา

- นี้

- เวลา

- ไปยัง

- แบบดั้งเดิม

- การจราจร

- การฝึกอบรม

- ชนิด

- สากล

- us

- ใช้

- มือสอง

- การใช้

- หุบเขา

- รูปแบบ

- การตรวจสอบ

- มาก

- ผ่านทาง

- ความอ่อนแอ

- ดี

- ที่

- จะ

- กับ

- งาน

- เขียน

- เธอ

- ลมทะเล