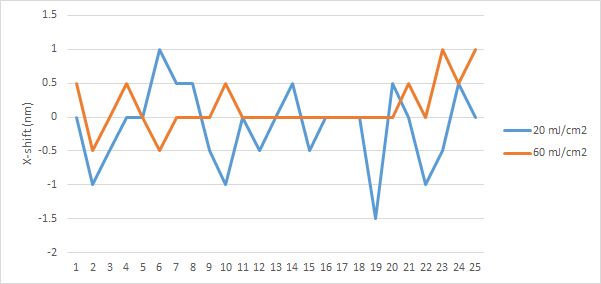

การแสวงหาขนาดเซลล์ DRAM ที่เล็กลงยังคงดำเนินอยู่และดำเนินต่อไป ขนาดเซลล์ DRAM คาดว่าจะเข้าใกล้ 0.0013 um2 สำหรับโหนด D12 ความท้าทายในการสร้างลวดลายมีความสำคัญไม่ว่าจะพิจารณาถึงการใช้การพิมพ์หิน DUV หรือ EUV โดยเฉพาะอย่างยิ่ง ASML รายงานว่าเมื่อค่าจากศูนย์กลางถึงศูนย์กลางถึง 40 นาโนเมตร จะไม่แนะนำให้ใช้รูปแบบเดียวแม้แต่กับ EUV [1] ในบทความนี้ เราจะแสดงให้เห็นว่าสำหรับโหนด DRAM ขนาด 12 นาโนเมตรและหลังจากนั้น ตัวเก็บประจุจากศูนย์กลางถึงศูนย์กลางคาดว่าจะต่ำกว่า 40 นาโนเมตร ดังนั้นจึงต้องใช้รูปแบบหลายลวดลาย

รูปแบบเซลล์ DRAM สำหรับตัวเก็บประจุ

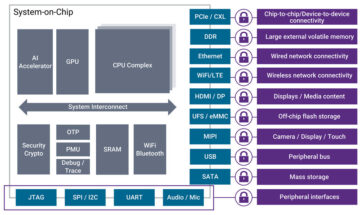

ตัวเก็บประจุจัดเก็บถูกจัดเรียงเป็นอาร์เรย์หกเหลี่ยม (รูปที่ 1) กฎการออกแบบพื้นที่แอ็คทีฟถูกกำหนดโดยระดับบิตไลน์และระดับเวิร์ดไลน์ [2]

รูปที่ 1. โหนดหน่วยเก็บข้อมูล (สีเหลือง) บนตารางเซลล์ DRAM BLP = ระดับเสียงของเส้นบิต, WLP = ระดับเสียงของคำ

ระยะพิทช์ของเส้นบิต 38 นาโนเมตรและระยะพิทช์ของเส้นคำ 33 นาโนเมตรจะนำไปสู่จุดกึ่งกลางถึงกึ่งกลางที่ 38 นาโนเมตรและระยะพิทช์ 32.9 นาโนเมตรระหว่างเส้นทแยงมุม สำหรับขนาดเซลล์ 0.001254 um2 และต่ำกว่ากฎการออกแบบพื้นที่แอ็คทีฟ 12 นาโนเมตร

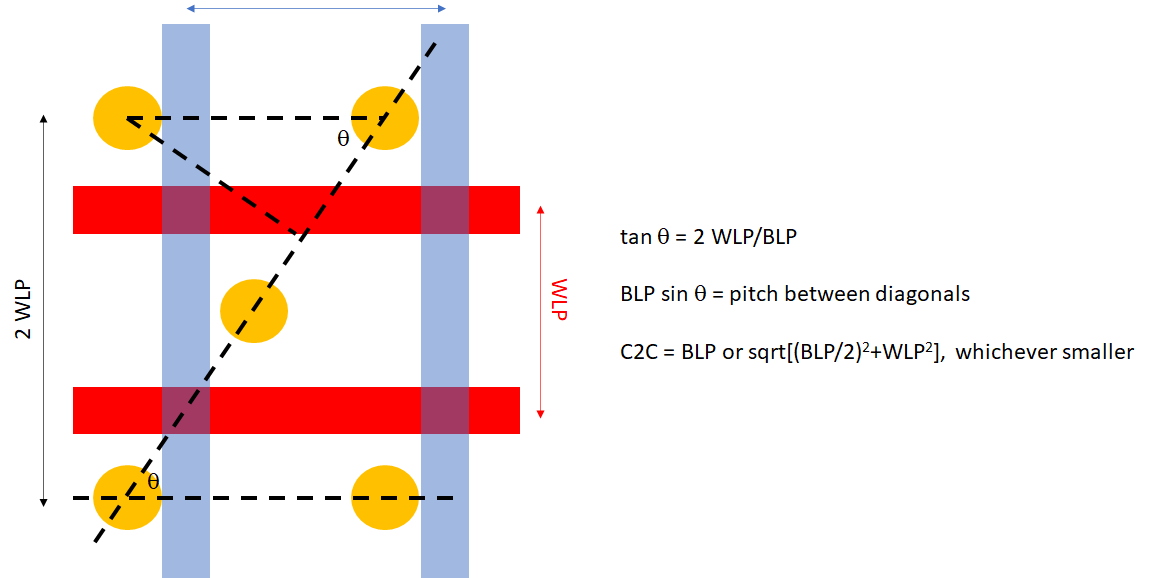

สำหรับระบบ 0.33 NA EUV อาร์เรย์หกเหลี่ยมจะใช้การส่องสว่างแบบหกเหลี่ยม โดยที่แต่ละขั้วจะสร้างรูปแบบการรบกวนแบบสามลำแสง (รูปที่ 2) เสาสี่แฉกสร้างรูปแบบที่แตกต่างจากเสาแนวนอนอีกสองเสา สิ่งนี้นำไปสู่ส่วนประกอบของขนาดยาที่แยกจากกันโดยมีสโทแคสติกแยกกัน สิ่งเหล่านี้ถูกเพิ่มเข้ามาในรูปแบบผสมขั้นสุดท้าย

รูปที่ 2 ไฟส่องสว่างแบบ Hexapole สำหรับรูปแบบการจัดเก็บข้อมูล DRAM ประกอบด้วย 4 ขั้ว (สีเทา) และ XNUMX ขั้วในแนวนอน (สีเหลือง) รูปแบบการแทรกสอดของลำแสงสามลำที่ได้จะมีทิศทางเฉพาะ ทั้งนี้ขึ้นอยู่กับทิศทางการส่องสว่าง

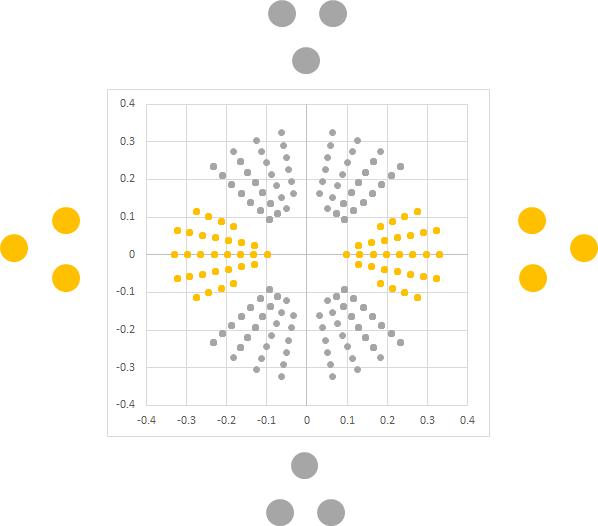

เนื่องจากสัญญาณรบกวนจากการยิงโฟตอนที่ถูกดูดกลืนอย่างมากที่ขอบของคุณลักษณะ ผลกระทบแบบสุ่มต่อข้อผิดพลาดในการจัดวางรูปแบบจึงมีความสำคัญ ดังที่ได้เปิดเผยไว้แล้วในการอ้างอิง 1 เกินสเป็คโอเวอร์เลย์ 1 นาโนเมตรอย่างง่ายดาย ปริมาณการดูดซึมที่ต่ำกว่าดูเหมือนจะแย่ลงอย่างเห็นได้ชัด (รูปที่ 3)

รูปที่ 3 ข้อผิดพลาดในการจัดวางสุ่ม (เฉพาะ X) ของเสากลางในเซลล์หน่วยขนาด 38 นาโนเมตร x 66 นาโนเมตร (ระยะห่างของเส้นคำ = 33 นาโนเมตร) โดยคาดว่าจะมีการส่องสว่างแบบหกเหลี่ยมในระบบ 0.33 NA EUV ในที่นี้มีการแสดงตัวอย่างที่แตกต่างกัน 25 รายการสำหรับปริมาณที่ดูดซึมสองครั้ง

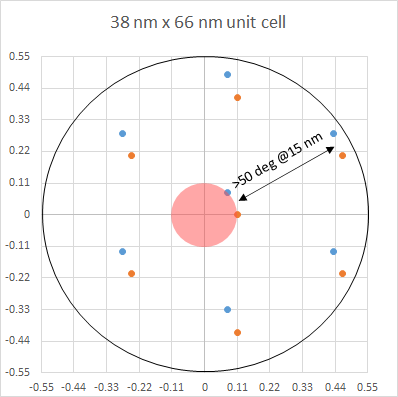

ไปที่ 0.55 NA เพิ่มปัญหาของความลึกของโฟกัสที่ลดลงอย่างมาก ค่า NA 0.55 จะส่งผลให้เกิดการเบลอ 15 นาโนเมตร ซึ่งนำไปสู่การเปลี่ยนเฟส >50 องศาระหว่างคำสั่งการเลี้ยวเบนด้านในสุดและด้านนอกสุด (รูปที่ 4) ซึ่งทำให้คอนทราสต์ของภาพลดลงอย่างมากเนื่องจากการซีดจาง [3]

รูปที่ 4 ระยะพร่ามัว 15 นาโนเมตรบนระบบ 0.55 NA EUV ทำให้เกิดการเลื่อนเฟส >50 องศาระหว่างคำสั่งการเลี้ยวเบนด้านในสุดและด้านนอกสุด

ดังนั้นจึงเป็นไปได้ว่ารูปแบบโหนดหน่วยเก็บข้อมูลจำเป็นต้องเกิดขึ้นจากรูปแบบเส้นสองเส้นที่ตัดกัน (รูปที่ 5) รูปแบบเส้นที่ตัดกันแต่ละรูปแบบสามารถเกิดขึ้นได้จากการเปิดรับแสงครั้งเดียวของ EUV หรือโดย DUV SAQP (การสร้างรูปแบบสี่เท่าในแนวเดียวกัน) ตัวเลือกทั้งสองเป็นกระบวนการมาสก์เดียว กระบวนการ SAQP นั้นสมบูรณ์กว่า (มี EUV นำหน้ามานาน) และปราศจากความกังวลสุ่มอิเล็กตรอนทุติยภูมิของ EUV [4] ดังนั้นจึงควรเป็นที่ต้องการ อย่างไรก็ตาม สำหรับกรณี SAQP เส้นสเปเซอร์จะต้องมีการควบคุมอย่างดีทั้งในแง่ของตำแหน่งและความขรุขระของเส้น [5]

รูปที่ 5 รูปแบบโหนดหน่วยเก็บข้อมูลสามารถเกิดขึ้นได้จากจุดตัดของรูปแบบเส้นสองเส้นที่ตัดกัน

แทนที่จะใช้ SAQP แบบเส้น ซัมซุงยังแสดงรูปแบบรังผึ้งสเปเซอร์แบบ 2 มิติ [6] โดยใช้มาสก์เดียวที่มีรูปแบบรังผึ้งเริ่มต้น แทนที่จะใช้มาสก์สองตัวที่มีรูปแบบเส้นเริ่มต้น

ในขณะที่กรณีข้างต้นพิจารณาระยะพิตช์บรรทัดบิต 38 นาโนเมตรและพิตช์บรรทัดคำ 33 นาโนเมตร มันก็ใช้กับกรณีที่สลับพิตช์ (พิตช์บรรทัดบิต 33 นาโนเมตรและพิตช์บรรทัดคำ 38 นาโนเมตร) เนื่องจากสมมาตรหกเหลี่ยม

อ้างอิง

[1] W. Gao et al., Proc. SPIE 11323, 113231L (2020)

[2] F. Chen, ความสัมพันธ์ตรีโกณมิติระหว่าง DRAM Cell Pitches, https://www.youtube.com/watch?v=Oq6b-6iw6Zk

[3] จฮ. Franke, TA Brunner, E. Hendrickx, J. Micro/Nanopattern แม่ เมโทรล. 21, 030501 (2022).

[4] F. Chen, ความสุ่มของอิเล็กตรอนเบลอทุติยภูมิเป็นต้นกำเนิดของ EUV Stochastic Defects, https://www.linkedin.com/pulse/secondary-electron-blur-randomness-origin-euv-stochastic-chen/

[5] N. Bae et al., Proc. SPIE 11615, 116150B (2021)

[6] JM Park et al., IEDM 2015.

บทความนี้ปรากฏครั้งแรกใน LinkedIn Pulse: การพิมพ์หินเฉพาะแอปพลิเคชัน: Sub-0.0013 um2 DRAM Storage Node Patterning

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- เพลโตบล็อคเชน Web3 Metaverse ข่าวกรอง ขยายความรู้. เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/lithography/323357-application-specific-lithography-sub-0-0013-um2-dram-storage-node-patterning/

- 1

- 2020

- 2021

- 2022

- 9

- a

- ข้างบน

- คล่องแคล่ว

- ที่เพิ่ม

- เพิ่ม

- แล้ว

- ในหมู่

- และ

- ปรากฏ

- การใช้งาน

- เฉพาะแอปพลิเคชัน

- เข้าใกล้

- AREA

- จัด

- แถว

- บทความ

- ด้านล่าง

- ระหว่าง

- เกิน

- บิต

- เบลอ

- กรณี

- ส่วนกลาง

- ความท้าทาย

- เฉิน

- ส่วนประกอบ

- ความกังวลเกี่ยวกับ

- ถือว่า

- พิจารณา

- ตรงกันข้าม

- ข้าม

- แสดงให้เห็นถึง

- ทั้งนี้ขึ้นอยู่กับ

- ความลึก

- ออกแบบ

- แน่นอน

- ต่าง

- ทิศทาง

- แต่ละ

- อย่างง่ายดาย

- ขอบ

- ผล

- ความผิดพลาด

- แม้

- เคย

- ที่คาดหวัง

- การเปิดรับ

- ลักษณะ

- รูป

- สุดท้าย

- ชื่อจริง

- โฟกัส

- ที่เกิดขึ้น

- ฟรี

- ราคาเริ่มต้นที่

- GAO

- Go

- ตะแกรง

- มี

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- ตามแนวนอน

- HTTPS

- ภาพ

- in

- แทน

- การตัด

- ปัญหา

- IT

- แบบ

- นำ

- ชั้นนำ

- นำไปสู่

- น่าจะ

- Line

- เส้น

- นาน

- หน้ากาก

- มาสก์

- เป็นผู้ใหญ่

- ความกว้างสูงสุด

- ข้อมูลเพิ่มเติม

- ความต้องการ

- ปม

- โหนด

- สัญญาณรบกวน

- ต่อเนื่อง

- Options

- คำสั่งซื้อ

- ที่มา

- อื่นๆ

- สวนสาธารณะ

- ในสิ่งที่สนใจ

- แบบแผน

- รูปแบบ

- ระยะ

- เสา

- ขว้าง

- โหมโรง

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- โพสต์

- ที่ต้องการ

- PROC

- กระบวนการ

- กระบวนการ

- ก่อ

- ที่คาดการณ์

- ชีพจร

- สุ่ม

- ถึง

- แนะนำ

- ลดลง

- ลด

- ความสัมพันธ์

- รายงาน

- ผล

- ส่งผลให้

- กฎ

- ซัมซุง

- รอง

- ชุด

- เปลี่ยน

- น่า

- โชว์

- แสดง

- สำคัญ

- เดียว

- ขนาด

- ขนาด

- มีขนาดเล็กกว่า

- So

- โดยเฉพาะ

- ที่เริ่มต้น

- ยังคง

- การเก็บรักษา

- เป็นกอบเป็นกำ

- ระบบ

- เงื่อนไขการใช้บริการ

- พื้นที่

- ดังนั้น

- ไปยัง

- ภายใต้

- หน่วย

- ใช้

- การใช้ประโยชน์

- ความคุ้มค่า

- ผ่านทาง

- W

- ว่า

- ที่

- จะ

- คำ

- จะ

- X

- YouTube

- ลมทะเล