ในศัพท์เฉพาะของวงจรรวม การลดหย่อนคือแรงดันตกคร่อมที่เกิดขึ้นในวงจร นี่เป็นปรากฏการณ์ที่รู้จักกันดีและอาจเกิดขึ้นได้จากสาเหตุดังต่อไปนี้ แหล่งจ่ายไฟอยู่ต่ำกว่าช่วงการทำงานที่ชิปได้รับการออกแบบมา ส่งผลให้ไฟตก กระแสไฟฟ้าถูกดึงโดยองค์ประกอบที่เป็นสื่อกระแสไฟฟ้ามากกว่าที่ได้รับการออกแบบไว้ ส่งผลให้เกิดการตกต่ำ บางครั้งสัญญาณรบกวนหรือสัญญาณรบกวนบนแหล่งจ่ายไฟอาจทำให้เกิดความผันผวนของแรงดันไฟฟ้า ส่งผลให้เกิดการตกต่ำ

การตกหล่นสามารถส่งผลกระทบต่อการทำงานของวงจรได้ ประสิทธิภาพที่ลดลงของชิป ส่งผลให้ใช้เวลาในการประมวลผลนานขึ้นคือผลกระทบอย่างหนึ่ง แต่ต่อไปนี้คือผลกระทบที่ร้ายแรงและ/หรือเป็นหายนะบางส่วน ชิปสามารถดึงกระแสไฟได้มากขึ้นเพื่อรักษาระดับประสิทธิภาพซึ่งนำไปสู่การใช้พลังงานและการกระจายความร้อนที่เพิ่มขึ้น สิ่งนี้สามารถนำไปสู่อายุการใช้งานของชิปที่ลดลง และในกรณีที่รุนแรง อาจทำให้ชิปเสียหายโดยสิ้นเชิงเนื่องจากการตั้งค่าและการยึดรูปแบบต่างๆ การตกหล่นอาจทำให้ข้อมูลเสียหายหรือเกิดข้อผิดพลาดในเอาต์พุตได้ นี่เป็นปัญหาร้ายแรงมากสำหรับการใช้งานที่ต้องอาศัยความแม่นยำและความน่าเชื่อถือของชิป

โดยปกติแล้ว ปรากฏการณ์การตกหล่นจะถูกนำมาพิจารณาอย่างจริงจังเมื่อออกแบบชิปและระบบ วิธีการทั่วไปในการบรรเทาปัญหาไฟตก ได้แก่ การแยกแหล่งจ่ายไฟ การควบคุมแรงดันไฟฟ้า การปรับวงจรให้เหมาะสม และการจัดการพลังงานระดับระบบ เงื่อนไขและสภาพแวดล้อมการทำงานที่ชิปจะทำงานจะได้รับการพิจารณาอย่างรอบคอบเมื่อออกแบบโซลูชันลดการตกหล่น

ปัญหาในยุคปัจจุบัน

เมื่อ SoC มีความซับซ้อนมากขึ้น ปัญหาการตกต่ำก็อาจซับซ้อนได้เช่นกัน การออกแบบของ SoC จำเป็นต้องได้รับการปรับให้เหมาะสมทั้งด้านประสิทธิภาพ พลังงาน ต้นทุน ฟอร์มแฟคเตอร์ ฯลฯ นอกเหนือจากการปรับให้เหมาะสมเพื่อบรรเทาปัญหาการตกต่ำ บางครั้งเป้าหมายการปรับให้เหมาะสมเหล่านี้สามารถแข่งขันกันเองและต้องตอบโต้และต้องแลกกัน ตัวอย่างเช่น สถาปนิก SoC สามารถเพิ่มแรงดันไฟฟ้าในการดำเนินงาน โดยเพิ่มส่วนต่าง เพื่อหลีกเลี่ยงปัญหาการตกต่ำทั้งในระดับท้องถิ่นและระดับโลก แต่การเพิ่มขึ้นนี้จะเพิ่มกำลังเป็นกำลังสอง อีกทางหนึ่ง นักออกแบบสามารถให้การสร้างนาฬิกาของตนปรับให้เข้ากับการตกต่ำ ซึ่งทำให้ประสิทธิภาพการทำงานเป็นหน้าที่ของเวลาในการสลับการสร้างนาฬิกา

ด้วยเหตุนี้ SoC ขนาดใหญ่ในการประมวลผลของศูนย์ข้อมูลและพื้นที่ AI จึงมีแนวโน้มที่จะลดลงอย่างเห็นได้ชัด ปริมาณงานของลูกค้ามีความหลากหลายและเปลี่ยนแปลงตลอดเวลา ซึ่งนำไปสู่ความผันผวนอย่างมากในการเปลี่ยนกิจกรรมและผลที่ตามมาในปัจจุบัน แน่นอนว่าระบบไม่สามารถปล่อยให้ปัญหาที่ตกต่ำหายไปโดยไม่ได้รับการจัดการ ความรับผิดที่อาจเกิดขึ้นจากเอาต์พุตที่ไม่ถูกต้องหรือความล้มเหลวร้ายแรงของชิปนั้นสูงเกินไปสำหรับระบบและแอปพลิเคชันในปัจจุบัน

ปัญหาการตกหล่นที่แปลเป็นภาษาท้องถิ่น

ตัวเร่งความเร็วเฉพาะแอปพลิเคชันถูกนำมาใช้กันอย่างแพร่หลายควบคู่กับโปรเซสเซอร์อเนกประสงค์เพื่อมอบประสิทธิภาพและประสิทธิภาพการใช้พลังงานที่จำเป็นสำหรับสภาพแวดล้อมการประมวลผลที่มีความต้องการในปัจจุบัน แต่ตัวเร่งความเร็วเหล่านี้ รวมถึงจำนวนคอร์ที่เพิ่มขึ้น และลักษณะของปริมาณงานที่ไม่สมดุล จะเพิ่มความเสี่ยงที่แรงดันไฟฟ้าตกเฉพาะจุด แรงดันไฟฟ้าตกเฉพาะจุดเหล่านี้เป็นผลมาจากกิจกรรมการสลับที่เพิ่มขึ้นอย่างฉับพลัน และอาจทำให้เกิดข้อผิดพลาดชั่วคราวและความล้มเหลวของโหมดภารกิจที่อาจเกิดขึ้นได้

เมื่อเกิดการตกต่ำเฉพาะที่ ผลกระทบสามารถบรรเทาลงได้ด้วยการปรับความถี่แบบไดนามิก ซึ่งทำได้โดยการปรับระยะเวลาของวงจรโดยใช้นาฬิกาที่ตั้งโปรแกรมได้ นาฬิกาที่ตั้งโปรแกรมได้ช่วยให้สามารถปรับความถี่นาฬิกาและเวลาแบบไดนามิกตามสภาพการทำงานปัจจุบันของวงจร

Movellus ทำให้การจัดการปัญหาการตกหล่นเป็นภาษาท้องถิ่นเป็นเรื่องง่าย

Movellus ผู้ให้บริการระบบ IP ดิจิทัลชั้นนำ ได้พัฒนากลุ่มผลิตภัณฑ์ Aeonic Generate เพื่อจัดการกับปัญหาการตกหล่นในพื้นที่ กลุ่มผลิตภัณฑ์ Movellus Aeonic นำเสนอโซลูชันการตอกบัตรแบบปรับเปลี่ยนได้ที่ให้การตอบสนองการตกต่ำอย่างรวดเร็ว กลุ่มผลิตภัณฑ์ประกอบด้วยระบบตอกบัตรแบบปรับได้ Building Block ถูกสร้างขึ้นด้วย Verilog ที่สามารถสังเคราะห์ได้ ทำให้มีความยืดหยุ่นอย่างแท้จริง โซลูชันนี้สามารถกำหนดค่า สแกนได้ และพกพากระบวนการได้สำหรับแอปพลิเคชัน SoC ขั้นสูงที่หลากหลาย

ผลิตภัณฑ์ในตระกูล Aeonic Generate ยังมีขนาดเล็กกว่าโซลูชันอะนาล็อกแบบดั้งเดิมอย่างมาก เป็นผลให้นักออกแบบสามารถสร้างอินสแตนซ์ IP ในระดับรายละเอียดที่ต้องการโดยไม่มีผลกระทบอย่างมีนัยสำคัญต่อพื้นที่ นอกจากนี้ ในขณะที่การออกแบบเคลื่อนไปสู่รูปทรงเรขาคณิตของกระบวนการที่ละเอียดยิ่งขึ้น พื้นที่ Aeonic Generate ก็ยังคงขยายขนาดต่อไป ทำให้เป็นโซลูชั่นที่ดีเยี่ยมสำหรับการออกแบบในอนาคต

กรณีการใช้งานสองสามกรณี

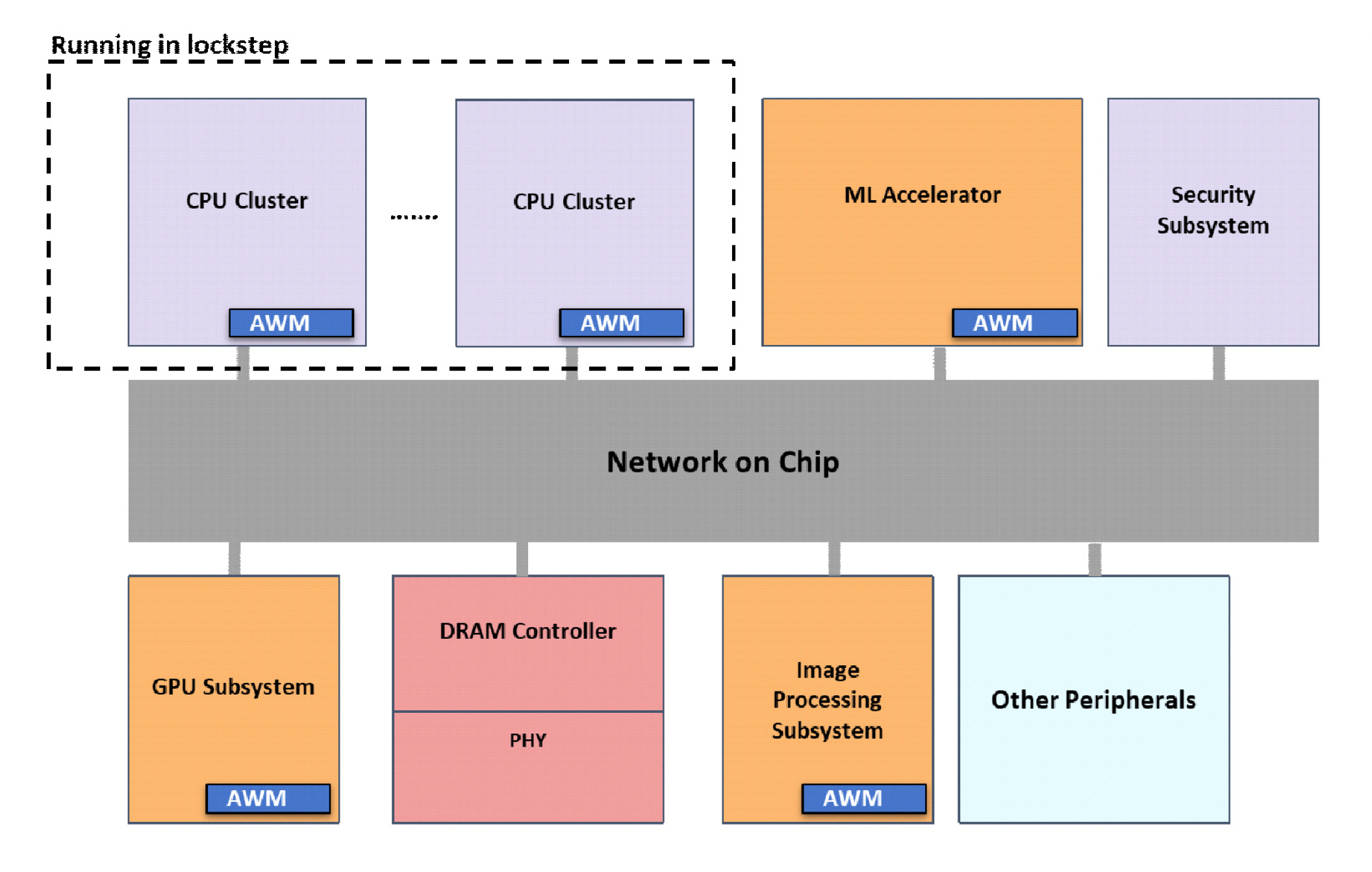

รูปภาพต่อไปนี้จาก Movellus แสดงตัวอย่างสถาปัตยกรรมของโปรเซสเซอร์ ADAS พร้อมด้วย Aeonic Generate AWM Platform สำหรับการรองรับการตกต่ำแบบโลคัลไลซ์ สถาปนิกจะจับคู่โมดูล AWM กับบล็อกย่อยหรือตัวเร่งความเร็วเฉพาะแอปพลิเคชัน เพื่อตอบสนองต่อปัญหาการลดลงเฉพาะที่ซึ่งขับเคลื่อนด้วยเวิร์กโหลดภายในห้ารอบสัญญาณนาฬิกา โดยมีการเปลี่ยนความถี่อย่างรวดเร็วและน้อยลง แนวทางนี้มอบโซลูชันที่เชื่อถือได้และมีประสิทธิภาพสำหรับจัดการกับความท้าทายของการตกหล่นเฉพาะที่ในตลาดเครือข่าย ADAS, 5G และศูนย์ข้อมูล

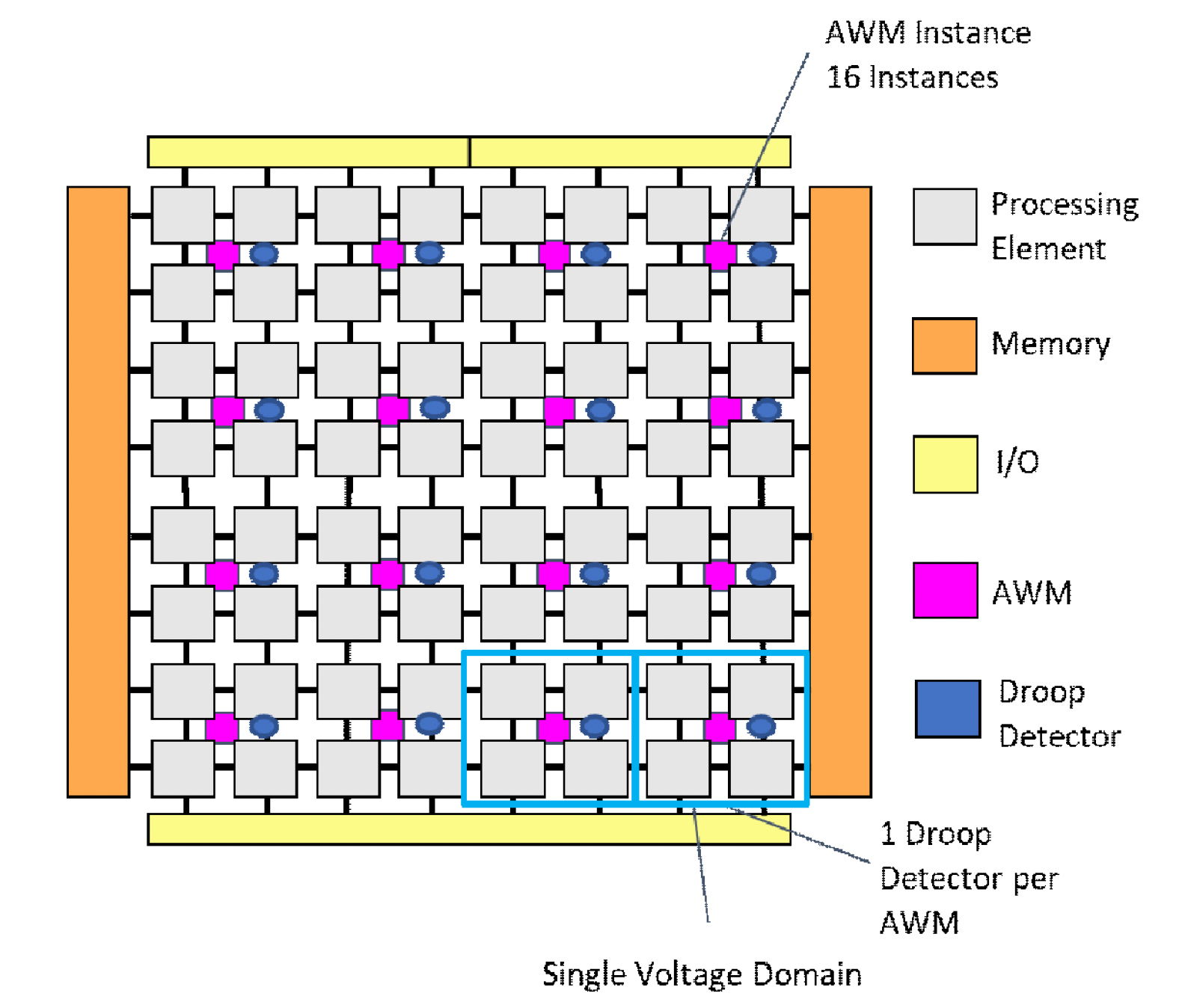

รูปต่อไปนี้จาก Movellus แสดงตัวอย่างสถาปัตยกรรมของ SoC โปรเซสเซอร์ที่มี Aeonic Generate สำหรับการรองรับการตกต่ำแบบโลคัลไลซ์ สถาปนิกจะจับคู่โมดูล Aeonic Generate AWM กับเครื่องตรวจจับการตกหล่นสำหรับคลัสเตอร์โปรเซสเซอร์และโดเมนแรงดันไฟฟ้าที่เกี่ยวข้อง เพื่อตอบสนองต่อการสูญเสียที่เกิดขึ้นเฉพาะที่ซึ่งขับเคลื่อนด้วยเวิร์กโหลดอย่างรวดเร็ว สิ่งนี้ช่วยให้นักออกแบบสามารถส่งมอบการตอบสนองการตกต่ำแบบโลคัลไลซ์และเป็นอิสระ โดยไม่ต้องเปลี่ยนแปลงประสิทธิภาพของคลัสเตอร์โปรเซสเซอร์ข้างเคียง

สรุป

แรงดันไฟฟ้าตกเฉพาะจุดสามารถเกิดขึ้นได้ใน SoC ที่ต่างกันซึ่งมีตัวเร่งความเร็วเฉพาะแอปพลิเคชัน การตกหล่นเหล่านี้สามารถนำไปสู่ข้อผิดพลาดด้านเวลา ข้อบกพร่องชั่วคราว และความล้มเหลวของโหมดภารกิจใน ADAS เครือข่ายศูนย์ข้อมูล และแอปพลิเคชัน 5G สถาปนิกระบบสามารถใช้การตอกบัตรแบบปรับเปลี่ยนได้เพื่อตอบสนองต่อการสูญเสียเหล่านี้และลดผลกระทบ

กลุ่มผลิตภัณฑ์ IP รุ่นนาฬิกาประสิทธิภาพสูง Movellus™ Aeonic Generate Adaptive Workload Module (AWM) เป็นส่วนหนึ่งของสถาปัตยกรรม Aeonic Intelligent Clock Network™ สำหรับข้อมูลเพิ่มเติม โปรดดูที่ Movellus' หน้า Aeonic Generate™ AWM.

ยังอ่าน:

ข้อดีของโดเมนการตอกบัตรแบบซิงโครนัสขนาดใหญ่ในการออกแบบชิป AI

ได้เวลาสำหรับเครือข่ายนาฬิกาอัจฉริยะแล้ว

ประโยชน์ด้านประสิทธิภาพ กำลังไฟฟ้า และพื้นที่ (PPA) ผ่านเครือข่ายนาฬิกาอัจฉริยะ

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- เพลโตบล็อคเชน Web3 Metaverse ข่าวกรอง ขยายความรู้. เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :เป็น

- 5G

- a

- คันเร่ง

- เร่ง

- ความถูกต้อง

- ประสบความสำเร็จ

- อยากทำกิจกรรม

- ปรับ

- AD

- นอกจากนี้

- นอกจากนี้

- ที่อยู่

- ที่อยู่

- ปรับ

- สูง

- AI

- ช่วยให้

- และ

- การใช้งาน

- เข้าใกล้

- สถาปัตยกรรม

- เป็น

- AREA

- AS

- ที่เกี่ยวข้อง

- At

- ตาม

- BE

- กลายเป็น

- ด้านล่าง

- ประโยชน์ที่ได้รับ

- ปิดกั้น

- Blocks

- การก่อสร้าง

- สร้าง

- by

- CAN

- สามารถรับ

- ไม่ได้

- รอบคอบ

- กรณี

- เป็นภัยพิบัติ

- ก่อให้เกิด

- ศูนย์

- ความท้าทาย

- ชิป

- ชิป

- นาฬิกา

- Cluster

- ร่วมกัน

- แข่งขัน

- สมบูรณ์

- ซับซ้อน

- คำนวณ

- การคำนวณ

- เงื่อนไข

- การพิจารณา

- ถือว่า

- การบริโภค

- อย่างต่อเนื่อง

- คอรัปชั่น

- ราคา

- ได้

- ตอบโต้

- คู่

- หลักสูตร

- ปัจจุบัน

- ลูกค้า

- รอบ

- ข้อมูล

- ศูนย์ข้อมูล

- ศูนย์ข้อมูล

- วัน

- ส่งมอบ

- เรียกร้อง

- ออกแบบ

- ได้รับการออกแบบ

- นักออกแบบ

- การออกแบบ

- การออกแบบ

- พัฒนา

- ดิจิตอล

- กระจาย

- หลาย

- โดเมน

- โดเมน

- วาด

- หล่น

- หยด

- พลวัต

- แบบไดนามิก

- แต่ละ

- อย่างมีประสิทธิภาพ

- ที่มีประสิทธิภาพ

- องค์ประกอบ

- สิ่งแวดล้อม

- สภาพแวดล้อม

- ข้อผิดพลาด

- ฯลฯ

- ตัวอย่าง

- ความล้มเหลว

- ฟอลส์

- ครอบครัว

- รูป

- มีความยืดหยุ่น

- ความผันผวน

- ดังต่อไปนี้

- สำหรับ

- ฟอร์ม

- เวลา

- ราคาเริ่มต้นที่

- ฟังก์ชัน

- อนาคต

- จุดประสงค์ทั่วไป

- สร้าง

- รุ่น

- ได้รับ

- เหตุการณ์ที่

- Go

- เป้าหมาย

- เกิดขึ้น

- ที่เกิดขึ้น

- มี

- จุดสูง

- ประสิทธิภาพสูง

- ถือ

- HTTPS

- ในอุดมคติ

- ส่งผลกระทบ

- ผลกระทบ

- การดำเนินการ

- in

- ไม่เที่ยง

- รวมถึง

- เพิ่ม

- เพิ่มขึ้น

- เพิ่มขึ้น

- ที่เพิ่มขึ้น

- อิสระ

- ข้อมูล

- แบบบูรณาการ

- บูรณาการ

- ฉลาด

- ภายใน

- IP

- ปัญหา

- ปัญหา

- IT

- ใหญ่

- ขนาดใหญ่

- นำ

- ชั้นนำ

- ชั้น

- ความรับผิดชอบ

- ชีวิต

- ในประเทศ

- อีกต่อไป

- ทำ

- เก็บรักษา

- ทำให้

- การทำ

- การจัดการ

- ขอบ

- ตลาด

- ความกว้างสูงสุด

- วิธีการ

- บรรเทา

- ซึ่งบรรเทา

- การบรรเทา

- โมดูล

- โมดูล

- ข้อมูลเพิ่มเติม

- มากที่สุด

- ย้าย

- ธรรมชาติ

- ความต้องการ

- เครือข่าย

- เครือข่าย

- สัญญาณรบกวน

- ยวด

- จำนวน

- of

- เสนอ

- on

- ONE

- การดำเนินงาน

- การดำเนินการ

- การเพิ่มประสิทธิภาพ

- การปรับให้เหมาะสม

- การเพิ่มประสิทธิภาพ

- อื่นๆ

- เอาท์พุต

- ส่วนหนึ่ง

- การปฏิบัติ

- ที่มีประสิทธิภาพ

- ปรากฏการณ์

- เวที

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- ผลงาน

- โพสต์

- ที่มีศักยภาพ

- อำนาจ

- พาวเวอร์ซัพพลาย

- กระบวนการ

- การประมวลผล

- หน่วยประมวลผล

- โปรเซสเซอร์

- ผลิตภัณฑ์

- ผู้จัดหา

- ให้

- ยก

- พิสัย

- รวดเร็ว

- อย่างรวดเร็ว

- อ่าน

- เรียลไทม์

- เหตุผล

- ลดลง

- การควบคุม

- ความเชื่อถือได้

- น่าเชื่อถือ

- จำเป็นต้องใช้

- ตอบสนอง

- คำตอบ

- ผล

- ส่งผลให้

- ขึ้น

- ความเสี่ยง

- วิ่ง

- ขนาด

- ปรับ

- เอเชียตะวันออกเฉียงใต้

- ร้ายแรง

- การติดตั้ง

- รุนแรง

- กะ

- แสดงให้เห็นว่า

- สัญญาณ

- สำคัญ

- อย่างมีความหมาย

- มีขนาดเล็กกว่า

- สมาร์ท

- ทางออก

- โซลูชัน

- บาง

- ช่องว่าง

- อย่างเช่น

- ฉับพลัน

- จัดหาอุปกรณ์

- สนับสนุน

- ฉลาด

- ระบบ

- ระบบ

- ตามกันไป

- เทคโนโลยี

- คำศัพท์

- ที่

- พื้นที่

- พื้นที่

- ของพวกเขา

- พวกเขา

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- ตลอด

- เวลา

- ครั้ง

- ระยะเวลา

- ไปยัง

- วันนี้

- เกินไป

- แบบดั้งเดิม

- ใช้

- หลากหลายมาก

- ผ่านทาง

- แรงดันไฟฟ้า

- ดี

- โด่งดัง

- ที่

- กว้าง

- ช่วงกว้าง

- อย่างกว้างขวาง

- จะ

- กับ

- ภายใน

- ไม่มี

- จะ

- ลมทะเล