ในโครงการออกแบบชิปขนาดใหญ่ ความพยายามในการตรวจสอบลอจิกอาจมากกว่าความพยายามในการออกแบบ โดยใช้เวลาถึง 70% ของเวลาโครงการตามข้อมูลจาก 2022 กลุ่มวิจัยวิลสัน ผลการวิจัย น่าเศร้าที่อัตราความสำเร็จของซิลิกอนตัวแรกลดลงจาก 31 เปอร์เซ็นต์เหลือเพียง 24 เปอร์เซ็นต์ในช่วง 8 ปีที่ผ่านมา ทำให้เกิดการหมุนอีกครั้งเพื่อแก้ไขข้อบกพร่อง ทำให้บริษัทต่าง ๆ สูญเสียเวลาในการเข้าสู่ตลาดและกระทบต่อแผนรายได้ของพวกเขาอย่างแน่นอน การตรวจสอบที่ดีกว่าจะช่วยปรับปรุงความสำเร็จของซิลิกอนตัวแรกได้อย่างแน่นอน แต่พูดง่ายกว่าทำ

ตัวเลขที่น่าวิตกอื่น ๆ จากการศึกษาของ Wilson Research Group:

- ASIC – 24% สำเร็จในครั้งแรก, 36% จบตรงเวลา

- FPGA – 16% บรรลุการหลบหนีข้อผิดพลาดเป็นศูนย์ 30% เสร็จสิ้นตรงเวลา

การตรวจสอบการออกแบบมีงานยากมากมาย: การดีบัก การสร้างการทดสอบ จากนั้นรันเอ็นจิ้น การพัฒนา Testbench และการวางแผนการทดสอบ ตามหลักแล้ว ทีมของคุณต้องการลดเวลาดำเนินการให้เหลือน้อยที่สุด บรรลุการปิดการตรวจสอบด้วยคนและทรัพยากรการประมวลผลน้อยที่สุด เป็นไปตามข้อกำหนดด้านความปลอดภัย และรู้ว่าเมื่อใดที่คุณภาพการออกแบบสูงพอที่จะหยุดการตรวจสอบ ในขณะที่ปฏิบัติตามกำหนดการของโครงการ

ฉันเพิ่งได้รับการอัปเดตจาก Darron May ผู้เชี่ยวชาญด้านการตรวจสอบการออกแบบที่ Siemens EDA เพื่อรับทราบเกี่ยวกับบางสิ่งที่เพิ่งประกาศเรียกว่า Questa การตรวจสอบ IQ. แนวทางของพวกเขาคือทั้งหมดที่เกี่ยวกับการยืนยันที่ขับเคลื่อนด้วยข้อมูลซึ่งเกิดขึ้นจากการตรวจสอบย้อนกลับ การทำงานร่วมกัน และการวิเคราะห์ที่ขับเคลื่อนโดย AI/ML การวิเคราะห์แบบดั้งเดิมให้ประสิทธิภาพที่จำกัดและข้อมูลเชิงลึกในการอธิบายและวิเคราะห์พฤติกรรมของลอจิก ในขณะที่การวิเคราะห์ที่ขับเคลื่อนด้วยข้อมูลขนาดใหญ่โดยใช้ AI/ML นำเสนอการดำเนินการเชิงคาดการณ์และเชิงกำหนดสำหรับการตรวจสอบ ทีมซอฟต์แวร์และฮาร์ดแวร์มีประสิทธิผลมากขึ้นโดยการทำงานร่วมกันผ่านการใช้ CI (บูรณาการต่อเนื่อง), คล่องแคล่ว วิธีการ ALM (Application Lifecycle Management) การออกแบบบนคลาวด์ และการใช้เทคนิค AI/ML อุตสาหกรรมที่มีความสำคัญด้านความปลอดภัยจำเป็นต้องมีความสามารถในการตรวจสอบย้อนกลับระหว่างข้อกำหนด การนำไปใช้ และการตรวจสอบตามที่กำหนดในมาตรฐานอุตสาหกรรม เช่น ISO 26262 และ DO-254

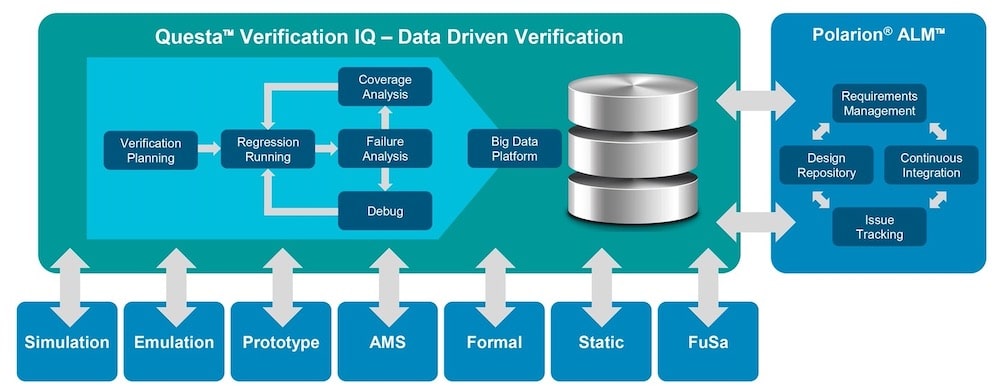

นี่คือภาพรวมของวิธีที่ Quest Verification IQ เชื่อมต่อข้อมูลทั้งหมดจากเครื่องมือตรวจสอบต่างๆ เข้าด้วยกันเป็นโฟลว์ที่ขับเคลื่อนด้วยข้อมูลพร้อมกับเครื่องมือ ALM

ข้อมูลความครอบคลุมรวบรวมจากการจำลองลอจิก (นี้), การจำลองและการสร้างต้นแบบ (Veloce), โรคเอเอ็มเอส (ซิมโฟนี), เป็นทางการ (วันสปิน), คงที่และ FuSa. ฟีเจอร์ ML จะวิเคราะห์ข้อมูลทั้งหมดนี้เพื่อคาดการณ์รูปแบบและเปิดเผยช่องโหว่ ระบุสาเหตุที่แท้จริง จากนั้นกำหนดการดำเนินการเพื่อปรับปรุงความครอบคลุม ALM ที่แสดงคือ โพลาไรออน จาก Siemens แม้ว่าคุณจะสามารถใช้ ALM อื่นได้ เช่นเดียวกับคุณสามารถใช้เครื่องมือการตรวจสอบที่คุณชื่นชอบ

Questa Verification IQ เป็นเฟรมเวิร์กบนเบราว์เซอร์ที่มีคู่มือกระบวนการ เพื่อให้คุณสามารถสร้างโฟลว์ที่สำคัญด้านความปลอดภัยโดยใช้การจัดการวงจรชีวิตเพื่อวางแผนและติดตามข้อกำหนดทั้งหมด ตัวนำทางการถดถอยช่วยให้ทีมของคุณสามารถสร้างและดำเนินการทดสอบ ตรวจสอบผลลัพธ์ และมีประวัติการตรวจสอบที่สมบูรณ์ ด้วยเครื่องมือวิเคราะห์ความครอบคลุม คุณจะรู้ว่าความครอบคลุมของคุณสำหรับโค้ด บล็อคการทำงาน และแผนการทดสอบนั้นสมบูรณ์เพียงใด สุดท้าย การวิเคราะห์ข้อมูลที่นำเสนอให้คุณมีแพลตฟอร์มเมตริก โดยใช้แดชบอร์ดโครงการและให้การวิเคราะห์ข้าม

เฟรมเวิร์กบนเว็บปรับขนาดสำหรับโครงการอิเล็กทรอนิกส์ทุกขนาด และคุณไม่ต้องติดตั้งซอฟต์แวร์ใดๆ หรือกังวลเกี่ยวกับการอัปเดต OS ของคุณ นอกจากนี้ยังรองรับการตั้งค่าคลาวด์สาธารณะ ส่วนตัว หรือไฮบริด เมื่อใช้ AI/ML กระบวนการปิดการตรวจสอบจะเร็วขึ้น ในขณะที่ความพยายามในการแก้ไขจุดบกพร่องจะเร็วขึ้นเนื่องจากการวิเคราะห์สาเหตุที่แท้จริงจะช่วยระบุจุดที่ควรปรับปรุง

ฉันถาม Darron May สองสามคำถามที่ชัดเจน

ถาม: ฉันสามารถผสมและจับคู่ Questa Verification IQ กับเครื่องมือผู้จำหน่าย EDA และ ALM ได้หรือไม่

A: Questa Verification IQ รองรับเครื่องมือและเอ็นจิ้น ALM ผ่านแนวทางมาตรฐาน โดยจะเชื่อมต่อกับเครื่องมือ ALM โดยใช้บริการ Open Services for Lifecycle Collaboration (OSLC) เพื่อให้สามารถใช้เครื่องมือใดๆ ที่รองรับมาตรฐาน เช่น Doors next หรือ Siemens Polarion และ Teamcenter ได้ Questa Verification IQ สามารถเปิดใช้งานเอ็นจิ้นใดก็ได้ และอีกครั้งที่เราได้รับการสนับสนุนสำหรับความครอบคลุมผ่าน Unified Coverage Interoperability Standard (UCIS)

ถาม: วิธีการนี้เปรียบเทียบกับ Synopsys DesignDash อย่างไร

A: Synopsys DesignDash มุ่งเน้นไปที่ ML สำหรับข้อมูลการออกแบบ ในขณะที่ Questa Verification IQ มุ่งเน้นไปที่การตรวจสอบข้อมูลที่ขับเคลื่อนด้วยข้อมูลโดยใช้การวิเคราะห์ ซึ่งรวมถึง ML เพื่อเร่งการปิดการตรวจสอบ ลดเวลาดำเนินการ และมอบประสิทธิภาพกระบวนการสูงสุด Questa Verification IQ มอบแอปพลิเคชันที่จำเป็นสำหรับการจัดการการตรวจสอบร่วมกันแบบทีมในเฟรมเวิร์กบนเบราว์เซอร์พร้อมการเข้าถึงข้อมูลแบบรวมศูนย์

ถาม: วิธีการนี้เปรียบเทียบกับ Cadence Verisium อย่างไร

A: Cadence Verisium มุ่งเน้นที่ ML Assisted Verification เท่านั้น เมื่อเปรียบเทียบกัน Siemens Questa Verification IQ มอบโซลูชันการตรวจสอบข้อมูลที่สมบูรณ์ซึ่งขับเคลื่อนโดย Analytics การทำงานร่วมกัน และการตรวจสอบย้อนกลับ การจัดการการตรวจสอบมีให้ในเครื่องมือบนเบราว์เซอร์พร้อมแอปพลิเคชันที่สร้างขึ้นจากการทำงานร่วมกัน เครื่องมือวิเคราะห์ความครอบคลุมนำเสนอเครื่องมือการปิดความครอบคลุมที่ทำงานร่วมกันเป็นครั้งแรกของอุตสาหกรรมโดยใช้การนำทางเชิงวิเคราะห์ที่ช่วยเหลือโดย ML คำถาม การยืนยันอินเทอร์เฟซ IQ กับ Siemens Polarion โดยใช้ OSLC และให้การตรวจสอบย้อนกลับของเธรดแบบดิจิทัลอย่างเข้มงวดด้วย Application Lifecycle Management โดยไม่มีการเปลี่ยนแปลงบริบทของ UI นำพลังของ ALM มาสู่การตรวจสอบฮาร์ดแวร์

สรุป

ฉันประทับใจเสมอกับเครื่องมือ EDA ใหม่ๆ ที่ทำให้งานที่ซับซ้อนง่ายขึ้นโดยการทำงานอย่างชาญฉลาดขึ้น โดยไม่จำเป็นต้องให้วิศวกรใช้เวลาทำงานด้วยตนเองนานหลายชั่วโมง ด้วยการรับรอง Questa Verification IQ ล่วงหน้าจากบริษัทที่คุ้นเคยอย่าง Arm และ Nordic Semiconductor ดูเหมือนว่า Siemens EDA ได้เพิ่มบางสิ่งที่น่าสนใจสำหรับทีมตรวจสอบที่จะต้องพิจารณาดู

บล็อกที่เกี่ยวข้อง

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- เพลโตบล็อคเชน Web3 Metaverse ข่าวกรอง ขยายความรู้. เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/eda/324031-achieving-faster-design-verification-closure/

- a

- เกี่ยวกับเรา

- เร่งความเร็ว

- เข้า

- การเข้าถึงข้อมูล

- บรรลุ

- การบรรลุ

- การกระทำ

- การปฏิบัติ

- ที่เพิ่ม

- AI / ML

- ทั้งหมด

- แม้ว่า

- เสมอ

- การวิเคราะห์

- วิเคราะห์

- การวิเคราะห์

- การวิเคราะห์

- และ

- ประกาศ

- อื่น

- การใช้งาน

- การใช้งาน

- ประยุกต์

- การประยุกต์ใช้

- เข้าใกล้

- ARM

- รอบ

- อัตโนมัติ

- ตาม

- สมควร

- กำลัง

- ดีกว่า

- ระหว่าง

- ใหญ่

- รูปภาพขนาดใหญ่

- Blocks

- การนำ

- นำ

- Bug

- สร้าง

- สร้าง

- จังหวะ

- ที่เรียกว่า

- ก่อให้เกิด

- สาเหตุที่

- การก่อให้เกิด

- ส่วนกลาง

- อย่างแน่นอน

- เปลี่ยนแปลง

- ชิป

- การปิด

- เมฆ

- รหัส

- การทำงานร่วมกัน

- การทำงานร่วมกัน

- การทำงานร่วมกัน

- บริษัท

- เปรียบเทียบ

- การเปรียบเทียบ

- จับใจ

- สมบูรณ์

- ซับซ้อน

- การปฏิบัติตาม

- คำนวณ

- เกี่ยวข้อง

- เชื่อมต่อ

- พิจารณา

- สิ่งแวดล้อม

- ต่อเนื่องกัน

- ได้

- ความคุ้มครอง

- สร้าง

- การสร้าง

- วิกฤติ

- ข้าม

- ข้อมูล

- วิเคราะห์ข้อมูล

- ที่ขับเคลื่อนด้วยข้อมูล

- ออกแบบ

- พัฒนาการ

- ยาก

- ดิจิตอล

- ประตู

- ขับเคลื่อน

- ก่อน

- ง่ายดาย

- อย่างมีประสิทธิภาพ

- ความพยายาม

- อิเล็กทรอนิกส์

- ช่วยให้

- การรับรอง

- เครื่องยนต์

- วิศวกร

- เครื่องยนต์

- พอ

- ดำเนินการ

- ชำนาญ

- คุ้นเคย

- เร็วขึ้น

- ที่ชื่นชอบ

- ลักษณะ

- สองสาม

- ในที่สุด

- ชื่อจริง

- ครั้งแรก

- ข้อบกพร่อง

- ไหล

- มุ่งเน้น

- มุ่งเน้นไปที่

- เป็นทางการ

- ที่เกิดขึ้น

- กรอบ

- ราคาเริ่มต้นที่

- การทำงาน

- บัญชีกลุ่ม

- ให้คำแนะนำ

- ฮาร์ดแวร์

- จะช่วยให้

- จุดสูง

- ประวัติ

- หลุม

- ชั่วโมง

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- HTTPS

- เป็นลูกผสม

- เมฆไฮบริด

- การดำเนินงาน

- ประทับใจ

- ปรับปรุง

- in

- รวมถึง

- รวมทั้ง

- อุตสาหกรรม

- อุตสาหกรรม

- มาตรฐานอุตสาหกรรม

- ของอุตสาหกรรม

- ความเข้าใจ

- ติดตั้ง

- บูรณาการ

- อินเตอร์เฟซ

- การทำงานร่วมกัน

- มาตรฐาน ISO

- IT

- การเก็บรักษา

- ทราบ

- ที่มีขนาดใหญ่

- เปิดตัว

- ถูก จำกัด

- ที่ต้องการหา

- LOOKS

- ทำ

- การจัดการ

- คู่มือ

- หลาย

- ตลาด

- การจับคู่

- ความกว้างสูงสุด

- สูงสุด

- พบ

- ที่ประชุม

- วิธีการ

- เมตริก

- ML

- การตรวจสอบ

- ข้อมูลเพิ่มเติม

- การเดินเรือ

- Navigator

- จำเป็นต้อง

- จำเป็น

- ใหม่

- ถัดไป

- ตัวเลข

- เสนอ

- เปิด

- ใบสั่ง

- OS

- อื่นๆ

- อดีต

- รูปแบบ

- คน

- เปอร์เซ็นต์

- ภาพ

- แผนการ

- การวางแผน

- แผน

- เวที

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- จุด

- โพสต์

- อำนาจ

- ขับเคลื่อน

- คาดการณ์

- กำหนด

- นำเสนอ

- ส่วนตัว

- กระบวนการ

- ประสิทธิผล

- ผลผลิต

- โครงการ

- โครงการ

- การสร้างต้นแบบ

- ให้

- ให้

- ให้

- การให้

- สาธารณะ

- ใส่

- คุณภาพ

- การแสวงหา

- คำถาม

- คำถาม

- คะแนน

- มาถึง

- เมื่อเร็ว ๆ นี้

- ลด

- ถดถอย

- ความต้องการ

- การวิจัย

- กลุ่มวิจัย

- แหล่งข้อมูล

- ผลสอบ

- เปิดเผย

- รายได้

- ราก

- วิ่ง

- ความปลอดภัย

- กล่าวว่า

- ตาชั่ง

- กำหนด

- สารกึ่งตัวนำ

- บริการ

- แสดง

- ซีเมนส์

- ซิลิคอน

- จำลอง

- ขนาด

- อย่างชาญฉลาด

- So

- ซอฟต์แวร์

- ทางออก

- บางสิ่งบางอย่าง

- สปิน

- มาตรฐาน

- มาตรฐาน

- หยุด

- ศึกษา

- ความสำเร็จ

- สนับสนุน

- ที่สนับสนุน

- รองรับ

- การ

- งาน

- ทีม

- ทีม

- เทคนิค

- ทดสอบ

- การทดสอบ

- พื้นที่

- ของพวกเขา

- ตลอด

- เวลา

- ครั้ง

- ไปยัง

- ร่วมกัน

- เครื่องมือ

- เครื่องมือ

- ตรวจสอบย้อนกลับ

- ลู่

- แบบดั้งเดิม

- ui

- ปึกแผ่น

- บันทึก

- ให้กับคุณ

- ใช้

- ต่างๆ

- ผู้ขาย

- การตรวจสอบ

- การตรวจสอบ

- ผ่านทาง

- web-based

- ในขณะที่

- วิกิพีเดีย

- วิลสัน

- การทำงาน

- จะ

- ปี

- ของคุณ

- ลมทะเล

- เป็นศูนย์