Den var in igen 1991 att Cadence först tillkännagav Virtuoso-produktnamnet, och här är vi 32 år senare och produkten lever och klarar sig ganska bra. Steven Lewis från Cadence gav mig en uppdatering om något nytt som de kallar Virtuos studio, och det handlar om anpassad IC-design för den verkliga världen. Under de 32 åren har vi sett halvledarprocessen marschera längs Moores lag från 600nm med hjälp av plan CMOS, skala ner till FinFET-eran under 22 nm, och nå GAA vid 3nm-noden. Uppenbarligen har kraven på EDA-verktyg förändrats eftersom mindre noder skapat nya fysiska effekter som behövde modelleras och simuleras för att säkerställa första kiselframgång.

Fokus för Cadence Virtuoso Studio är att hjälpa IC-designers att ta sig an dagens utmaningar genom sex områden:

- Ökad processkomplexitet

- Hanterar 10,000 XNUMX-tals kretssimuleringar

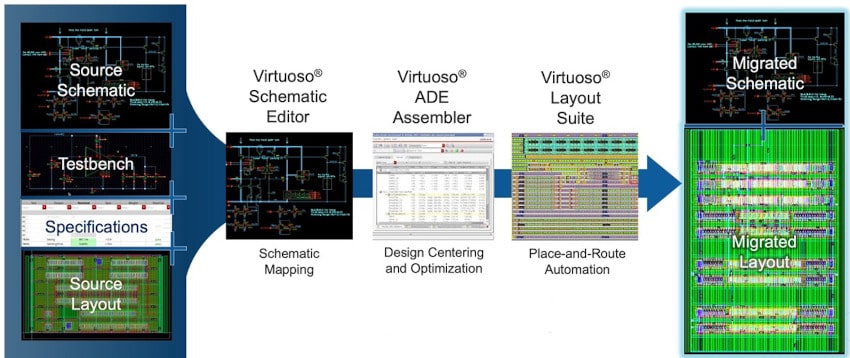

- Designautomation och kretsmigrering

- Heterogen integration

- AI

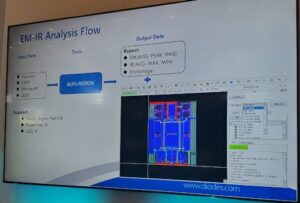

- Sign-off, in-design verifiering och analys

Smakämnen Virtuos ADE (Analog Design Environment) tillåter kretsingenjörer att utforska sina analoga, blandade signaler och RFIC-designer genom schematisk insamling och kretssimulering. Arkitekturen i Virtuoso ADE har förnyats för bättre jobbkontroll, minskad RAM-användning och påskynda simuleringar genom att använda molnet. Till exempel minskade RAM-minnet som krävs för att köra Spectre på 10,000 420-tals simuleringar från 18 MB ner till bara 420 MB för simuleringsövervakning, medan uttrycksutvärderingar minskade från 280 MB RAM till bara XNUMX MB.

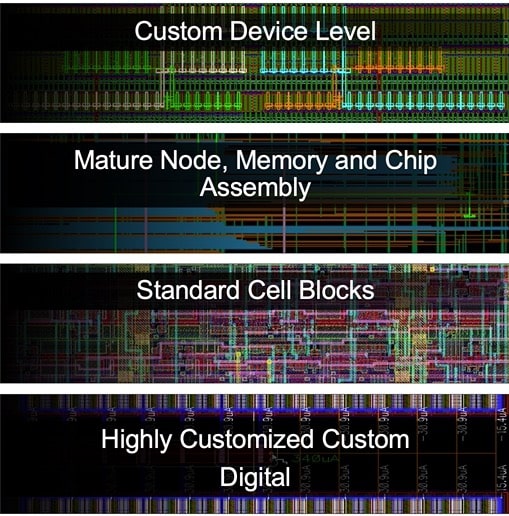

Uppdateringar till Virtuos layoutsvit inkluderar fyra val av plats- och ruttteknik, var och en lämpad för den unika uppgiften genom den virtuosa miljön:

Fyra P&R-tekniker

DRC- och LVS-körningar är en del av fysisk verifiering, och att köra dessa i batch-läge, fixa och upprepa, leder till långa utvecklingsscheman. In-design-verifiering tillåter interaktiv användning av DRC och LVS medan du arbetar på en IC-layout, så feedback om vad som ska ändras framhävs snabbt, vilket accelererar produktiviteten. En layoutdesigner som använder Virtuoso Layout Suite drar nytta av in-designverifiering med hjälp av Pegasus DRC och LVS-teknik.

Chiplets, 2.5D- och 3D-paketering spänner över de traditionellt separata områdena av PCB-, paket- och IC-designdomäner. Virtuoso Studio möjliggör samdesign och verifiering av paket, moduler och IC:er genom:

När du tittar in i en nära framtid kan du förvänta dig att se detaljer dyka upp om hur AI tillämpas för att automatiskt gå från ett analogt schema till layout baserat på maskininlärning och specifikationer. Dessa automatiskt genererade testlayouter kommer ytterligare att påskynda en mycket arbetsintensiv process. Ett andra utvecklingsområde för AI som ska tillämpas är problemet med att migrera anpassad analog IP till en ny processnod. Håll ögonen öppna.

Tidiga kunder hos Virtuoso Studio inkluderar Analog Devices för samdesign av IC och paket, ledande IC-konsumentdesigner på MediaTek och AI-baserad processmigrering på Renesas.

Sammanfattning

Virtuoso Studio har infört några imponerande nya funktioner i release 23.1 som IC-designteam kan börja använda för att bli mer produktiva. Den virtuosa infrastrukturen har förändrats för att möta utmaningarna i Moores lag, simuleringar med 10,000 2.5-tals kretssimuleringar är praktiska, RFIC och modul 3D/XNUMXD co-design stöds, in-design DRC/LVS-verifiering tar mycket kortare tid, och AI är används för att automatisera analoga uppgifter.

Relaterade bloggar

Dela det här inlägget via:- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- Platoblockchain. Web3 Metaverse Intelligence. Kunskap förstärkt. Tillgång här.

- Minting the Future med Adryenn Ashley. Tillgång här.

- Källa: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- : har

- :är

- $UPP

- 1

- 10

- 3d

- a

- Om oss

- accelererande

- AI

- Alla

- tillåter

- längs

- och

- meddelade

- tillämpas

- arkitektur

- ÄR

- OMRÅDE

- områden

- AS

- At

- automatisera

- automatiskt

- Automation

- tillbaka

- baserat

- BE

- varit

- Där vi får lov att vara utan att konstant prestera,

- nedan

- Fördelarna

- Bättre

- fört

- by

- Kadens

- Ring

- KAN

- fånga

- utmaningar

- byta

- val

- klart

- cloud

- Konsumenten

- kontroll

- beställnings

- Kunder

- dag

- krav

- Designa

- designer

- konstruktörer

- mönster

- detaljer

- Utveckling

- enheter

- gör

- domäner

- ner

- varje

- effekter

- möjliggör

- Ingenjörer

- säkerställa

- Miljö

- Era

- utvärderingar

- exempel

- förvänta

- utforska

- Funktioner

- återkoppling

- Förnamn

- Fokus

- För

- fyra

- från

- ytterligare

- framtida

- Go

- sidan

- Har

- hjälpa

- här.

- Markerad

- Hur ser din drömresa ut

- html

- HTTPS

- ICS

- imponerande

- in

- innefattar

- Infrastruktur

- interaktiva

- IP

- Jobb

- jpg

- arbetskraft

- Lag

- Layout

- Leads

- inlärning

- Lewis

- Lång

- Maskinen

- maskininlärning

- Mars

- max-bredd

- Möt

- migration

- Mode

- modul

- Moduler

- övervakning

- mer

- namn

- Nära

- behövs

- Nya

- Nya funktioner

- nod

- noder

- of

- on

- ONE

- paket

- paket

- förpackning

- del

- fysisk

- Plats

- plato

- Platon Data Intelligence

- PlatonData

- Inlägg

- Praktisk

- presentera

- Problem

- process

- Produkt

- produktiv

- produktivitet

- sätta

- snabbt

- RAM

- nå

- verklig

- verkliga världen

- Minskad

- reducerande

- frigöra

- Obligatorisk

- Rutt

- Körning

- rinnande

- skalning

- Andra

- se detaljer

- halvledare

- separat

- Kisel

- simulering

- SEX

- mindre

- So

- några

- något

- span

- specifikationer

- spöke

- fart

- starta

- bo

- studio

- framgång

- svit

- Som stöds

- Ta

- tar

- uppgift

- uppgifter

- lag

- Teknologi

- den där

- Smakämnen

- deras

- Dessa

- Genom

- tid

- till

- verktyg

- traditionellt

- rättegång

- unika

- Uppdatering

- Användning

- användning

- Verifiering

- via

- VÄL

- Vad

- medan

- kommer

- med

- arbetssätt

- världen

- år

- zephyrnet