Med ett ökande antal företag som är intresserade av enheter baserade på RISC-V ISA, och ett växande antal kärnor, acceleratorer och infrastrukturkomponenter som görs tillgängliga, antingen kommersiellt eller i öppen källkod, står slutanvändare inför en allt svårare utmaning att se till att de gör de bästa valen.

Varje användare kommer sannolikt att ha en uppsättning behov och bekymmer som nästan motsvarar flexibiliteten hos RISC-V-erbjudandena, som sträcker sig långt bortom traditionella PPA-mått till säkerhets- och säkerhetsfrågor eller kvalitetsöverväganden. Det kan inkludera anpassningsförmågan hos verifieringssäkerheten, vilket gör det möjligt för den arkitektoniska utvidgningen och den nödvändiga verifieringen att följa med.

Traditionellt har tre nivåer av prototyper implementerats – virtuella prototyper, emulering och FPGA-prototyper, inklusive hybrider mellan dem. Varje plattform används sedan för en mängd olika ändamål, inklusive programvaruverifiering, arkitekturvalidering, funktionsverifiering av hårdvaran, prestandaanalys och mer.

Medan design- och mjukvaruekosystemen för RISC-V håller på att etableras, är ekosystemen för konfiguration och verifiering eftersläpande och kräver ny teknik för att byggas. Det är själva flexibiliteten hos RISC-V som skapar enorma utmaningar för verifiering, utöver vad som krävs för verifiering av fasta processorer. Det gör också gemensam utveckling av hårdvara och mjukvara inte bara möjlig utan också nödvändig.

Samutveckling

Tidigare valdes hårdvara och sedan utvecklades mjukvara för att köras på den. Med RISC-V drivs hårdvaran ofta av mjukvara. "Det första du måste välja är vilka standard RISC-V-alternativ du vill ha", säger Simon Davidmann, grundare och VD för Imperas programvara. "RISC-V-funktionsuppsättningen har för närvarande 200 eller 300 alternativ. Hur vet du om din algoritm skulle dra nytta av en flyttalsenhet, eller SIMD, hårdvarumultiplikatorer eller till och med en vektormotor? Du måste räkna ut de hårdvarufunktioner du kommer att behöva, och har råd med, för den typ av applikation eller jobb som du vill att processorn ska göra. Det blir lite av en utmaning i sig.”

Det krävs prototyper för att göra den typen av avvägningar. "Om designerns mål är att utvärdera prestanda och lämplighet för ändamålet, så är virtuell prototypframställning det enda hållbara valet", säger Steve Roddy, CMO på Quadric. "Att bygga hårdvaruprototyper är mer än 10 till 50 gånger mer tidskrävande än att skapa en SystemC-modell av ett delsystem eller hela SoC. Den virtuella SystemC-prototypen körs i allmänhet tillräckligt snabbt för att svara på prestandafrågor, som hur många bildrutor per sekund av genomströmning kan jag få med den här processorkärnan, eller vad är topp- och medelbandbreddskravet för funktion X, inom en acceptabel noggrannhet.

Att få rätt noggrannhet kan vara svårt. "Det handlar om noggrannhet och din förmåga att snurra en modell väldigt snabbt", säger Frank Schirrmeister, vice vd för lösningar och affärsutveckling på Arteris IP. "Rätt noggrannhet definieras av vad din fråga än kräver, och att generera dem är inte trivialt. Om du är en ASIP-leverantör kommer du att kunna generera dem från vilken mall du än har. Beroende på frågan kan du behöva pipelinenoggrannhet, du kan behöva minnesnoggrannhet, den behöver inte vara helt korrekt, men när du har en CAD-avdelning inblandad är de för rädda för att svara på fel fråga.”

Men noggrannhet är en avvägning mot hastighet. "Medan vissa virtuella prototyper är cykelnoggranna, går dessa ofta för långsamt för att kunna ha den nödvändiga mjukvarukapaciteten", säger Imperas Davidmann. "De virtuella prototyperna med högsta prestanda är inte prestandamotorer, eftersom de inte modellerar processorpipelines. De tittar på det från en mjukvarusynpunkt, där du kan kompilera det och köra det på hårdvara, och du kan se ungefärlig prestanda genom att titta på antalet instruktioner eller ungefärliga tidsuppskattningar. Detta borde vara tillräckligt för att fatta den här typen av arkitektoniska beslut."

Det krävs ofta flera prototyper. "Vi brukar prototyper av två skäl", säger Venki Narayanan, senior director för mjukvaru- och systemteknik inom Microchip Technologys affärsenhet FPGA. "En är för arkitektonisk validering för att säkerställa att vi uppfyller alla prestandamått och krav och funktionsvalidering. Den andra anledningen är utveckling av inbäddad programvara och firmware. Vi använder olika nivåer av prototyptekniker, där det vanligaste är att använda våra egna FPGA:er för att utveckla en emuleringsplattform för både arkitektonisk och funktionell validering. Vi använder också arkitektoniska modeller som QEMU för att bygga virtuella plattformar för både prestandavalidering och inbyggd mjukvaruutveckling."

Antalet möjligheter växer. "Det finns många sätt som företag gör prototyper med RISC-V idag", säger Mark Himelstein, CTO för RISC-V International. "Dessa sträcker sig från enkortsdatorer på tillverkarnivå till LINUX-kompatibla kort för företag. Emuleringsmiljöer (som QEMU) gör det möjligt för utvecklare att utvecklas med mjukvara innan deras hårdvara är färdig, och det finns delar överallt från inbyggda SoC:er (från företag som Espressif och Telink), till FPGA:er (från företag som Microsemi), till den kommande Horse Creek-brädan från Intel och SiFive.”

Det kommer tillbaka till avvägningen mellan prestanda och noggrannhet. "Fysiska prototyper kräver mycket mer designansträngning, eftersom du ansluter och syntetiserar riktig RTL, men de levererar mycket större noggrannhet och genomströmning", säger Quadrics Roddy. "En fysisk prototyp i ett FPGA-system, vare sig det är hemmaodlat eller från de stora EDA-företagen, kräver ansträngning att få upp. Men den kan köra en storleksordning snabbare än en SystemC-modell, och flera storleksordningar snabbare än simulering på full gate-nivå. Designteam kommer vanligtvis att svänga från C-baserade modeller under IP-valprocessen till fysiska modeller för både verifiering av den faktiska designen efter IP-val och som en utvecklingsplattform för systemprogramvara."

När du väl vet vilken funktionsuppsättning du vill ha i hårdvaran kan du se efter om någon redan har skapat en lösning som uppfyller de flesta av dina behov. "Möjligheten är att med alla leverantörer där ute kommer det att finnas en kommersiell lösning som kommer att ha den typ av sak som du letar efter", säger Davidmann. "Men med RISC-V behöver du inte acceptera den lösningen som den är. En betydande del av värdet med RISC-V är friheten att ändra det, modifiera det och lägga till olika saker som du vill ha.”

Att välja en implementering

Det finns många sätt att implementera en uppsättning funktioner, till exempel antalet pipeline-steg eller spekulativa exekveringsfunktioner. Var och en kommer att ha olika avvägningar mellan kraft, prestanda och område. "ISA-smaken, vare sig det är RISC-V, Arm, Cadences Xtensa, Synopsys ARC, påverkar inte riktigt målen för modellering och prototypframställning och avvägningar", säger Roddy. "En systemarkitekt måste svara på frågor om SoC-designmål oavsett processormärke. På en teknisk nivå har RISC-V-vagnen verkligen en stabil position på marknaden i förhållande till verktygsstöd för modellering och prestandaanalys. Det finns många konkurrerande kärnleverantörer, var och en med olika implementeringar och processorfunktioner. Som en huvudsystems-CPU har den inte samma livslängd som en Arm, och därför har färre ekosystemspelare i EDA-världen brett validerat, färdigt att använda modelleringsstöd för standardiserade RISC-V-kärnor från olika varianter av RISC-V-leverantörer. Som en konfigurerbar, modifierbar kärna, släpar RISC-V-världen efter i nivån av instruktionsuppsättningsautomatisering som Tensilica har ägnat 25 år åt att bygga. Således har RISC-V mindre modelleringsstöd som en färdig byggsten och mindre automatisering att använda som en plattform för experiment med instruktionsuppsättningar."

Men det är bara en aspekt av en implementering som behöver utvärderas. Vad är kvaliteten på den? Om du vill ändra den, hur validerar du den på nytt?

Prestanda är den enklaste av dessa att bedöma. "Detta är inte annorlunda än att gå till vilken traditionell processorleverantör som helst", säger Davidmann. "De kommer att berätta för dig att den här kärnan ger dig så många Dhrystones per watt, de kommer att ge dig typiska processoranalytiska data, som säger att det är så här snabbt den här mikroarkitekturen körs. De har all den informationen, och alla som licensierar en processorkärna kommer att känna till den informationen och kommer att prata med dem och få den informationen. De kommer förmodligen att ha många valbara alternativ i sitt datablad, och de kommer att säga, "Om du aktiverar det här alternativet får du det eller det." Du kan titta på det på databladet, på leverantörernas webbplatser.”

På den här nivån behöver du förmodligen cykelnoggrannhet. "Jag ser att de flesta pumpar in det i en emulator och kör tillräckligt mycket data genom den för att fatta ett rimligt beslut", säger Schirrmeister. "Jag ser inte att det går upp till virtuella prototyper snart. Vissa företag pratar om FPGA-prototyper, där du har din egen enkortslösning. Beroende på vilken fråga du behöver besvara kan du bestämma dig för att konfigurera den, generera den och sedan pumpa in den i en FPGA för att köra mer data genom den, med lämpliga programvarurutiner ovanpå. Branschen har tillräckligt snabba inträde i emulatorer och prototyper för att göra detta möjligt. Det grundläggande problemet är att du vill fatta det här beslutet baserat på så exakt data du kan, men du kanske inte har den korrekta informationen vid den tidpunkten när du vill fatta det beslutet.”

Många av dessa prototyper måste innehålla mer än bara processorn. "Virtuella plattformar ger möjlighet att integrera med andra externa fysiska hårdvarufunktioner, såsom minne och sensorer som fungerar i en verklig miljö", säger Microchips Narayanan. ”Hybridsystem kan sammanföra virtuella plattformar med fysiska prototyper för andra externa funktioner. FPGA-emulering och prototyper hjälper till att hitta tidrelaterade buggar, såsom tävlingsförhållanden, eftersom detta är mer exakt på cykeln och externa funktioner körs med hastighet."

Verifiering

Eftersom processordesign har varit internt under lång tid finns det inget offentligt verifieringsekosystem för att bygga en processor och funktionerna i RISC-V kräver en mycket mer flexibel verifieringslösning än vad som någonsin funnits tidigare. Skapandet av detta har precis börjat hända.

"Det finns branschmått som Dhrystones eller CoreMark, så att folk kan jämföra prestanda", säger Davidmann. "Men hur kan du jämföra verifieringskvaliteten? Det måste finnas lika villkor så att varje leverantör kan säga: "Så här gör vi det." Vi behöver lite kvalitetsmått för verifiering.”

Det är här som öppen källkodsrörelsen kan hjälpa till. "Om du tittar på RISC-V-ekosystemet har du ett stort antal mycket erfarna processorutvecklare", säger Schirrmeister. "Det finns två ytterligheter. En är att jag får en kärna från en leverantör och om det inte fungerar har du problem med dem. Å andra sidan har jag total frihet och gör allt själv. En jämvikt håller på att utvecklas någonstans mellan dessa två ytterligheter. Du får något där en viss mängd verifiering tillhandahålls av din leverantör, och sedan är tilläggen ditt eget ansvar.”

Och det är här statistiken kommer in. "ISA-kompatibilitet är bara det första steget i en stege full av komplexitet som bara ett fåtal företag har klättrat på", säger Dave Kelf, VD för Breker Verification Systems. "Prototypframställning kan vara det enda sättet att helt säkerställa tillförlitlig processordrift, men att utnyttja verkliga arbetsbelastningar för att driva dessa prototyper skrapar på ytan av verklig processortäckning. Detta strider mot konkurrenskraften från en öppen ISA som driver påskyndad utveckling och tid till marknadsproblem.”

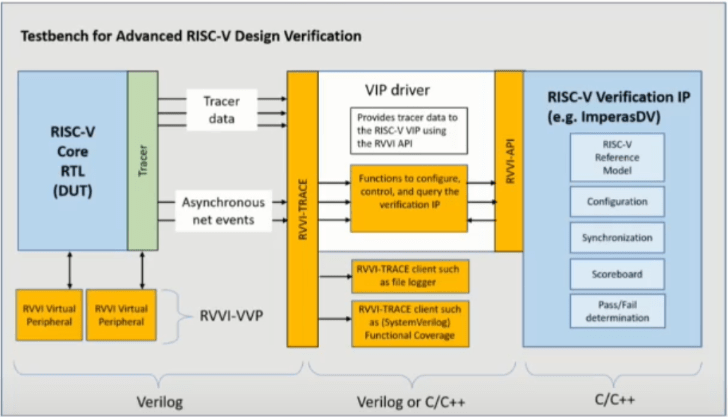

Men vad är dessa mätvärden? "I OpenHW-kvalitetsgruppen försöker vi räkna ut vad dessa mätvärden ska vara", säger Davidmann. "Det inkluderar saker som funktionell täckning, eftersom det inte bara är enkla instruktioner. För en högkvalitativ processor behöver du mycket mer än så. Du måste ha en metod för verifiering, där det finns förtroende för att dina jämförelser mot en referens täcker allt. Funktionell täckning visar bara att du har testet, men det måste kombineras med en metod som jämförs med någon form av känd referens. Vi kommer att lägga till felinsprutningsteknik så att det blir möjligt att ta reda på om din testbänk faktiskt upptäcker problem.”

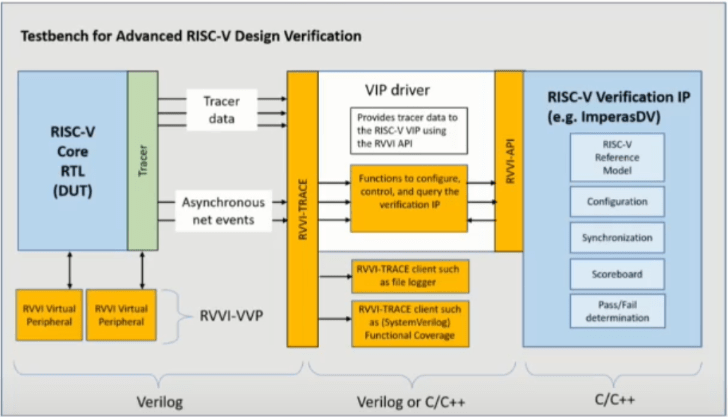

Fig. 1: Definiera arkitekturen för en RISC-V-verifieringslösning. Källa: Imperas

Det kommer att kräva en uppsättning verktyg. "När RISC-V-ekosystemet mognar börjar kommersiella implementeringar stödja definierade marknadssegment", säger Ashish Darbari, grundare och VD för Axiomise. "Vi ser stöd för marknader, som bilindustrin, som kräver funktionssäkerhet. Vi ser stöd för IoT som kräver säkerhet. RISC-V-leverantörer investerar i avancerade verifieringstekniker, inklusive virtuella prototyper för arkitektonisk modellering och prestanda. Verktyg är nu tillgängliga för tidig användning av formella metoder för att beskära buggar tidigt i designprocessen och undvika insättning av buggar eftersom designers kämpar för att fånga hörn-case buggar med simulering på processor-minnesgränssnittet."

Ett av verktygen som kommer att behövas är möjligheten att generera testfall baserat på en funktionslista eller en uppsättning funktioner. "Den automatiserade genereringen av testinnehåll för att driva prototyper som tar hänsyn till verifieringskomplexitet i tid är nyckeln", säger Breker's Kelf. "Dessa generationsmekanismer börjar nu dyka upp på marknaden."

Slutsats

Ett ekosystem är bara så bra som sin svagaste komponent, och för RISC-V är det EDA-verktygskedjan. Orsakerna till detta är tvåfaldiga. För det första, tills nyligen, fanns det ingen kommersiell marknad för verktyg för processorverifiering. Medan de existerade förr hade de alla antingen försvunnit eller upplösts i de äldre bearbetningsföretagen. För det andra skapar flexibiliteten hos RISC-V ISA en ny optimeringsmetod på systemnivå som kräver en ny uppsättning verktyg. Det tar tid för den här möjligheten att förstås och för kommersiella verktyg att dyka upp som på rätt sätt adresserar den.

Relaterad

En minimal RISC-V

Finns det plats för en ännu mindre version av en RISC-V-processor som skulle kunna ersätta 8-bitars mikrokontroller?

RISC-V skjuter in i huvudströmmen

Processorkärnor med öppen källkod börjar dyka upp i heterogena SoC:er och paket.

Effektiv spårning i RISC-V

Hur man arbetar med den nya felsökningsstandarden RISC-V.

Hur säkra är RISC-V-chips?

Öppen källkod i sig garanterar inte säkerhet. Det handlar fortfarande om grunderna för design.

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- Platoblockchain. Web3 Metaverse Intelligence. Kunskap förstärkt. Tillgång här.

- Källa: https://semiengineering.com/selecting-the-right-risc-v-core/

- 1

- 10

- a

- förmåga

- Able

- Om oss

- ovan

- accelererad

- acceleratorer

- Acceptera

- godtagbart

- Konto

- noggrannhet

- exakt

- faktiskt

- adress

- Antagande

- avancerat

- Efter

- mot

- algoritm

- Alla

- redan

- mängd

- analys

- Analytisk

- och

- och infrastruktur

- svara

- visas

- Ansökan

- tillvägagångssätt

- lämpligt

- Arc

- arkitektoniska

- arkitektur

- OMRÅDE

- ARM

- aspekt

- bedömas

- Automatiserad

- Automation

- fordonsindustrin

- tillgänglig

- genomsnitt

- tillbaka

- Bandbredd

- baserat

- grundläggande

- därför att

- blir

- passande

- innan

- Börjar

- Där vi får lov att vara utan att konstant prestera,

- fördel

- BÄST

- mellan

- Bortom

- Stor

- Bit

- Blockera

- ombord

- varumärke

- föra

- brett

- Bug

- fel

- SLUTRESULTAT

- Byggnad

- byggt

- företag

- affärsutveckling

- CAD

- kapacitet

- kapabel

- brottning

- VD

- vissa

- utmanar

- utmaningar

- chanser

- byta

- Pommes frites

- val

- val

- Välja

- Klättrade

- CMO

- Säkerheter

- komma

- kommersiella

- kommersiellt

- Gemensam

- Företag

- jämföra

- kompatibilitet

- tävlande

- konkurrenskraftig

- fullborda

- komplexiteter

- Efterlevnad

- komponent

- komponenter

- datorer

- oro

- villkor

- förtroende

- konfiguration

- Anslutning

- överväganden

- innehåll

- Kärna

- kunde

- kopplad

- täckning

- beläggning

- CPU

- skapas

- skapar

- Skapa

- skapande

- Bäck

- CTO

- För närvarande

- datum

- Dave

- Beslutet

- definierande

- leverera

- krav

- Avdelning

- beroende

- utplacerade

- Designa

- designprocessen

- konstruktörer

- utveckla

- utvecklade

- utvecklare

- utveckla

- Utveckling

- enheter

- olika

- svårt

- Direktör

- inte

- inte

- ner

- driv

- driven

- drivande

- under

- varje

- Tidig

- enklaste

- ekosystemet

- ekosystem

- ansträngning

- ansträngningar

- antingen

- inbäddade

- möjliggör

- Motor

- Teknik

- Motorer

- tillräckligt

- säkerställa

- säkerställa

- Företag

- Hela

- inträde

- Miljö

- miljöer

- lika

- Jämvikt

- etablerade

- uppskattningar

- utvärdera

- Även

- NÅGONSIN

- allt

- utförande

- erfaren

- sträcker

- förlängning

- förlängningar

- extern

- ytterligheter

- Ansikte

- bekant

- Mode

- SNABB

- snabbare

- Leverans

- Funktioner

- få

- fält

- Fig.

- hitta

- finna

- Förnamn

- passa

- fixerad

- Flexibilitet

- flexibel

- formen

- formell

- grundare

- Grundare och VD

- FPGA

- Frihet

- från

- full

- fullständigt

- fungera

- funktionella

- funktioner

- Fundamentals

- allmänhet

- generera

- generera

- generering

- skaffa sig

- få

- Ge

- ger

- Go

- Mål

- kommer

- god

- större

- Grupp

- Odling

- garanti

- hända

- hårdvara

- hjälpa

- hjälper

- hög kvalitet

- hemodlade

- Häst

- Hur ser din drömresa ut

- HTTPS

- stor

- Inverkan

- genomföra

- genomförande

- in

- innefattar

- innefattar

- Inklusive

- ökande

- alltmer

- industrin

- informationen

- Infrastruktur

- instruktioner

- integrera

- Intel

- intresserad

- Gränssnitt

- Internationell

- investera

- involverade

- iot

- IP

- problem

- IT

- sig

- Jobb

- Nyckel

- Snäll

- Vet

- känd

- stege

- Large

- Legacy

- Nivå

- nivåer

- hävstångs

- Licens

- sannolikt

- linux

- Lista

- Lång

- länge sedan

- livslängd

- se

- du letar

- gjord

- Huvudsida

- göra

- tillverkare

- GÖR

- många

- markera

- marknad

- Marknader

- mognar

- max-bredd

- Möt

- Minne

- Metodik

- metoder

- Metrics

- minimum

- modell

- modellering

- modeller

- modifiera

- mer

- mest

- rörelse

- rörliga

- nödvändigt för

- Behöver

- behov

- Nya

- antal

- talrik

- mål

- Odds

- offer~~POS=TRUNC

- ONE

- öppet

- öppen källkod

- drift

- drift

- Möjlighet

- optimering

- Alternativet

- Tillbehör

- beställa

- ordrar

- Övriga

- egen

- paket

- del

- reservdelar till din klassiker

- Tidigare

- Topp

- Personer

- prestanda

- fysisk

- rörledning

- pivot

- plattform

- Plattformar

- plato

- Platon Data Intelligence

- PlatonData

- spelare

- i

- Punkt

- Synvinkel

- placera

- Möjligheterna

- möjlig

- kraft

- VD

- förmodligen

- Problem

- problem

- process

- Processorn

- processorer

- Framsteg

- ordentligt

- Prototypen

- prototyper

- prototyping

- ge

- förutsatt

- leverantör

- allmän

- pump

- pumpning

- Syftet

- syfte

- kvalitet

- fråga

- frågor

- Lopp

- område

- färdiga

- verklig

- verkliga världen

- Anledningen

- rimlig

- skäl

- nyligen

- Oavsett

- pålitlig

- ersätta

- kräver

- Obligatorisk

- krav

- Krav

- Kräver

- ansvaret

- Rum

- Körning

- rinnande

- Säkerhet

- Säkerhet och trygghet

- Andra

- säkra

- säkerhet

- segment

- vald

- väljer

- Val

- senior

- sensor

- in

- flera

- skall

- show

- Visar

- signifikant

- Simon

- Enkelt

- simulering

- enda

- Långsamt

- mindre

- So

- Mjukvara

- mjukvaruutveckling

- lösning

- Lösningar

- några

- någon

- något

- någonstans

- Alldeles strax

- Källa

- fart

- spent

- Snurra

- stabil

- stadier

- standard

- Starta

- Steve

- Fortfarande

- Kamp

- sådana

- svit

- stödja

- yta

- system

- System

- Ta

- tar

- Diskussion

- tala

- lag

- Teknisk

- tekniker

- Teknologi

- mall

- testa

- Smakämnen

- deras

- därför

- sak

- saker

- tre

- Genom

- genomströmning

- tid

- tidskrävande

- gånger

- Tidpunkten

- till

- i dag

- tillsammans

- alltför

- verktyg

- topp

- Totalt

- spåra

- traditionell

- SVÄNG

- typisk

- typiskt

- förstått

- enhet

- kommande

- användning

- Användare

- användare

- validerade

- godkännande

- värde

- mängd

- leverantör

- försäljare

- Verifiering

- version

- genomförbar, livskraftig

- Vice President

- utsikt

- Virtuell

- virtuella plattformar

- önskar

- sätt

- webbsidor

- Vad

- Vad är

- om

- som

- medan

- kommer

- inom

- Arbete

- träna

- världen

- skulle

- Fel

- X

- år

- Din

- zephyrnet