Ett nytt tekniskt dokument med titeln "Non-Traditional Design of Dynamic Logics using FDSOI for Ultra-Efficient Computing" publicerades av forskare vid University of Stuttgart, UC Berkeley, Indian Institute of Technology Kanpur och TU München, med finansiering från German Research Foundation .

Abstrakt

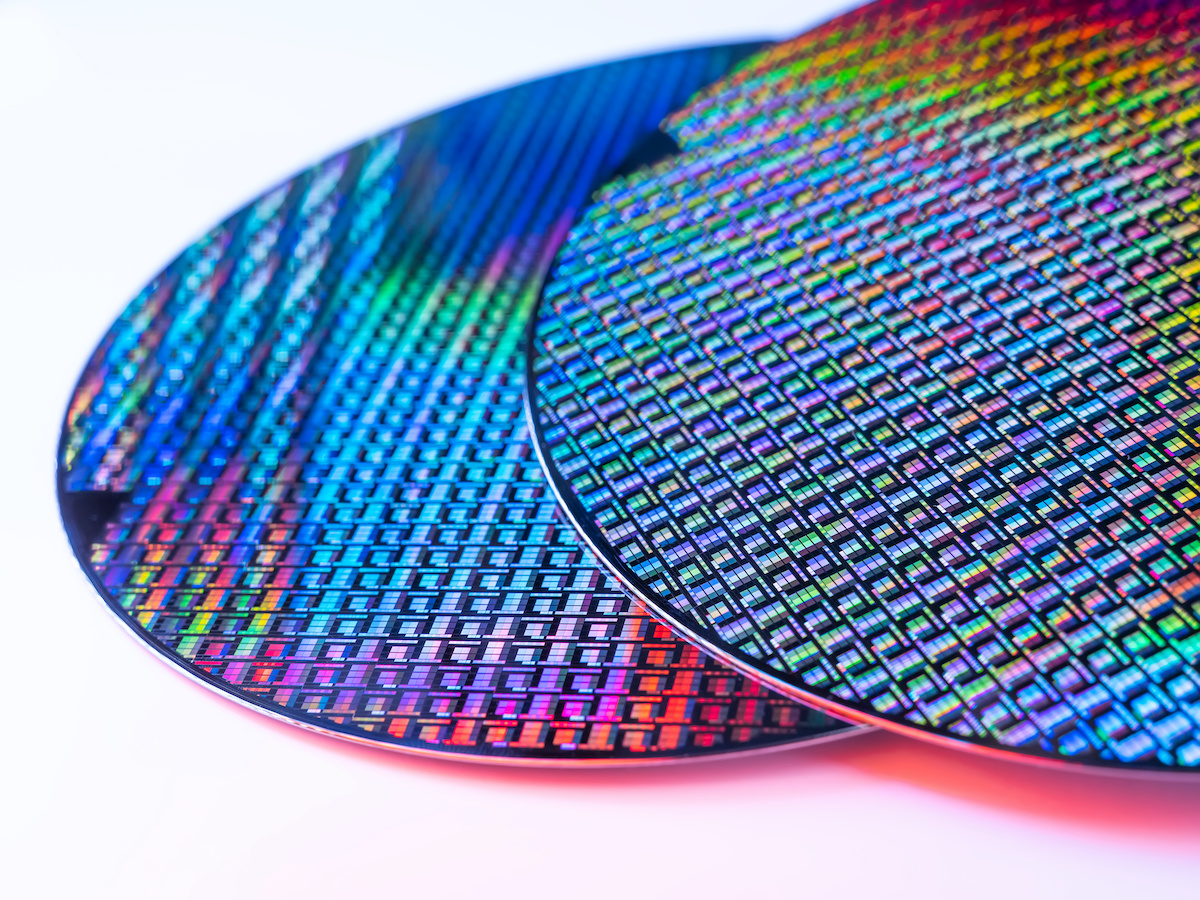

"I det här dokumentet föreslår vi en icke-traditionell design av dynamiska logiska kretsar som använder Fully-Depleted Silicon on Insulator (FDSOI) FET. FDSOI FET tillåter tröskelspänningen (Vt ) för att vara justerbar (dvs. låg-Vt- och hög-Vt-tillstånd) genom att använda bakgrindens förspänning. Vår design använder de främre och bakre grindarna på en FDSOI FET som ingångsterminaler och föreslår de dynamiska logiska grindarna (som; NAND, NOR, AND, OR, XOR och XNOR) och kretsar (som halvadderare och heladderare). Det kräver färre transistorer för att bygga dynamiska logiska grindar och uppnår hög prestanda med låg effektförlust jämfört med konventionella dynamiska logiska konstruktioner. Den kompakta industriella modellen av FDSOI FET (BSIM-IMG) har använts för att simulera dynamiska logiska grindar och är helt kalibrerad för att reproducera 14nm FDSOI FET-teknologinoddata. Kalibrering utförs för både elektriska egenskaper och processvariationer. Simuleringsresultaten visar en genomsnittlig förbättring av transistorantal, utbredningsfördröjning, effekt och effektfördröjningsprodukt på 23.43 %, 57.16 %, 47.05 % respektive 77.29 % jämfört med de konventionella designerna. Dessutom minskar vår design laddningsdelningseffekten, vilket påverkar körbarheten hos de dynamiska logiska grindarna. Dessutom har vi analyserat inverkan av processen, matningsspänning och belastningskapacitansvariationer på utbredningsfördröjningen av den dynamiska logikfamiljen i detalj. Resultaten visar att dessa variationer har en mindre inverkan på utbredningsfördröjningen av de föreslagna FDSOI-baserade dynamiska logiska grindarna jämfört med konventionella dynamiska logiska grindar."

Hitta tekniskt dokument här. Publicerad april 2023.

S. Kumar, S. Chatterjee, CK Dabhi, YS Chauhan och H. Amrouch, "Non-Traditional Design of Dynamic Logics using FDSOI for Ultra-Efficient Computing," i IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, doi: 10.1109/JXCDC.2023.3269141. Öppna Accesss.

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- PlatoAiStream. Web3 Data Intelligence. Kunskap förstärkt. Tillgång här.

- Minting the Future med Adryenn Ashley. Tillgång här.

- Köp och sälj aktier i PRE-IPO-företag med PREIPO®. Tillgång här.

- Källa: https://semiengineering.com/non-traditional-design-of-dynamic-logic-gates-and-circuits-with-fdsoi-fets/

- : har

- :är

- 10

- 2023

- 23

- 77

- a

- uppnår

- Dessutom

- justerbar

- tillåter

- an

- och

- April

- AS

- At

- genomsnitt

- tillbaka

- BE

- varit

- Berkeley

- förspänning

- båda

- SLUTRESULTAT

- by

- egenskaper

- laddning

- jämfört

- databehandling

- konventionell

- datum

- fördröja

- Designa

- mönster

- detalj

- enheter

- dynamisk

- e

- effekt

- familj

- FET

- färre

- För

- fundament

- främre

- full

- fullständigt

- finansiering

- ytterligare

- grindar

- tyska

- Hälften

- Har

- Hög

- HTTPS

- i

- IEEE

- Inverkan

- förbättring

- in

- indisk

- industriell

- ingång

- Institute

- IT

- tidskriften

- tycka om

- läsa in

- Logiken

- Låg

- mindre

- modell

- Munich

- Nya

- nod

- of

- on

- or

- vår

- Papper

- prestanda

- plato

- Platon Data Intelligence

- PlatonData

- kraft

- process

- Produkt

- föreslå

- föreslagen

- föreslår

- publicerade

- minskar

- Kräver

- forskning

- forskare

- respektive

- Resultat

- s

- delning

- show

- Kisel

- simulering

- Stater

- leverera

- Teknisk

- Teknologi

- den där

- Smakämnen

- Dessa

- detta

- tröskelvärde

- betitlad

- till

- universitet

- Begagnade

- med hjälp av

- Återvinnare

- Spänning

- var

- we

- som

- med

- zephyrnet