Minnen har alltid spelat en avgörande roll, både för att driva på utvecklingsfronten för halvledarprocesser och för att stödja de olika kraven från olika applikationer och användningsfall. Listan över de olika typer av minnen som används idag är lång. På bruttonivå kan vi klassificera minnen i flyktiga eller icke-flyktiga, läsbara eller läs-skriva, statiska eller dynamiska, etc. Och när det kommer till kostnad, prestanda, effekt och area/formfaktor för ett elektroniskt system , mycket bygger på användningen av alla rätt minnen för applikationen. Lejonparten av uppmärksamheten ägnas åt den effektiva användningen av Static Random Access Memories (SRAM) och Dynamic Random Access Memories (DRAMs) enligt de kompromissfördelar som kan erhållas. Medan behovet av minnen med högre densitet som förbrukar mycket låg ström och presterar som SRAM alltid har funnits där, kunde applikationer hantera med en klok blandning av DRAM och SRAM.

Men under de senaste åren har snabbt växande marknader som modem, edge connectivity och EdgeAI börjat kräva mer av minnen. Dessutom, med framväxten av Smart Internet of Things (IoT) och bärbar teknologi, finns det en ökande efterfrågan på minneslösningar som kan ge hög prestanda och låg strömförbrukning för att förlänga batteritiden. Dessa applikationer vill ha minnen som levererar prestanda- och effektfördelarna med SRAMs (över DRAMs) och tätheten och kostnadsfördelarna för DRAMs (över SRAMs) samlade i ett. Lyckligtvis uppfanns en sådan typ av minne för ganska länge sedan och kallas Pseudo Static Random Access Memory (PSRAM). PSRAM-tillverkarna väntade i kulisserna för adoptionsdrivrutiner som de ovan nämnda snabbväxande applikationerna. Listan över PSRAM-minnesleverantörer inkluderar AP Memory, Infineon, Micron Technology, Winbond Technology och andra.

Vad är PSRAM? [Källa: JEDEC.org]

(1) En kombinationsform av ett dynamiskt RAM som innehåller olika uppdaterings- och styrkretsar på chipet (t.ex. uppdateringsadressräknare och multiplexor, intervalltimer, arbiter). Dessa kretsar tillåter PSRAM-driftsegenskaperna att nära likna de hos ett SRAM.

(2) Ett slumpmässigt åtkomstminne vars interna struktur är ett dynamiskt minne med uppdateringsstyrsignaler genererade internt, i standby-läge, så att det kan efterlikna funktionen hos ett statiskt minne.

(3) PSRAMs har icke-multiplexerade adresslinjer och pinouts liknande SRAM.

Mobilbil

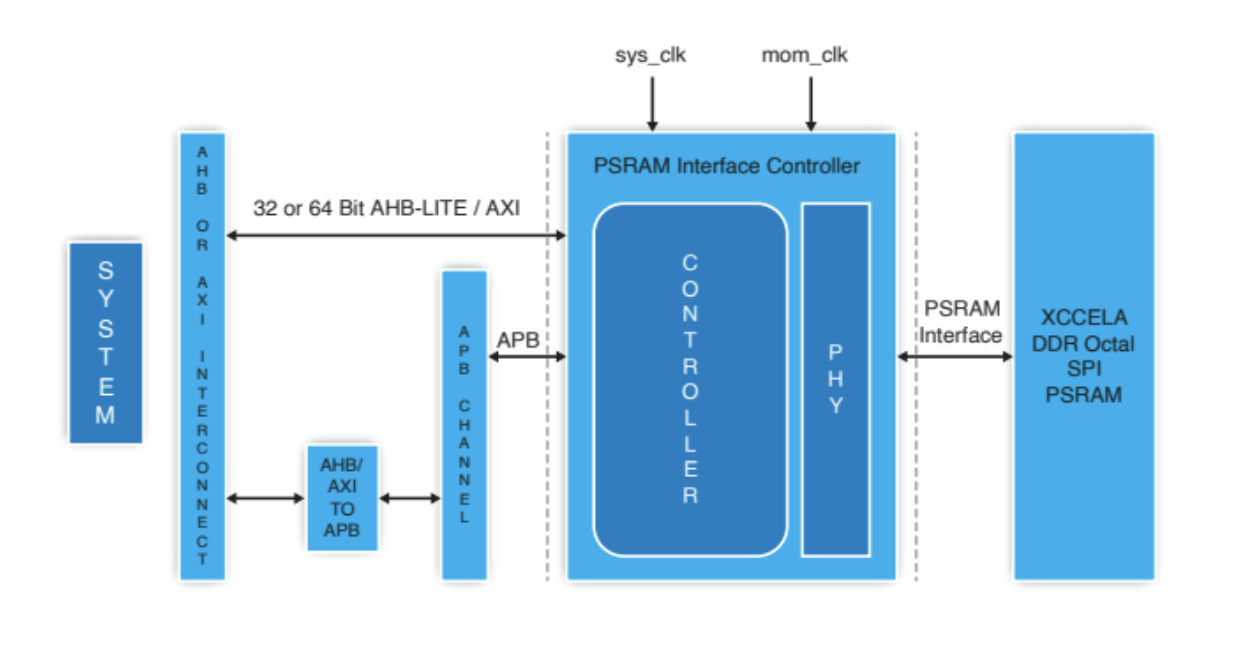

Mobiveil är ett snabbväxande teknikföretag som är specialiserat på utveckling av Silicon Intellectual Properties, plattformar och lösningar för olika snabbväxande marknader. Dess strategi är att växa med snabbt växande marknader genom att erbjuda sina kunder värdefulla IP:er som är lätta att integrera i SoC:er. En sådan IP är Mobiveils PSRAM Controller som har varit i massproduktion i mer än ett halvt decennium med kunder över hela USA, Europa, Israel och Kina. Styrenheten finns i olika systembussvarianter som AXI och AHB och stöder en mängd olika PSRAM- och HyperRAM-enheter från många leverantörer. Företaget utökade nyligen listan med tillägg av stöd för AP-minnen senaste 250MHz PSRAM-enheter.

AP minne

AP Memory är världsledande inom PSRAM och har hittills skickat mer än sex miljarder PSRAM-enheter. Företaget har positionerat sig som marknadsledare inom PSRAM-enheter och tillhandahåller en komplett produktlinje av högkvalitativa minneslösningar för att stödja IoT och bärbara marknadssegment. Företaget lanserar kontinuerligt konkurrenskraftiga produkter och tillhandahåller skräddarsydda minneslösningar baserade på kundernas krav.

Mobil-AP Memory Partnership

Detta partnerskap förväntar sig att ge betydande fördelar för SoCs, eftersom PSRAM-enheter erbjuder 10x högre densitet jämfört med eSRAM, 10x lägre effekt jämfört med standard DRAM och nära 3x färre stiftantal. Dessa fördelar kommer att resultera i lägre energiförbrukning, högre prestanda och kostnadsbesparingar för de system som använder PSRAM.

Resultatet av partnerskapet är en styrenhets IP som kommer att tillhandahålla kostnadseffektiva minneslösningar med ultralåg effekt för systemdesigners. Mobiveil har anpassat sin PSRAM Controller för att samverka med AP Memorys nya PSRAM-enhet som går upp till 250 MHz i hastighet och densiteter från 64Mb till 512Mb, med stöd för x8/x16-lägen. Denna integration kommer att göra det möjligt för SoC-designers att dra fördel av den höga prestandan hos PSRAM-kontrollern vid mycket låg effekt, vilket gör den idealisk för batteridrivna applikationer och förlänger standbytiden för enheter.

PSRAM-styrenheten stöder Octal Serial Peripheral Interface (Xccela-standard), vilket möjliggör hastigheter på upp till 1,000 16 Mbyte/s för ett XNUMX-stifts SPI-alternativ. Dessutom ger den stöd för ett direkt minnesmappat systemgränssnitt, automatisk sidgränshantering, linjär/omslutning/kontinuerlig/hybrid/burst-stöd och lågeffektfunktioner som djup och halv avstängning.

PSRAM-styrenhetens IP är systemvaliderad, processteknologioberoende och mycket konfigurerbar. För att lära dig mer om denna IP, ladda ner en kopia av den detaljerade produktbeskrivningen här.

Sammanfattning

Mobiveils flexibla affärsmodeller, starka industrinärvaro genom strategiska allianser och nyckelpartnerskap, dedikerat integrationsstöd och ingenjörsutvecklingscenter i Milpitas, Kalifornien, Chennai, Bangalore, Hyderabad och Rajkot, Indien, samt försäljningskontor och representanter över hela världen, har lagt till enorma värde för kunderna i att utföra sina produktmål inom budget och i tid. För att lära dig mer, besök www.mobileil.com.

Läs också:

Vd-intervju: Ravi Thummarukudy från Mobiveil

Dela det här inlägget via:

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- PlatoAiStream. Web3 Data Intelligence. Kunskap förstärkt. Tillgång här.

- Minting the Future med Adryenn Ashley. Tillgång här.

- Köp och sälj aktier i PRE-IPO-företag med PREIPO®. Tillgång här.

- Källa: https://semiwiki.com/ip/327824-memory-solutions-for-modem-edgeai-smart-iot-and-wearables-applications/

- : har

- :är

- $UPP

- 000

- 1

- 250

- a

- Able

- Om oss

- ovan

- accelerera

- tillgång

- tvärs

- anpassat

- lagt till

- Dessutom

- Dessutom

- adress

- Antagande

- Fördel

- fördelar

- sedan

- Alla

- tillåter

- alltid

- an

- och

- Ansökan

- tillämpningar

- ÄR

- AS

- At

- uppmärksamhet

- Automat

- tillgänglig

- baserat

- batteri

- Batteriets livslängd

- BE

- varit

- Fördelarna

- Blockera

- båda

- föra

- bred

- budget

- Bussen

- företag

- by

- CA

- kallas

- KAN

- Centers

- egenskaper

- Kina

- klassificera

- Stäng

- nära

- COM

- kommer

- företag

- jämfört

- konkurrenskraftig

- fullborda

- Anslutningar

- konsumera

- konsumtion

- kontinuerligt

- kontroll

- styrenhet

- Pris

- kostnadsbesparingar

- kostnadseffektiv

- Motverka

- kritisk

- kund

- Kunder

- kundanpassad

- Datum

- dedicerad

- djup

- leverera

- Efterfrågan

- krävande

- densitet

- Härledd

- Designa

- designsystem

- konstruktörer

- detaljerad

- Utveckling

- anordning

- enheter

- olika

- rikta

- ner

- chaufförer

- dynamisk

- e

- lätt

- kant

- Effektiv

- Elektronisk

- möjliggör

- Teknik

- etc

- Europa

- exekvera

- expanderade

- förväntar

- förlänga

- sträcker

- faktor

- SNABB

- Funktioner

- färre

- Blixt

- flexibel

- För

- formen

- Lyckligtvis

- från

- främre

- fungera

- genereras

- Mål

- Går

- Gold

- grov

- Väx

- Odling

- Hälften

- Arbetsmiljö

- Har

- Hög

- hög kvalitet

- högre

- höggradigt

- http

- HTTPS

- idealisk

- in

- innefattar

- inkorporerar

- ökande

- oberoende

- indien

- industrin

- Infineon

- integrera

- integrering

- intellektuella

- Gränssnitt

- inre

- invändigt

- Internet

- sakernas Internet

- Intervju

- in

- uppfann

- iot

- IP

- Israel

- IT

- DESS

- sig

- Nyckel

- lanserar

- ledare

- LÄRA SIG

- Lets

- Nivå

- Hävstång

- livet

- tycka om

- linje

- rader

- Lista

- belägen

- Lång

- Lot

- Låg

- Framställning

- hantera

- Tillverkare

- många

- marknad

- Marknadsledare

- Marknader

- Massa

- max-bredd

- Minnen

- Minne

- nämnts

- mikron

- Mode

- modeller

- lägen

- mer

- Behöver

- Nya

- of

- erbjudanden

- erbjuda

- kontor

- on

- ONE

- drift

- Alternativet

- or

- Övrigt

- över

- sida

- betalas

- Partnerskap

- partnerskap

- utföra

- prestanda

- PHP

- Plattformar

- plato

- Platon Data Intelligence

- PlatonData

- spelat

- portfölj

- placerad

- Inlägg

- kraft

- Närvaron

- process

- Produkt

- Produktion

- Produkter

- egenskaper

- ge

- ger

- tillhandahålla

- Tryckande

- RAM

- slumpmässig

- Läsa

- senaste

- nyligen

- Representanter

- Krav

- resultera

- Rise

- Roll

- Rullad

- försäljning

- Besparingar

- segment

- halvledare

- seriell

- Tjänster

- Dela

- skeppas

- visa

- signaler

- signifikant

- Kisel

- liknande

- smarta

- So

- Lösningar

- Källa

- specialiserat

- fart

- hastigheter

- sponsra

- standard

- igång

- Strategisk

- Strategi

- stark

- struktur

- sådana

- Summit

- leverantörer

- stödja

- Stödjande

- Stöder

- system

- System

- Ta

- Teknologi

- än

- den där

- Smakämnen

- deras

- Där.

- Dessa

- saker

- detta

- de

- Genom

- tid

- till

- i dag

- enorm

- Typ

- typer

- us

- användning

- användarfall

- validerade

- Värdefulla

- värde

- mängd

- olika

- Verifiering

- mycket

- via

- Besök

- flyktiga

- väntar

- vill

- var

- we

- wearable

- wearable teknik

- användbara

- były

- när

- som

- medan

- kommer

- med

- inom

- världen

- inom hela sverige

- år

- zephyrnet