Den gamla frasen att botemedlet är värre än sjukdomen är apropos när man diskuterar MBIST för stora SOC:er där körning av många MBIST-tester parallellt kan överskrida kapaciteten för kraftdistributionsnätverket (PDN). Memory Built-In Self-Test (MBIST) körs vanligtvis automatiskt under påslagningshändelser. På grund av önskan att snabba upp test- och chipstarttiderna, körs dessa tester ofta parallellt. Problemet är att de lätt kan producera växlingsaktivitet som är en storleksordning över de nivåer som finns under vanlig chipdrift. Faktum är att dessa högre växlingsaktivitetsnivåer inte bara kan orsaka sjunkande utbud som påverkar testresultaten, utan även den höga värme som genereras kan skada chips. Dessa effekter kan leda till felaktig binning eller direkta och latenta händelser.

Lösningen är att simulera MBIST-aktivitet för att förutsäga belastningen på PDN och de relaterade termiska effekterna. Med simuleringsresultat i hand kan konstruktörer korrekt bestämma hur många och vilka minnesblock som kan testas parallellt. Detta är dock inte alltid möjligt i stora SOC:er med många minnesblock eftersom simuleringstiderna kan vara oöverkomliga. Med grindnivå och ännu mindre exakt RTL-simulering är det kanske inte möjligt att köra tillräckligt många cykler för att få den information som behövs.

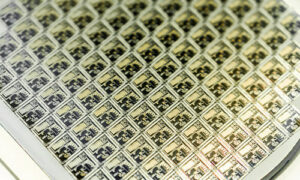

I en vitbok med titeln "Analyzing the power implikations of MBIST use" tittar Siemens EDA på hur designers kan köra tillräcklig simulering för att fatta välgrundade beslut om teststrategin innan bandet tas ut. Siemens arbetade med ARM på ett av deras testchips för att skapa ett testfall där de kunde tillämpa hårdvaruemulering med DFT- och Power-apparna för Siemens hårdvaruemulator Veloce. För det första används Veloce DFT-appen för att mata ut den interna aktiviteten under MBIST-emulering. Appen använder Standard Test Interface Language (STIL) och producerar industristandardutdatafiler.

Veloce Power-appen tar aktivitetsinformationen från MBIST-körningarna för att generera vågformer, effektprofiler och värmekartor som kan indikera när det finns effektspikar över angivna gränser. Med denna information kan testingenjörer fatta välgrundade beslut om sekvenseringen av MBIST.

ARM-testfallet som beskrivs i Siemens vitbok innehåller 176 miljoner grindar. Siemens använde ett Veloce-system med 6 Veloce Strato-brädor för detta testfall. Veloce-emulatorn tog bara 26 timmar, vilket är 15,600 XNUMX gånger snabbare än gatenivåsimulering. En annan fördel med Veloce-flödet är att aktivitetsinformationen strömmas av Power-appen till elverktygen i flödet, vilket sparar diskutrymme och tid. Resultaten från testfallet visade flera kraftspikar som bröt mot SOC-designspecifikationerna. Utdata från Veloce Power-appen visar de totala effektnivåerna genom simuleringen tillsammans med de separata effektbidragen för klockan, kombinationslogik och minne. Likaså finns det information om var på tärningen strömmen används. Denna information gör det enkelt att avgöra var det finns problem.

Att hitta sådana problem kräver att man kör miljontals eller miljarder klockcykler. Begränsningarna för mjukvarusimulatorer gör det oöverkomligt att utföra nödvändig analys. Emulering erbjuder en unik möjlighet att noggrant undersöka effekteffekterna av MBIST och andra testoperationer långt före kisel. Siemens vitbok ger insikt i kraftmetoden som används i ett riktigt testfall. Vitboken finns att ladda ner för läsning på Siemens hemsida.

Dela det här inlägget via: Källa: https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- Om oss

- analys

- app

- appar

- ARM

- tillgänglig

- Där vi får lov att vara utan att konstant prestera,

- Orsak

- chip

- Pommes frites

- klocka

- innehåller

- kunde

- härdning

- Designa

- Sjukdom

- under

- lätt

- Ingenjörer

- händelse

- händelser

- snabbare

- Förnamn

- flöda

- hittade

- grindar

- generera

- hårdvara

- Hög

- Hur ser din drömresa ut

- HTTPS

- industrin

- informationen

- IT

- språk

- Large

- leda

- Nivå

- nivåer

- läsa in

- Lång

- kartor

- miljon

- miljoner

- behövs

- nät

- Erbjudanden

- Verksamhet

- beställa

- Övriga

- Papper

- kraft

- Problem

- Profiler

- Läsning

- Resultat

- Körning

- rinnande

- sparande

- siemens

- simulering

- Mjukvara

- Utrymme

- fart

- Strategi

- strömmas

- leverera

- system

- testa

- Testning

- tester

- termisk

- Genom

- tid

- verktyg

- unika

- vanligen

- Webbplats

- vitt papper

- arbetade