Två nyare mjukvarubaserade algoritmiska teknologier – autonom körning (ADAS/AD) och generativ AI (GenAI) – håller halvledartekniker uppe på natten.

Medan ADAS på nivå 2 och nivå 3 är på rätt spår, är AD på nivå 4 och 5 långt ifrån verkligheten, vilket orsakar en minskning av riskkapitalentusiasm och pengar. Idag får GenAI uppmärksamheten och VC:er investerar ivrigt miljarder dollar.

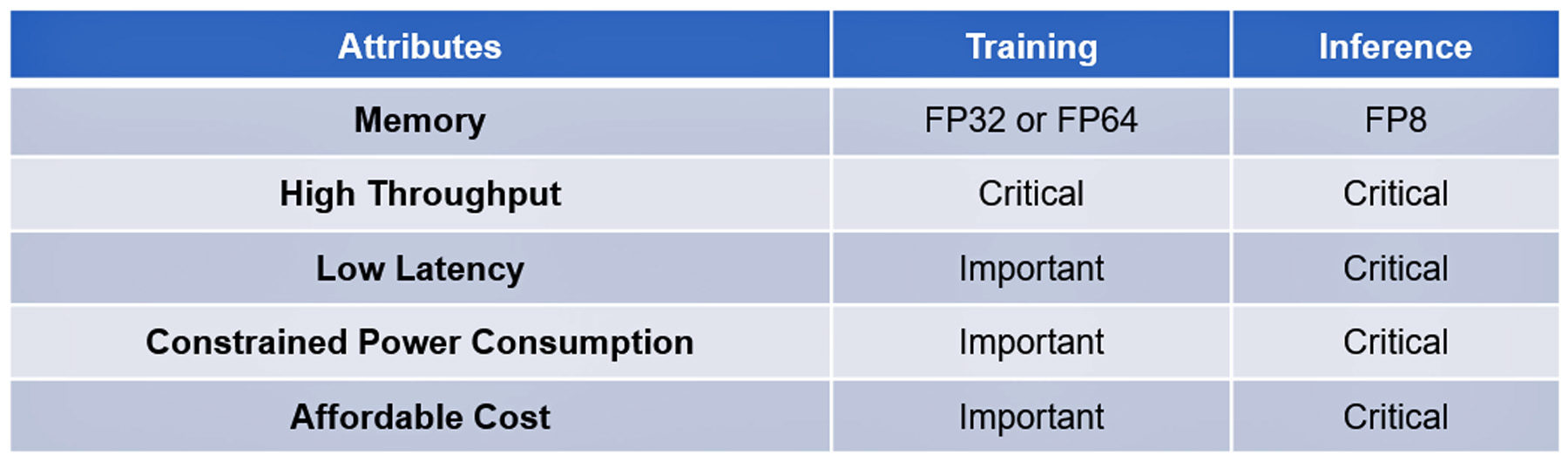

Båda teknologierna är baserade på moderna, komplexa algoritmer. Bearbetningen av deras träning och slutsatser delar några attribut, några kritiska, andra viktiga men inte väsentliga: Se tabell I.

De anmärkningsvärda mjukvaruframstegen inom dessa teknologier har hittills inte replikerats av framsteg inom algoritmisk hårdvara för att påskynda deras exekvering. Till exempel har toppmoderna algoritmiska processorer inte prestanda att svara på ChatGPT-4-förfrågningar på en eller två sekunder till en kostnad av ¢2 per fråga, det riktmärke som fastställts av Google-sökning, eller att bearbeta den massiva data samlas in av AD-sensorerna på mindre än 20 millisekunder.

Det är tills franska startupen VSORA investerade hjärnkraft för att ta itu med minnesflaskhalsen som kallas minnesväggen.

Minnesväggen

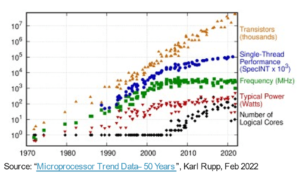

CPU:ns minnesvägg beskrevs först av Wulf och McKee 1994. Ända sedan dess har minnesåtkomst blivit flaskhalsen för datorprestanda. Framsteg i processorprestanda har inte speglats i minnesåtkomstförloppet, vilket får processorer att vänta längre på data som levereras av minnen. I slutet sjunker processoreffektiviteten långt under 100 % utnyttjande.

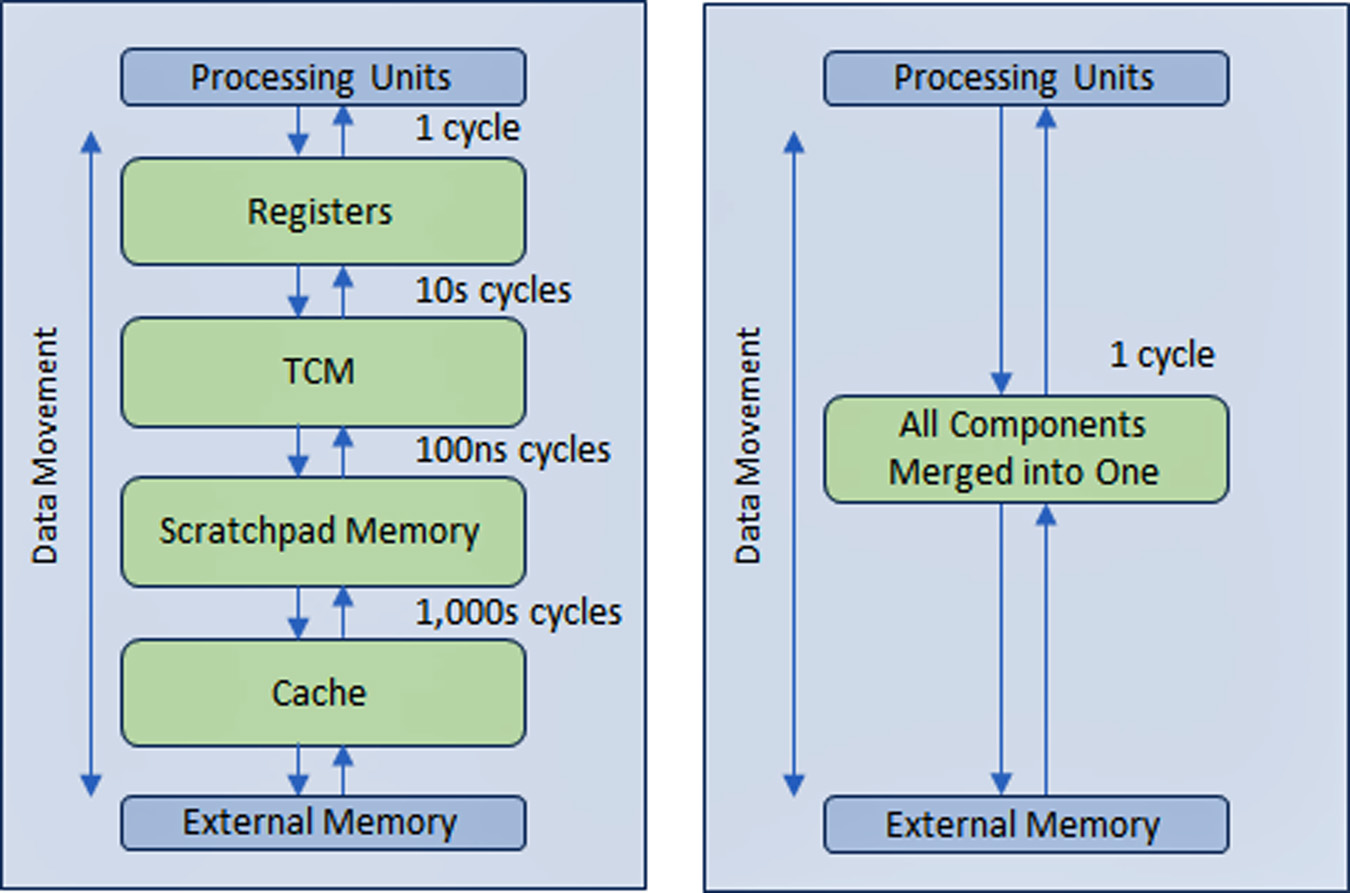

För att lösa problemet skapade halvledarindustrin en hierarkisk minnesstruktur på flera nivåer med flera nivåer av cache närmare processorn som minskar mängden trafik med de långsammare huvud- och externa minnena.

Prestanda hos AD- och GenAI-processorer beror mer än andra typer av datorenheter på bred minnesbandbredd.

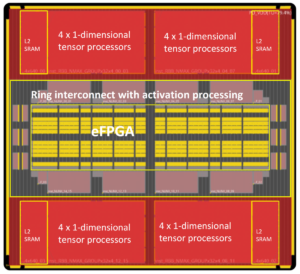

VSORA, som grundades 2015 för att rikta in sig på 5G-applikationer, uppfann en patenterad arkitektur som kollapsar den hierarkiska minnesstrukturen till ett tätt kopplat minne med stor bandbredd (TCM) som nås i en klockcykel.

Ur processorkärnornas perspektiv ser och fungerar TCM som ett hav av register i mängden MByte kontra kByte av faktiska fysiska register. Möjligheten att komma åt valfri minnescell i TMC i en cykel ger hög exekveringshastighet, låg latens och låg strömförbrukning. Det kräver också mindre kiselyta. Att ladda ny data från externt minne till TCM medan nuvarande data bearbetas påverkar inte systemets genomströmning. I grund och botten tillåter arkitekturen 80+% utnyttjande av bearbetningsenheterna genom sin design. Ändå finns det en möjlighet att lägga till cache och scratchpad-minne om en systemdesigner så önskar. Se figur 1.

Genom en registerliknande minnesstruktur implementerad i praktiskt taget alla minnen över alla applikationer kan fördelen med VSORA-minnesmetoden inte överskattas. Vanligtvis levererar banbrytande GenAI-processorer ensiffrig procentuell effektivitet. Till exempel ger en GenAI-processor med en nominell genomströmning på en Petaflops med nominell prestanda men mindre än 5 % effektivitet användbar prestanda på mindre än 50 Teraflops. Istället uppnår VSORA-arkitekturen mer än 10 gånger högre effektivitet.

VSORAS algoritmiska acceleratorer

VSORA introducerade två klasser av algoritmiska acceleratorer – Tyr-familjen för AD-tillämpningar och Jotunn-familjen för GenAI-acceleration. Båda levererar fantastisk genomströmning, minimal latens, låg strömförbrukning i ett litet kiselfotavtryck.

Med nominell prestanda på upp till tre Petaflops har de en typisk implementeringseffektivitet på 50-80 % oavsett algoritmtyp och en toppströmförbrukning på 30 Watt/Petaflops. Dessa är fantastiska attribut som inte rapporterats av någon konkurrerande AI-accelerator ännu.

Tyr och Jotunn är fullt programmerbara och integrerar AI- och DSP-funktioner, om än i olika mängder, och stöder val av aritmetik från 8-bitars till 64-bitars antingen heltals- eller flyttalsbaserade. Deras programmerbarhet rymmer ett universum av algoritmer, vilket gör dem algoritmagnostiska. Flera olika typer av gleshet stöds också.

VSORA-processorers egenskaper driver dem till fronten i det konkurrenskraftiga algoritmiska bearbetningslandskapet.

Stödprogram för VSORA

VSORA designade en unik kompilerings-/valideringsplattform skräddarsydd för dess hårdvaruarkitektur för att säkerställa att dess komplexa, högpresterande SoC-enheter har gott om mjukvarustöd.

En rad hierarkiska verifierings-/valideringsnivåer – ESL, hybrid, RTL och gate – – avsedd att placera den algoritmiska designern i cockpiten – levererar tryckknappsfeedback till algoritmingenjören som svar på designutforskningar av rymden. Detta hjälper honom eller henne att välja den bästa kompromissen mellan prestanda, latens, kraft och område. Programmeringskod skriven på en hög abstraktionsnivå kan mappas inriktad på olika bearbetningskärnor transparent för användaren.

Gränssnitt mellan kärnor kan implementeras inom samma kisel, mellan chips på samma PCB eller via en IP-anslutning. Synkronisering mellan kärnor hanteras automatiskt vid kompileringstidpunkten och kräver inte programvara i realtid.

Vägspärr till L4/L5 Autonom Driving och Generative AI Inference at the Edge

En framgångsrik lösning bör även innefatta programmerbarhet på fältet. Algoritmer utvecklas snabbt, drivna av nya idéer som föråldras över en natt av gårdagens toppmoderna. Möjligheten att uppgradera en algoritm i fält är en anmärkningsvärd fördel.

Medan företag i hyperskala har satt ihop enorma datorfarmar med mängder av sina processorer med högsta prestanda för att hantera avancerade mjukvarualgoritmer, är tillvägagångssättet bara praktiskt för träning, inte för att sluta sig till vid kanten.

Utbildning är vanligtvis baserad på 32-bitars eller 64-bitars flyttalsaritmetik som genererar stora datamängder. Det kräver ingen sträng latens och tolererar hög strömförbrukning samt betydande kostnader.

Slutledning vid kanten utförs vanligtvis på 8-bitars flyttalsaritmetik som genererar något mindre mängder data, men kräver kompromisslös latens, låg energiförbrukning och låg kostnad.

Energiförbrukningens inverkan på latens och effektivitet

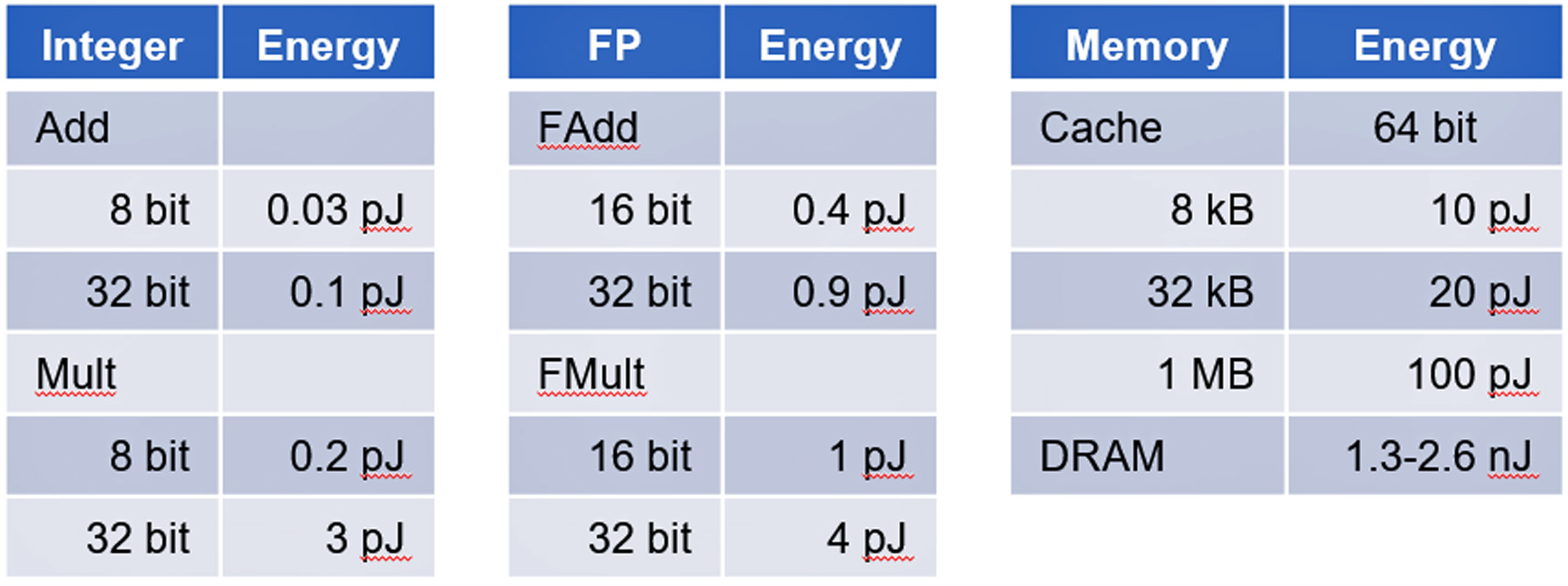

Strömförbrukningen i CMOS IC domineras av datarörelser inte databehandling.

En studie från Stanford University ledd av professor Mark Horowitz visade att strömförbrukningen för minnesåtkomst förbrukar storleksordningar mer energi än grundläggande digitala logiska beräkningar. Se tabell II.

AD- och GenAI-acceleratorer är utmärkta exempel på enheter som domineras av datarörelser och utgör en utmaning för att begränsa strömförbrukningen.

Slutsats

AD och GenAI slutledning utgör icke-triviala utmaningar för att uppnå framgångsrika implementeringar. VSORA kan leverera en heltäckande hårdvarulösning och stödjande mjukvara för att uppfylla alla kritiska krav för att hantera AD L4/L5 och GenAI som GPT-4-acceleration till kommersiellt lönsamma kostnader.

Mer information om VSORA och dess Tyr och Jotunn finns på www.vsora.com.

Om Lauro Rizzatti

Lauro Rizzatti är affärsrådgivare till VSORA, en innovativ startup som erbjuder IP-lösningar för kisel och kiselchips, och en känd verifieringskonsult och branschexpert på hårdvaruemulering. Tidigare har han haft befattningar inom management, produktmarknadsföring, teknisk marknadsföring och ingenjörskonst.

Läs också:

Soitec är Engineering the Future of the Semiconductor Industry

ISO 21434 för cybersäkerhetsmedveten SoC-utveckling

Förutsägande underhåll i samband med fordonsfunktionell säkerhet

Dela det här inlägget via:

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- PlatoData.Network Vertical Generative Ai. Styrka dig själv. Tillgång här.

- PlatoAiStream. Web3 Intelligence. Kunskap förstärkt. Tillgång här.

- Platoesg. Kol, CleanTech, Energi, Miljö, Sol, Avfallshantering. Tillgång här.

- PlatoHealth. Biotech och kliniska prövningar Intelligence. Tillgång här.

- Källa: https://semiwiki.com/automotive/336201-long-standing-roadblock-to-viable-l4-l5-autonomous-driving-and-generative-ai-inference-at-the-edge/

- : har

- :är

- :inte

- $UPP

- 000

- 1

- 10

- 1800

- 1994

- 20

- 30

- 50

- 5G

- a

- förmåga

- Om oss

- abstraktion

- accelerera

- acceleration

- accelerator

- acceleratorer

- tillgång

- Accessed

- åtkomst

- Uppnå

- uppnår

- tvärs

- handlingar

- faktiska

- Ad

- ADA:er

- lägga till

- adress

- avancerat

- framsteg

- Fördel

- rådgivare

- påverka

- AI

- algoritm

- algoritmisk

- algoritmer

- Alla

- tillåter

- också

- mängd

- mängder

- an

- och

- svara

- vilken som helst

- tillämpningar

- tillvägagångssätt

- arkitektur

- ÄR

- OMRÅDE

- Konst

- AS

- At

- uppmärksamhet

- attribut

- automatiskt

- fordonsindustrin

- autonom

- Bandbredd

- baserat

- grundläggande

- I grund och botten

- BE

- blir

- varit

- nedan

- riktmärke

- BÄST

- mellan

- miljarder

- båda

- företag

- men

- by

- cache

- KAN

- kan inte

- kapacitet

- kapital

- orsakar

- cellen

- utmanar

- utmaningar

- Pommes frites

- klasser

- klocka

- Sittbrunnen

- koda

- faller ihop

- kommersiellt

- samfundet

- Företag

- konkurrenskraftig

- komplex

- komplicerad

- omfattande

- kompromiss

- beräkningar

- Compute

- databehandling

- anslutning

- konsult

- konsumtion

- innehålla

- sammanhang

- Pris

- Kostar

- kopplad

- CPU

- skapas

- kritisk

- Aktuella

- allra senaste

- cykel

- datum

- databehandling

- leverera

- levereras

- levererar

- tät

- beror

- beskriven

- Designa

- utformade

- designer

- detaljer

- enheter

- olika

- digital

- siffror

- do

- gör

- dollar

- driven

- drivande

- Drop

- Droppar

- ivrigt

- kant

- effektivitet

- antingen

- änden

- energi

- Energiförbrukning

- ingenjör

- Teknik

- säkerställa

- entusiasm

- ESL

- väsentlig

- etablerade

- NÅGONSIN

- utvecklas

- exempel

- exempel

- utförande

- expert

- extern

- familj

- långt

- gårdar

- återkoppling

- få

- fält

- Figur

- Förnamn

- flytande

- Fotavtryck

- För

- förgrunden

- hittade

- Grundad

- franska

- från

- fullständigt

- funktionella

- framtida

- genererar

- generativ

- Generativ AI

- Google Sök

- större

- hantera

- hårdvara

- Har

- he

- Held

- hjälper

- här

- Hög

- högpresterande

- högsta

- honom

- Horowitz

- http

- HTTPS

- stor

- Hybrid

- i

- ICS

- idéer

- if

- ii

- genomförande

- implementeringar

- genomföras

- med Esport

- ålagts

- in

- innefattar

- industrin

- Branschexpert

- innovativa

- exempel

- istället

- integrera

- in

- introducerade

- uppfann

- Invest

- investerat

- IP

- IT

- DESS

- jpg

- hopp

- hålla

- känd

- liggande

- Large

- Latens

- Led

- mindre

- Nivå

- nivåer

- tycka om

- läser in

- Logiken

- långvarig

- längre

- UTSEENDE

- Låg

- Huvudsida

- underhåll

- Framställning

- förvaltade

- ledning

- mandat

- markera

- Marknadsföring

- massiv

- max-bredd

- Möt

- Minnen

- Minne

- millisekunder

- minimum

- Modern Konst

- pengar

- mer

- rörelse

- multipel

- folkmassor

- Nya

- natt

- noterade

- anmärkningsvärd

- nu

- föråldrad

- of

- erbjuda

- on

- ONE

- endast

- Verksamhet

- or

- beställa

- ordrar

- Övriga

- Övrigt

- över

- natten

- överskattas

- patenterad

- Topp

- för

- procentuell

- prestanda

- utfört

- perspektiv

- fysisk

- plattform

- plato

- Platon Data Intelligence

- PlatonData

- Massor

- Punkt

- positioner

- Möjligheten

- Inlägg

- kraft

- Praktisk

- tidigare

- Prime

- Problem

- process

- bearbetade

- bearbetning

- Processorn

- processorer

- Produkt

- Professor

- programmerbar

- Programmering

- Framsteg

- Driva fram

- sätta

- sökfrågor

- område

- snabbt

- Läsa

- realtid

- Verkligheten

- senaste

- minskar

- Oavsett

- register

- anmärkningsvärd

- replikeras

- Rapporterad

- kräver

- Krav

- Kräver

- respons

- Samma

- HAV

- Sök

- sekunder

- se

- Val

- halvledare

- sensor

- flera

- Dela

- aktier

- skall

- visade

- Kisel

- eftersom

- enda

- Small

- So

- Mjukvara

- lösning

- Lösningar

- LÖSA

- några

- något

- Källa

- Utrymme

- fart

- spent

- stanford

- Stanford University

- start

- Ange

- state-of-the-art

- Stjärn

- Fortfarande

- strömlinjeformad

- stränga

- struktur

- Läsa på

- väsentlig

- framgångsrik

- stödja

- Som stöds

- Stödjande

- synkronisering

- system

- bord

- skräddarsydd

- Målet

- targeting

- Teknisk

- Tekniken

- än

- den där

- Smakämnen

- Framtiden

- deras

- Dem

- Där.

- Dessa

- de

- detta

- tre

- Genom

- genomströmning

- tätt

- tid

- gånger

- till

- i dag

- spår

- traditionell

- trafik

- Utbildning

- transparent

- två

- Typ

- typer

- typisk

- typiskt

- unika

- enheter

- Universum

- universitet

- tills

- uppgradera

- användbar

- Användare

- med hjälp av

- VC

- våga

- riskkapital

- Verifiering

- Kontra

- via

- genomförbar, livskraftig

- praktiskt taget

- volymer

- vänta

- Vägg

- var

- Sätt..

- VÄL

- när

- medan

- bred

- önskemål

- med

- inom

- skriven

- ännu

- utbyten

- zephyrnet