Plasmaetsning är kanske den mest väsentliga processen vid halvledartillverkning, och möjligen den mest komplexa av alla fab-operationer vid sidan av fotolitografi. Nästan hälften av alla fantastiska steg är beroende av en plasma, en energisk joniserad gas, för att göra sitt jobb.

Trots ständigt krympande transistor- och minnesceller fortsätter ingenjörer att leverera tillförlitliga etsningsprocesser.

"För att på ett hållbart sätt skapa chips med precision på nanoskalanivå och rätt kostnadsstruktur måste tillverkare av waferfab-utrustning tänja på gränserna för plasmafysik, materialteknik och datavetenskap för att leverera de utrustningslösningar som behövs", säger Thomas Bondur, företagsdirektör för Etch Produktgruppsmarknadsföring på Lam Research. Ingenstans är detta mer uppenbart än i plasmaetsning, som arbetar hand i hand med litografi för att skapa exakta, repeterbara egenskaper på wafers.

Den här rapporten undersöker viktiga etsningssteg i 3D NAND, DRAM, nanosheet-FET och sammankopplingar, med en framåtblick på 2D-enheter och lågbudget-backend-bearbetning. Industrin strävar också efter mer hållbar etsningskemi för att minska motsvarande CO2 utsläpp från dess fabriker.

För många verktygstillverkare spelar processmodellering en avgörande roll i utvecklingen av etsningsprocesser. Målet är att förkorta tiden till marknaden samtidigt som kostnaderna för wafer och mask minskar.

"Optimering av etsningsprocesser på några av de svåraste stegen kan ta ett år eller mer att slutföra", säger Barrett Finch, senior marknadschef på Lam Research. "Vi slutförde nyligen en del processimuleringsarbete på tre veckor som förväntades ta tre månader med typiska kiselbaserade tester och utvecklingar."

Detta kan uppgå till hundratusentals, eller till och med miljontals dollar, bara för mask- och waferkostnaderna för en enhetstillverkare.

Grunderna för etsning

Etsningsprocessen arbetar hand i hand med litografi. Etsning föregås typiskt av avsättning av en film (genom epitaxi, kemisk eller fysikalisk ångavsättning, etc.). Vanligtvis, a CVD filmen är belagd med fotoresist och exponeras sedan genom ett mönstrat hårkors (mask) med hjälp av optisk litografi (248nm eller 193nm UV, 13.5nm EUV). Motstå utveckling avslöjar sedan mönstret. I en plasmaetsningskammare med enstaka skivor bombarderar typiskt etsningskemikalierna och jonerna och tar bort CVD-filmen där fotoresisten saknas (i positiv tonresist). Efter etsning, motstå askning, våtkemisk rengöring och/eller våtetsning avlägsna rester.

Plasmaetsningsprocesser kan grovt grupperas som dielektriska etsar, kisel eller ledare. Dielektrika som kiseldioxid och kiselnitrid etsas bäst med fluorerade gaser medan kisel- och metallskikt reagerar bäst med klorkemi. Det finns i huvudsak tre torretsningslägen - reaktiv jonetsning, plasmaetsning och sputteretsning (jonstråle). Etsningsprocesser handlar om de komplexa interaktionerna mellan de kemiska reaktanterna, plasma och wafermaterial. När RF-bias appliceras på en reaktiv gas bombarderar elektroner och positivt laddade joner skivan för att fysiskt avlägsna (etsa) material medan de kemiska arterna och fria radikalerna reagerar med det exponerade materialet för att bilda flyktiga biprodukter. Etsning kan vara antingen isotropisk (reagerar lika vertikalt och horisontellt), anisotropisk (endast vertikalt) eller någonstans däremellan.

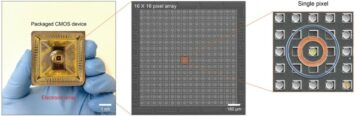

Fig. 1: Övergång från finFET till GAA driver kritiska isotropiska selektiva etsningskrav. Källa: Lam Research

De mått som etsingenjörer bryr sig mest om är etsningshastighet, profilkontroll, enhetlighet (över skivan) och etsningsselektivitet, eftersom dessa påverkar utbyte och produktivitet. Etsningsselektivitet är helt enkelt förhållandet mellan borttagning av materialet du vill etsa i förhållande till dess underskikt – till exempel SiO2 på kisel. Under etsning är det också fördelaktigt att inte ta bort för mycket fotoresist. Men när så är fallet överförs ofta mönstret till en hård mask (kiseldioxid, kiselnitrid, SiOC, TiN) innan det överförs till den underliggande filmen.

Selektivitetsspecifikationerna varierar från 2:1 till upp till 1,000 1:30 (mycket selektiv etsning). För varje ny nod blir dessa specifikationer stramare. "Med hög NA EUV som börjar ersätta vanlig EUV inom de kommande fyra åren, är fokus mycket lägre, så du kan inte längre exponera tjock fotoresist - och med tjock menar jag 2 nanometer", säger Philippe Bézard, torretsning FoU-ingenjör på imec. "Men du måste fortfarande mönstra samma filmtjocklek nedan. Så nu ber du om mycket högre selektivitet i den meningen att vi istället för 1:10 måste nå mer som 1:4, vilket är en plötslig 5X till XNUMXX selektivitetsförbättring."

Från proof of concept (POC) till högvolymtillverkning (HVM)

Bézard beskriver tre faser av etsprocessutveckling:

- Att bestämma vilken etsare, gaser, hjälplager etc. som behövs för att utföra etsningen;

- Demonstrerar prestanda för att helt ta bort film inom specifikationerna med processuniformighet över en wafer, och

- Bestämma hur processen kan upprepas över tusentals skivor i HVM med högt utbyte och liten drift.

Vanligtvis hanterar skickliga ets- och integrationsingenjörer de två första utvecklingsfaserna. Den tredje fasen kan återigen utnyttja ingenjörsexpertis, men maskininlärning kan hjälpa.

"Maskininlärning och dataanalys i allmänhet är bara användbar i den tredje fasen," sa han. "Den är väldigt kraftfull eftersom den har tillgång till massor av data och kan betyda en miljon små, enkla saker som alla interagerar. Så för en mänsklig hjärna att försöka ta reda på detta är mycket svårt, men det är mer hanterbart för ett datorprogram. Men i fall där du har en ny applikation, nytt material etsas eller en ny integration, visar det ingen förbättring jämfört med människor.”

ML-användning hänför sig också till tillverkningskostnad eftersom tusentals wafers används i fas tre - åtminstone en storleksordning större än vad som används i fas ett och två.

Barrett Finch, senior director för Etch Product Group på Lam Research, beskriver ny processväg som att ta ett proof-of-concept från ett nominellt processflöde och layout och utveckla en eller flera fungerande enheter på en wafer. Denna POC överförs sedan till ett produktutvecklingsteam i fabriken för att skala upp processen och förbättra avkastningen.

"Mängden arbete som krävs för att omvandla ett nominellt proof-of-concept till en livskraftig produkt som ger resultat är ofta underskattad, och detta skapar ett stort gap till lönsamhet," sa Finch. "Processfönstermodellering strävar efter att överbrygga denna lucka genom att introducera fantastisk variation i de tidiga stadierna av forskning och utveckling." Han föreslår att virtuella DOE och Monte Carlo-baserad analys över ett antal processparametrar testar en POC genom att simulera förväntad variabilitet.

"Processfönstermodellering kan svara på frågan "Vilken CD eller nivå av variation måste jag upprätthålla för att nå lägsta enhetsprestanda och -kapacitet?" Vi har slutfört virtuella processfönstertester med uppemot 1 miljon virtuella wafers på några dagar, vilket skulle vara omöjligt att genomföra i verkligheten”, sa han.

Flera parametrar påverkar etsningshastighet, profil och selektivitet. En nyckel är temperaturen. "Inverkan av termiska effekter i etsningsbearbetning ses av våra kunder när de kontrollerar etshastigheter, selektiviteter och etsade profiler. Alla dessa parametrar kan påverka både enhetsutbyte och fantastisk produktivitet, säger Benjamin Vincent, senior manager för halvledarprocess och integrationsteknik på Lam Research. Han hävdar att simulering kan vara särskilt användbart när ett processsteg har flera möjliga konfigurationer (processutrymmet är stort), eller där nedströmsresultaten från steget är mycket oförutsägbara.

"Etsprocessen är beroende av skivans yttemperatur, som beror på flera värmeflöden - inklusive värmeledning, jonpåverkansenergier, ytreaktioner och plasmastrålningsvärmeflöden", säger Alex Guermouche, produktmarknadschef på Esgee Technologies, en Lam Research Company. "Som ett resultat måste plasmamodeller införliva alla dessa fysikfunktioner för att exakt avbilda temperaturförändringar på skivans yta. Processimuleringsmjukvara kan modellera en rad etsningsattribut, vilket gör att vi kan få ett bättre etsningsresultat snabbare och accelerera kundens förmåga att öka produktionen eller optimera avkastningen."

Exakt tidpunkt för etsningsprocessen

Med snävare geometrier och tunnare filmer finns det ett behov av att balansera etshastigheten med stor kontroll över andra driftsparametrar.

"Med krympande designregler går många etsningsprocesser till mycket snabba plasmaetsningsprocesssteg som kräver mycket exakt kontroll av alla reaktionsingångar: effekt, tryck, kemi och temperatur," sa Finch och noterade att det också finns en trend mot optimerad plasma pulserande beteende för att generera ett speciellt jon-till-neutralt förhållande och sedan sopa bort biprodukter. "Avancerad modellering av sådana förhållanden kommer att vara avgörande för att möjliggöra ytterligare enhetsskalning."

Tillverkare av etsningssystem har använt modelleringsprogram under en tid för att påskynda utvecklingen av nästa nod eller ramputbyten. Detta är ingen överraskning, med tanke på den stora komplexiteten i processen och alla dess variabler.

"Det finns helt enkelt inte tillräckligt med tid eller tillräckligt med wafers för att utföra alla möjliga processexperiment när man utvecklar nästa nod-teknik," sa Finch. "Antalet kombinationer av etsutrustningsinställning kan uppgå till miljontals, eller till och med miljarder, och utveckling av brute force wafer med alla processmöjligheter är helt enkelt omöjligt."

Naturligtvis är alla bra modeller verifierade på faktiska marker. "En korrekt modell bör vara förutsägande, och den bör lösa det målinriktade problemet som en användare vill lösa," sa Finch. "Varje gång en process eller designändring har rekommenderats baserat på simuleringsarbete, bör faktiska fab-data återspegla resultaten av rekommendationen. I vårt fall har vi kunnat förutsäga effekten av processförändringar med modellbaserade resultat och snabbt lösa svåra process- och teknikutvecklingsproblem.”

Verktygsleverantörer arbetar också med avancerade etsningsprocesser för att närmare integrera linjer och omvandla det som en gång var en process på två masknivåer (två litografisteg) till en för processförenkling och kostnadsreduktion.

"Istället för att anpassa befintlig hårdvara för att göra den schweiziska armékniven ännu mer utrustad, introducerar företag teknologier som är applikationsspecifika, till exempel nya system för att lösa tip-to-tip-problem", säger Bézard. Syftet är att göra två linjer mot varandra närmare varandra, vilket för närvarande innebär ett linjemönstersteg följt av en skärmask. "Vad Applied Materials och andra introducerar är ett sätt att direkt etsa i horisontell riktning." Sådana processer kan också vidgas via hål.

Etsningssteg för nanosheet-FET:er

Den mest kritiska etsningen kliver in nanoark processflöden inkluderar dummy gate-etsningen, anisotropisk pelaretsning, isotropisk distansetsning och kanalfrigöringssteget. [1] Profilen etsar genom alternerande lager av kisel och SiGe är anisotropisk och använder fluorerad kemi. Den inre distansens etsning (intryckning) och kanalfrigöringssteget är optimerade för att ta bort SiGe med extremt låg kiselförlust.

Kanalsläppningssteget är kritiskt. "Släppningen av nanoarket kräver extremt hög selektivitet," sa Bézard. "De flesta nanoark är kisel, sedan kisel-germanium och kisel. Du har omväxlande lager, och du måste ta bort det ena utan att modifiera det andra alls." Vissa publikationer har diskuterat att utföra en flerstegs SiGe-etsning för att reducera spänningen på strukturen som induceras av ett enda etsningssteg.

Nästa i processen är bildandet av självjusterade kontakter. "Här är det vi försöker göra i princip att etsa kiseldioxid och inte röra eller försänka kiselnitriden. Nuvarande specifikationer är, låt oss säga, 3nm fördjupning, men folk begär noll förlust, säger Bézard. "I det här fallet använder vi inte ens ordet selektivitet. Vi pratar bara om rast – och noll rast vid det.

3D NAND

För 3D NAND flash fortsätter antalet lager att växa och kräver användning av flera staplade nivåer i framtiden, vilket så småningom skapar vertikala strängar av staplade enheter. "Det finns också en hel del driv att skala ordlinjestigningen eller vertikal/Z-pitch för lagren när antalet lager växer för att fortsätta öka bittätheten", säger Robert Clark, senior medlem av teknisk personal och teknikchef på TEL. "Ur ett processperspektiv kommer etsnings- och deponeringsprocesser att behöva ständiga förbättringar för att tillgodose de allt högre bildförhållandena vid allt mindre kritiska dimensioner som fortsatt skalning kräver."

Clark beskrev framtida förändringar. "När man ser på avancerade noder av laddningsfällande enheter med flera nivåer, kommer konstruktion av grindstackarna att krävas för att uppnå kortare grindlängder, fler nivåer per cell och förbättrad programmeringseffektivitet - potentiellt genom att använda högk-material. Högre konduktivitetskanaler kommer sannolikt att krävas för att ersätta poly-Si-kanaler i framtiden, säger han.

En av de mest kritiska etsningarna i 3D NAND involverar djupetsning av cirka 100 nm hål genom flerskiktsoxid-nitridstaplar (200+ lager), som kan vara upp till 10 µm djupa. Imecs Bézard sa att detta etsningssteg är särskilt dyrt.

"Vi har ett fysiskt fenomen som uppstår, som kallas differentiell laddningseffekt," sa han. "I plasman har vi elektroner, joner och neutrala arter för att förenkla mycket. Elektroner rör sig i alla riktningar, men joner accelereras vinkelrätt mot ytan. Så du har positiv laddning längst ner i hålet och negativ laddning överst, och du får ett elektriskt fält som försöker stöta bort inkommande joner."

Som ett resultat krävs höga effektnivåer för att helt etsa diket. "Vi försöker upprätthålla 30 till 50 gigawatt effekt utan ljusbågsbildning, och därför måste chucken vara extremt välpolerad och vältillverkad," sa han.

De djupa etsningarna inducerar också spänningar som måste minimeras, särskilt eftersom flerskiktad NAND-tillverkning därefter kräver skivförtunning, exakt inriktning och hybridbindning till nästa nivå.

Andra processer

Inte alla chiptillverkare producerar ledande chip som kräver EUV-litografi. Många fabs utökar sina 193nm lito- och etsningsprocesser.

"Vi har ett högtemperatur-SOC-material som vi nyligen har börjat introducera, som utökar dess mönstringsförmåga och som tål högre temperaturer, oavsett om det används som underlag för ett CVD-lager eller mask", säger Brian Wilbur, chef för halvledarprodukter diversifiering på Brewer Science.

BEOL förlängning för de tätaste metalllinjerna förväntas genomgå en dramatisk övergång från dubbla damascenintegreringsscheman till subtraktiv deponering och etsning av andra sammankopplingar än koppar. Här har två metaller - rutenium och molybden - varit de mest grundligt utvecklade. Det är dock mer sannolikt att molybden oxiderar under etsning, vilket gör det mer kompatibelt med dubbla damascener. Ruthenium är en ädelmetall så den har inte samma korrosionsproblem, men det är dyrare.

Enhetsstrukturer blir också intoleranta mot kantplaceringsfel. Nya system för självjustering från lager till lager och mellan vias och linjer kommer att behövas, enligt TEL:s Clark. "De första implementeringarna kommer sannolikt att vara för saker som nedgrävda ordlinjer i DRAM och de små MOL-metallskikten för logik där det finns behov av högre termisk stabilitet såväl som lägre resistivitet eller liner-lösa metaller."

Nästa generations utveckling

Långsiktigt kommer industrin idealiskt att gå över till back-end-processer med lägre termisk budget (närmare 300°C än 400°C) för att integrera enheter i back-end-interconnect-lager.

"Branschen har ett verkligt behov av att börja bygga enheter i fler lager", säger TEL:s Clark. "Det betyder att vi behöver minnes- och logikenheter byggda inom BEOL med BEOL termiska budgetar."

Hittills verkar enheter tillverkade med hjälp av halvledande oxider lovande, både för att integrera minnesenheter i ett logiskt BEOL-flöde eller för att bygga CMOS-arrayer ovanpå minnesarrayen i DRAM.

En annan betydande förändring involverar integrationen av 2D-material, som forskningshus och ledande chiptillverkare redan börjar testa. Etsningsprocesser för material som volframdisulfid eller molybdendisulfid övervägs. Filmerna består av ett monolager av material så att utveckla fantastiska processer för att integrera dem är extremt utmanande.

Hållbarhet

Flistillverkare och materialleverantörer strävar efter alternativa kemier för att minska koldioxidutsläppen. Inom etsning är de främsta bovarna fluorerade gaser med hög global uppvärmningspotential.

"En anledning till att du har PFOS (perfluoroktansulfonsyra), vilket är problematiskt, är för att molekylen är så stabil", säger imecs Bézard. "Ljus eller kemiska reaktioner i atmosfären är inte tillräckliga för att bryta ner den."

Han sa att ett antal alternativa gasblandningar med högre syrehalt är lättare att dissociera och har lägre GWP. "Men alla kandidater måste leverera lika bra eller till och med högre prestationer för att börja."

Men hållbarhet är inte särskilt en etsnings- eller deponeringsutmaning. Det är en holistisk industriutmaning från litografi till förpackning, där inverkan av ett nytt material påverkar hela enhetens bearbetning.

Hänvisning

1. K. Derbyshire, "Vad är annorlunda med nästa generations transistorer", Semiconductor Engineering, 20 oktober 2022.

Relaterade händelser

Mycket selektiv etsning rullar ut för nästa generations marker

Att tillverka 3D-strukturer kommer att kräva kontroll på atomnivå av vad som tas bort och vad som stannar på en wafer.

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- PlatoAiStream. Web3 Data Intelligence. Kunskap förstärkt. Tillgång här.

- Minting the Future med Adryenn Ashley. Tillgång här.

- Köp och sälj aktier i PRE-IPO-företag med PREIPO®. Tillgång här.

- Källa: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- : har

- :är

- :inte

- :var

- $UPP

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- 2D material

- 30

- 3d

- 50

- a

- förmåga

- Able

- Om oss

- accelerera

- accelererad

- tillgång

- rymma

- åstadkomma

- Enligt

- exakt

- exakt

- tvärs

- faktiska

- adress

- Antagande

- avancerat

- fördelaktig

- påverka

- igen

- Syftet

- alex

- Alla

- tillåta

- redan

- också

- alternativ

- mängd

- an

- analys

- och

- Annan

- svara

- vilken som helst

- visas

- Ansökan

- applikationsspecifik

- tillämpas

- ÄR

- Armé

- array

- AS

- aspekt

- bistå

- At

- Atmosfär

- attribut

- bort

- Back-end

- Balansera

- baserat

- I grund och botten

- BE

- Stråle

- därför att

- passande

- varit

- innan

- Börjar

- Där vi får lov att vara utan att konstant prestera,

- nedan

- Benjamin

- BÄST

- Bättre

- mellan

- förspänning

- Stor

- miljarder

- Bit

- båda

- Botten

- gränser

- Hjärna

- Ha sönder

- Brian

- brute force

- budget

- budgetar

- Byggnad

- byggt

- men

- by

- kallas

- KAN

- kandidat

- kol

- koldioxidutsläpp

- vilken

- Vid

- fall

- CD

- Celler

- utmanar

- utmanande

- Klimatkammare

- byta

- Förändringar

- Kanal

- kanaler

- laddning

- laddad

- avgifter

- laddning

- kemisk

- kemikalier

- kemi

- Pommes frites

- Rengöring

- Stänga

- nära

- närmare

- kombinationer

- Företag

- företag

- kompatibel

- fullborda

- Avslutade

- komplex

- Komplexiteten

- dator

- begrepp

- villkor

- konduktivitet

- dirigent

- anses

- konstant

- kontakter

- innehåll

- fortsätta

- fortsatte

- fortsätter

- kontroll

- Koppar

- Företag

- korrosion

- Pris

- kostnadsminskning

- Kostar

- kunde

- Naturligtvis

- skapa

- skapar

- Skapa

- kritisk

- Aktuella

- För närvarande

- Kunder

- Klipp

- datum

- dataanalys

- datavetenskap

- Dagar

- djup

- leverera

- densitet

- beror

- beskriven

- Designa

- utvecklade

- utveckla

- Utveckling

- anordning

- enheter

- olika

- svårt

- dimensioner

- riktning

- direkt

- Direktör

- diskuteras

- diversifiering

- do

- gör

- dollar

- ner

- dramatiskt

- driv

- torka

- under

- varje

- Tidig

- lätt

- effekt

- effekter

- effektivitet

- antingen

- elektriska

- elektroner

- utsläpp

- möjliggör

- ingenjör

- Teknik

- Ingenjörer

- tillräckligt

- lika

- Utrustning

- utrustad

- Motsvarande

- speciellt

- väsentlig

- väsentligen

- etc

- Även

- så småningom

- Varje

- krävande

- undersöker

- exekvera

- befintliga

- förväntat

- dyra

- experiment

- expertis

- utsatta

- sträcker

- extremt

- vänd

- långt

- SNABB

- snabbare

- Funktioner

- få

- fält

- Figur

- Film

- filmer

- Förnamn

- Blixt

- flöda

- flöden

- Fokus

- följt

- efter

- För

- kraft

- formen

- bildning

- Framåt

- fyra

- Fri

- från

- fullständigt

- ytterligare

- framtida

- spalt

- GAS

- Allmänt

- generera

- skaffa sig

- ges

- Välgörenhet

- den globala uppvärmningen

- Målet

- god

- stor

- Grupp

- Väx

- Växer

- Hälften

- hantera

- Hård

- hårdvara

- Har

- he

- hjälp

- här.

- Hög

- High Yield

- högre

- höggradigt

- Hål

- Hål

- helhetssyn

- Horisontell

- hus

- Hur ser din drömresa ut

- Men

- HTTPS

- humant

- Människa

- Hundratals

- Hybrid

- i

- Inverkan

- omöjligt

- förbättra

- förbättras

- förbättring

- in

- innefattar

- Inklusive

- Inkommande

- införliva

- ökande

- industrin

- ingångar

- exempel

- istället

- integrera

- Integrera

- integrering

- interagera

- interaktioner

- sammankopplingar

- in

- införa

- problem

- IT

- DESS

- jpg

- bara

- Nyckel

- Lam

- Large

- större

- lager

- skikt

- Layout

- ledande

- inlärning

- t minst

- Nivå

- nivåer

- livet

- tycka om

- sannolikt

- linje

- rader

- LITHO

- liten

- Logiken

- längre

- se

- förlust

- Lot

- Låg

- Maskinen

- maskininlärning

- gjord

- Huvudsida

- bibehålla

- göra

- Beslutsfattare

- Framställning

- chef

- tillverkad

- Tillverkare

- Produktion

- många

- marknad

- Marknadsföring

- Marknadsföringsdirektör

- mask

- Materialet

- material

- max-bredd

- Maj..

- betyda

- betyder

- medlem

- Minne

- metall

- Metaller

- Metrics

- kanske

- miljon

- miljoner

- minsta

- saknas

- modell

- modellering

- modeller

- lägen

- MOL

- molekyl

- månader

- mer

- mest

- flytta

- rörliga

- mycket

- multipel

- nästan

- Behöver

- behövs

- behov

- negativ

- Neutral

- Nya

- Nästa

- Nej

- Noble

- nod

- noder

- nu

- antal

- oktober

- of

- Ofta

- on

- gång

- ONE

- endast

- drift

- Verksamhet

- optimering

- Optimera

- optimerad

- or

- beställa

- Övriga

- Övrigt

- vår

- ut

- över

- Syrgas

- förpackning

- parametrar

- särskilt

- särskilt

- Mönster

- Personer

- utföra

- prestanda

- utför

- kanske

- perspektiv

- fas

- Fenomenet

- Philippe

- fysisk

- Fysiskt

- Fysik

- Pelare

- Tonhöjd

- svängbara

- Plasma

- plato

- Platon Data Intelligence

- PlatonData

- spelar

- PoC

- positiv

- Möjligheterna

- möjlig

- eventuellt

- potentiell

- potentiellt

- kraft

- den mäktigaste

- exakt

- Precision

- förutse

- VD

- tryck

- Problem

- problem

- process

- processer

- bearbetning

- producera

- Produkt

- produktutveckling

- Produktion

- produktivitet

- Produkter

- Profil

- Profiler

- lönsamhet

- Program

- Programmering

- lovande

- bevis

- bevis på koncept

- publikationer

- Tryck

- fråga

- snabbt

- R&D

- Ramp

- område

- Betygsätta

- rates

- ratio

- nå

- Reagera

- Reaktionen

- reaktioner

- verklig

- verkliga livet

- Anledningen

- nyligen

- Rekommendation

- rekommenderas

- minska

- reducerande

- reduktion

- reflektera

- regelbunden

- frigöra

- pålitlig

- förlita

- avlägsnande

- ta bort

- avlägsnas

- bort

- repeterbar

- upprepade

- ersätta

- rapport

- kräver

- Obligatorisk

- Krav

- Kräver

- forskning

- resultera

- Resultat

- avslöjar

- höger

- ROBERT

- Roll

- rullar

- ungefär

- regler

- Körning

- Nämnda

- Samma

- säga

- Skala

- skalning

- system

- Vetenskap

- Söker

- sett

- selektiv

- halvledare

- senior

- känsla

- inställning

- flera

- skifta

- skall

- Kisel

- Enkelt

- förenkla

- helt enkelt

- simulering

- enda

- skicklig

- Small

- So

- Mjukvara

- Lösningar

- LÖSA

- några

- någonstans

- Källa

- Utrymme

- specifik

- specifikationer

- specifikationer

- fart

- Stabilitet

- stabil

- staplade

- Stacks

- Personal

- stadier

- starta

- igång

- Steg

- Steg

- Fortfarande

- påkänning

- struktur

- Senare

- väsentlig

- sådana

- plötslig

- tillräcklig

- Föreslår

- leverantörer

- yta

- överraskning

- Hållbarhet

- hållbart

- Sweep

- Schweiziska

- System

- Ta

- tar

- Diskussion

- riktade

- grupp

- Teknisk

- Tekniken

- Teknologi

- Teknologisk utveckling

- termin

- testa

- Testning

- tester

- än

- den där

- Smakämnen

- Framtiden

- deras

- Dem

- sedan

- Där.

- termisk

- Dessa

- de

- saker

- Tredje

- detta

- grundligt

- tusentals

- tre

- Genom

- djur

- tätare

- tid

- Tidpunkten

- till

- tillsammans

- ton

- TON

- alltför

- topp

- Rör

- mot

- överförd

- Förvandla

- övergång

- Trend

- prova

- två

- typisk

- typiskt

- underliggande

- oförutsägbar

- på

- uppåt

- us

- användning

- Begagnade

- Användare

- med hjälp av

- utnyttja

- verifierade

- vertikal

- vertikalt

- mycket

- via

- genomförbar, livskraftig

- Vice President

- Vincent

- Virtuell

- flyktiga

- vill

- vill

- var

- Sätt..

- we

- veckor

- VÄL

- Vad

- när

- om

- som

- medan

- Hela

- varför

- kommer

- med

- inom

- utan

- ord

- Arbete

- arbetssätt

- fungerar

- skulle

- år

- år

- Avkastning

- vilket gav

- utbyten

- dig

- zephyrnet

- noll-