Nya stötstrukturer utvecklas för att möjliggöra högre sammankopplingstätheter i flip-chip-förpackningar, men de är komplexa, dyra och allt svårare att tillverka.

För produkter med högt antal stift, Flip chip [1] paket har länge varit ett populärt val eftersom de använder hela formområdet för sammankoppling. Tekniken har använts sedan 1970-talet, från och med IBMs C4 (controlled collapse chip-anslutning), men den kom verkligen till stor användning på 1990-talet.

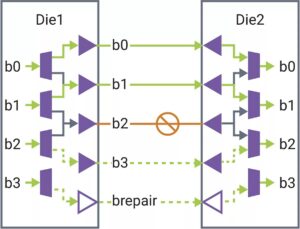

Sedan dess har bump-teknologin utvecklats för att hantera ökande effekt- och signalanslutningsdensitet som krävs av minne, högpresterande datorer och mobila datorenheter. För att möta den efterfrågan krävs ny sammankopplingsteknik som möjliggör mindre bump pitches, som för närvarande är under produktion.

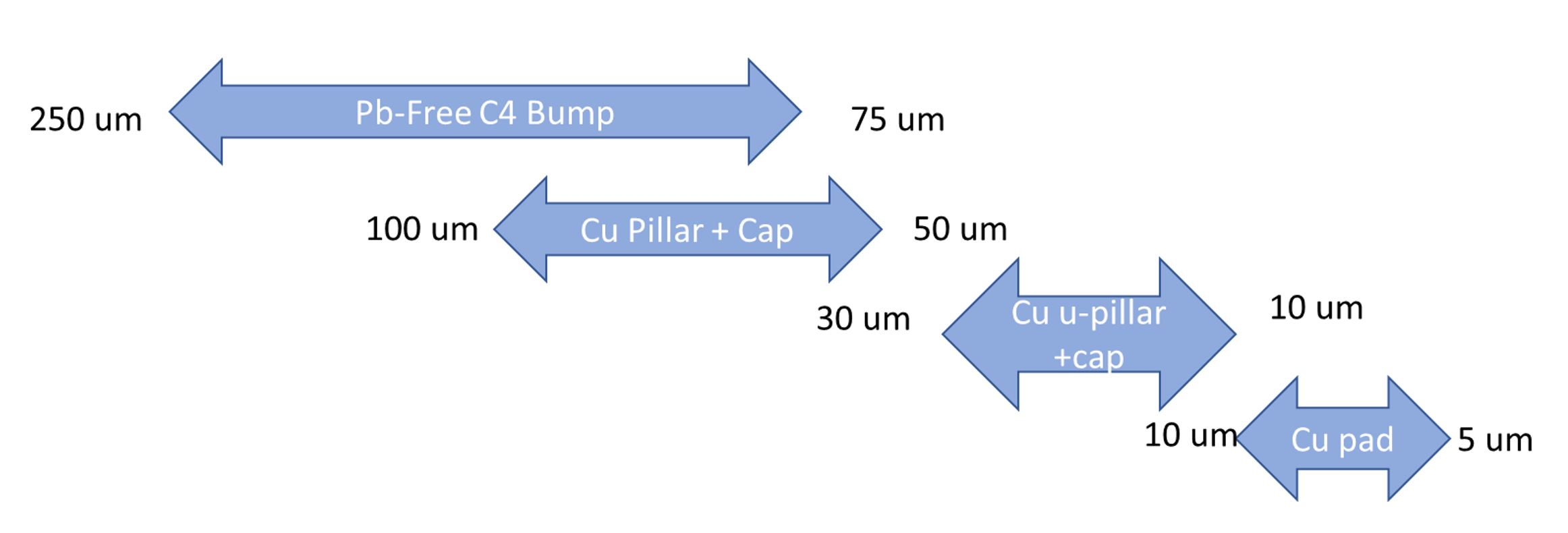

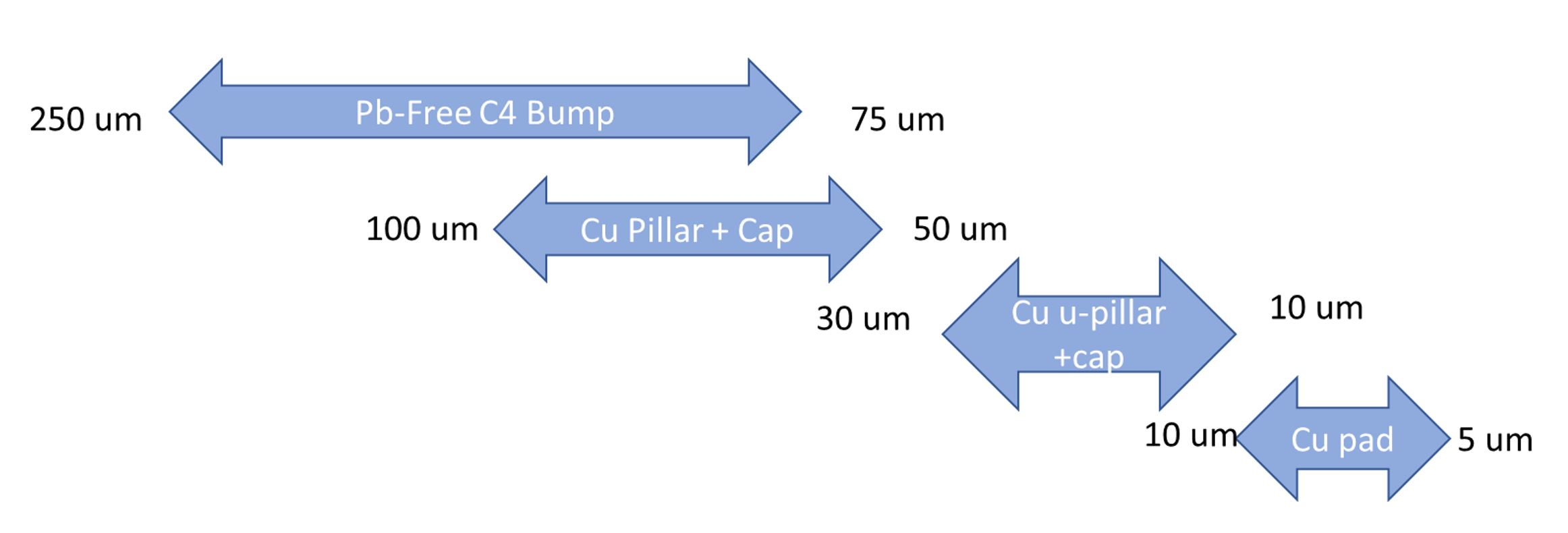

Sett över tid, går färdplanen för flip-chip-interconnect från blyfria stötar till kopparpelare och sedan till kopparmikrobulor. Stegstorlekarna fortsätter att krympa, vilket i sin tur har skapat tillverkningsutmaningar för stötning och limning.

Fig. 1: Flip-chip-teknikens tonhöjdsområden. Källa: A. Meixner/Semiconductor Engineering

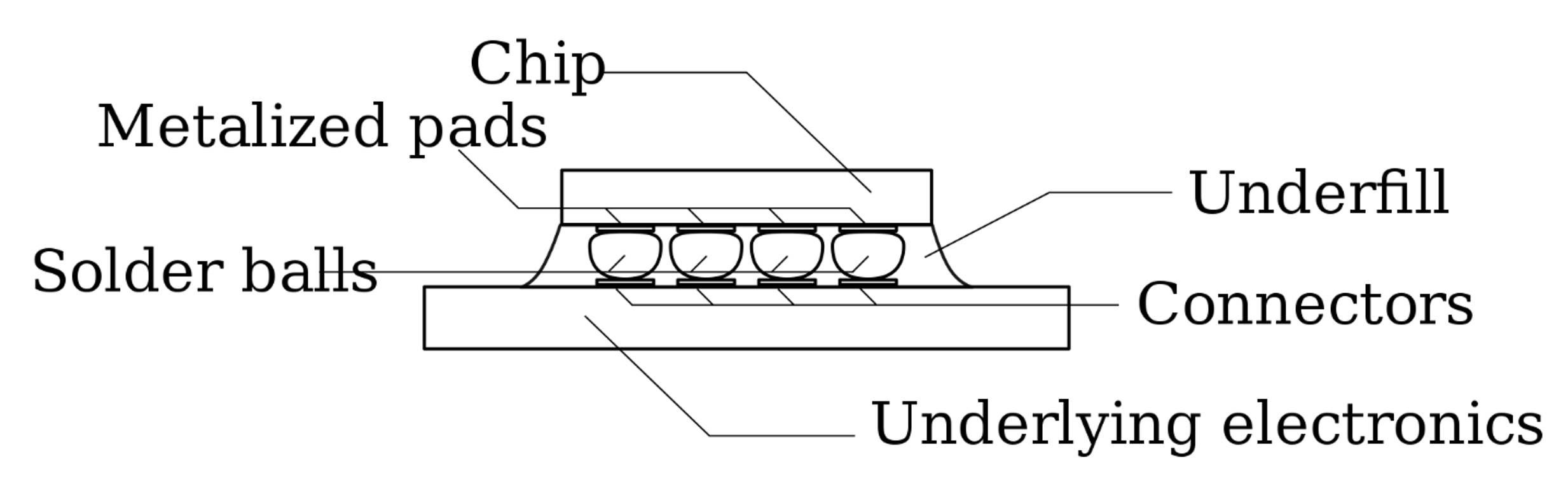

Fig. 2: Flip-chip komponenter. Källa: wikipedia

"På flip-chip-arenan - 250 mikron pitch och lägre - var det ursprungligen tenn-bly-bulor, och ett av de stora dragen var att bli blyfri. Men när du börjar nå 100 mikron eller lägre börjar du se mer av en kopparpelare, även om det finns en överlappning eftersom vi ser kopparpelare upp till 250 mikron”, säger Jeff Schaefer, senior processingenjör på Promex Industries. "Med 250 mikron stigningen ser vi 130 mikron bumpstorlekar eller kopparpelardiametrar. När vi väl kommer runt 100 mikron tonhöjden är den 80 mikron i diameter. Den minsta jag har sett är en 62.5 mikron stigning med en 40 mikron pelare. Jag förväntar mig att snart börja se 50 mikron tonhöjd."

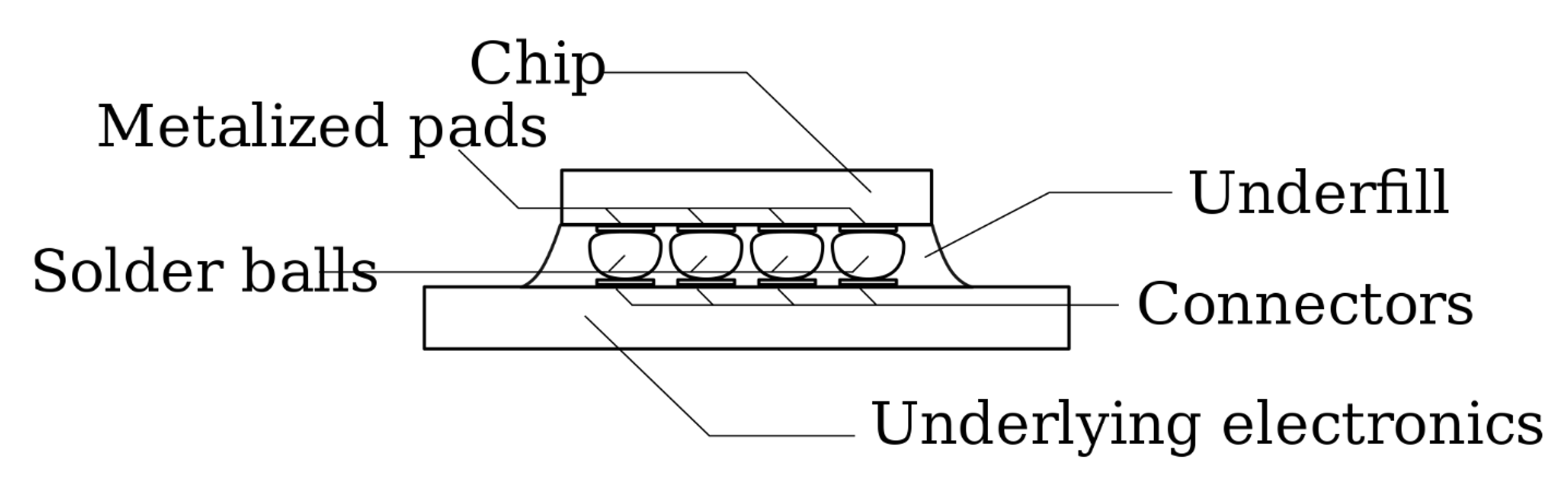

Den grundläggande flip-chip-processen börjar efter kretstillverkning, när metallkuddar skapas på formytan för att ansluta till I/O. Därefter kommer wafer bumping, där en lödkula placeras på varje dyna. Skivan skärs sedan i tärningar och dessa stansar vänds och placeras så att lödkulorna är i linje med substratkuddarna. Lödkulorna smälts/återflytas sedan, vanligtvis med hjälp av varmluft, och en monterad form underfylls med ett elektriskt isolerande lim, vanligtvis med kapillärverkan. [1]

Fig. 3: Flip-chip tillverkningsprocess. Källa: Wikipedia

Att flytta till en kopparpelare eller mikrobula kräver litografi för att skapa dessa strukturer.

"Kopparpelare används i allmänhet under 130 µm stigning, eftersom kopparpelaren i stället för att vara en cirkulär lödbult mestadels är en Cu-stolpe med lod på toppen", säger Doug Scott, senior vice president för wafer level packaging på Amkor teknologi. "Detta gör att kopparpelarens bulor kan placeras närmare varandra utan risk för att lodet kopplas ihop under monteringsåterflöde - i allmänhet ~40 µm Cu + ~25 µm."

Det finns variationer på temat också. "Microbump, som är en vanlig term som används där du har en sammankoppling mellan kisel-till-kisel, är något annorlunda eftersom CTE (koefficienten för termisk expansion) i allmänhet är densamma", säger Mark Gerber, senior director för ingenjörs-/teknisk marknadsföring på ASE-gruppen. "Några av de allmänna designreglerna som används för kopparpelare är desamma, men den plana yttopografin och fogarna med låg belastning möjliggör flexibilitet hos underfyllningen som används. Detta kan också driva den individuella bump-pitch. Idag är en 35 µm bump full-array pitch möjlig, på grund av de routingöverväganden som nämnts tidigare, för den wafer-nivå eller fab-nivå routing som används."

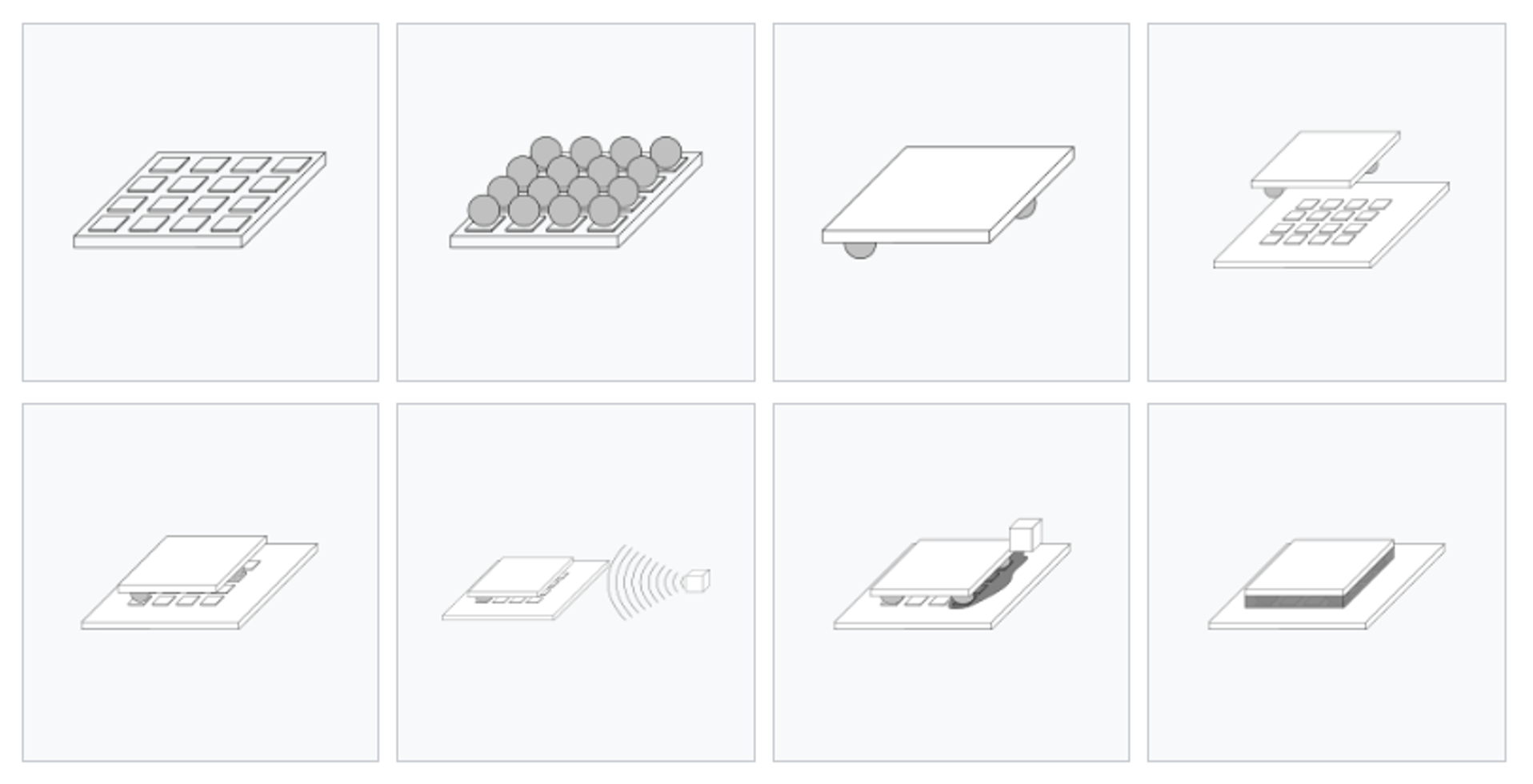

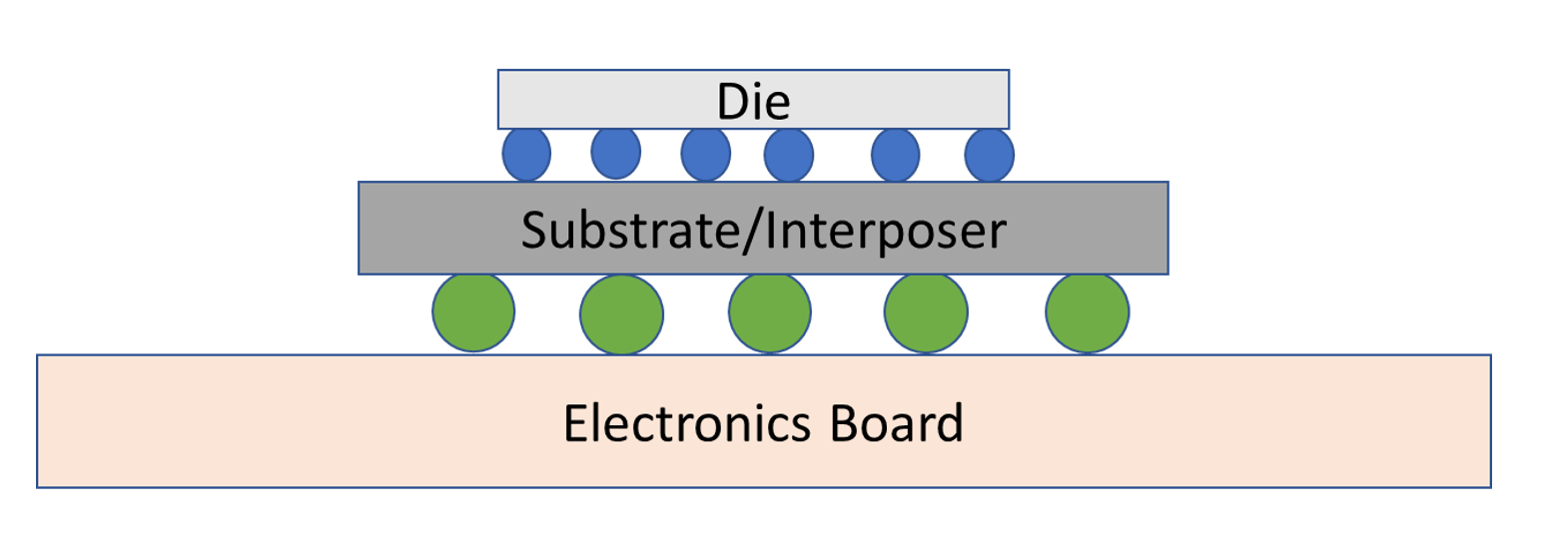

The Heterogeneous Integration Roadmap [2] beskriver alla aspekter av förpackning, inklusive sammankopplingar mellan form och substrat, från trådbindningar till genomgående kiselvägar. Med flip-chip-paket spelar sammankopplingar mellan dyna och substrat, omfördelningsområden för substrat och sammankopplingar mellan substrat och kort en roll i tillverkningsgränserna.

Fig. 4: Konceptuellt diagram av flip-chip-förpackningar. Källa: A. Meixner/Semiconductor Engineering

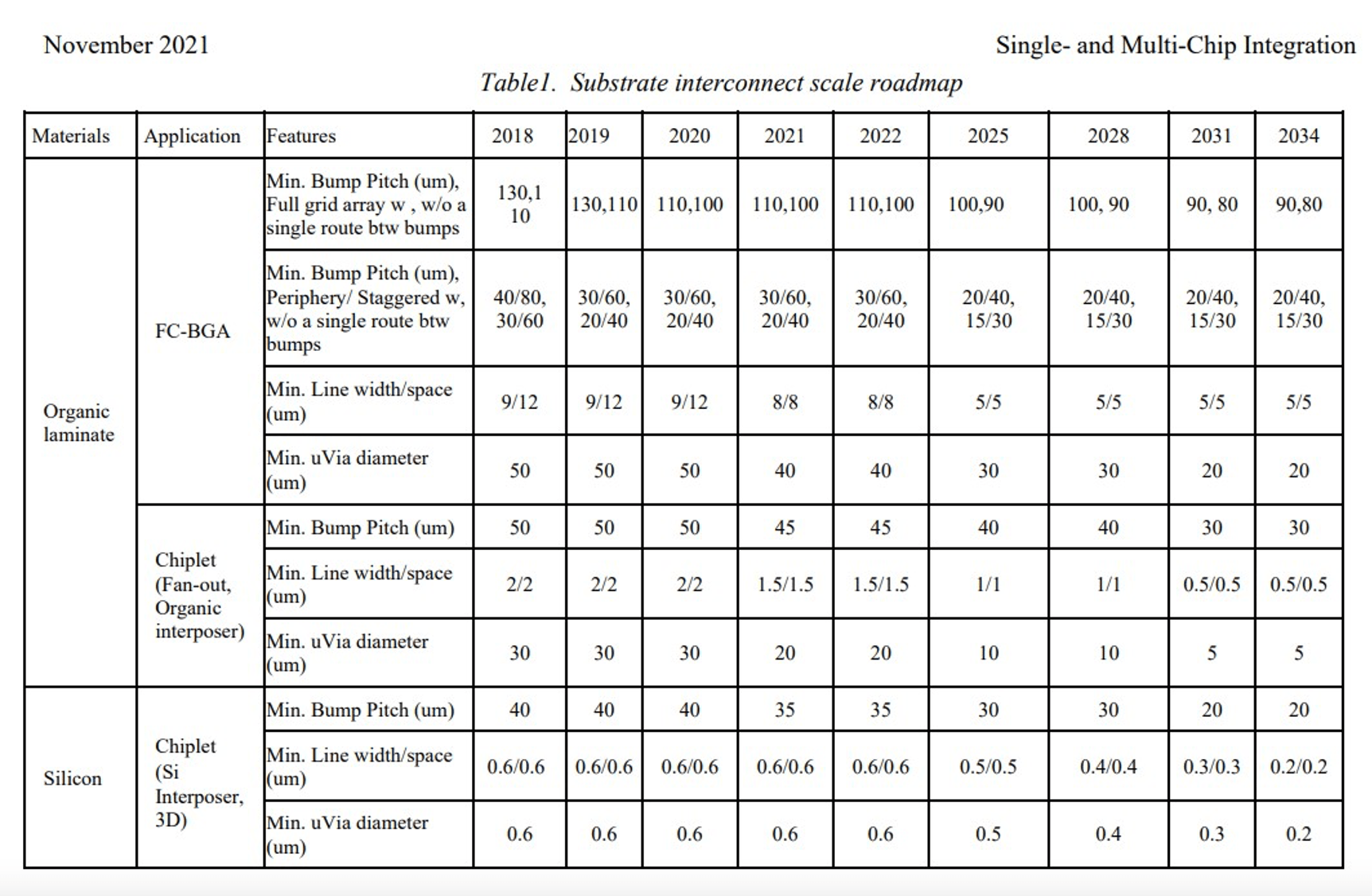

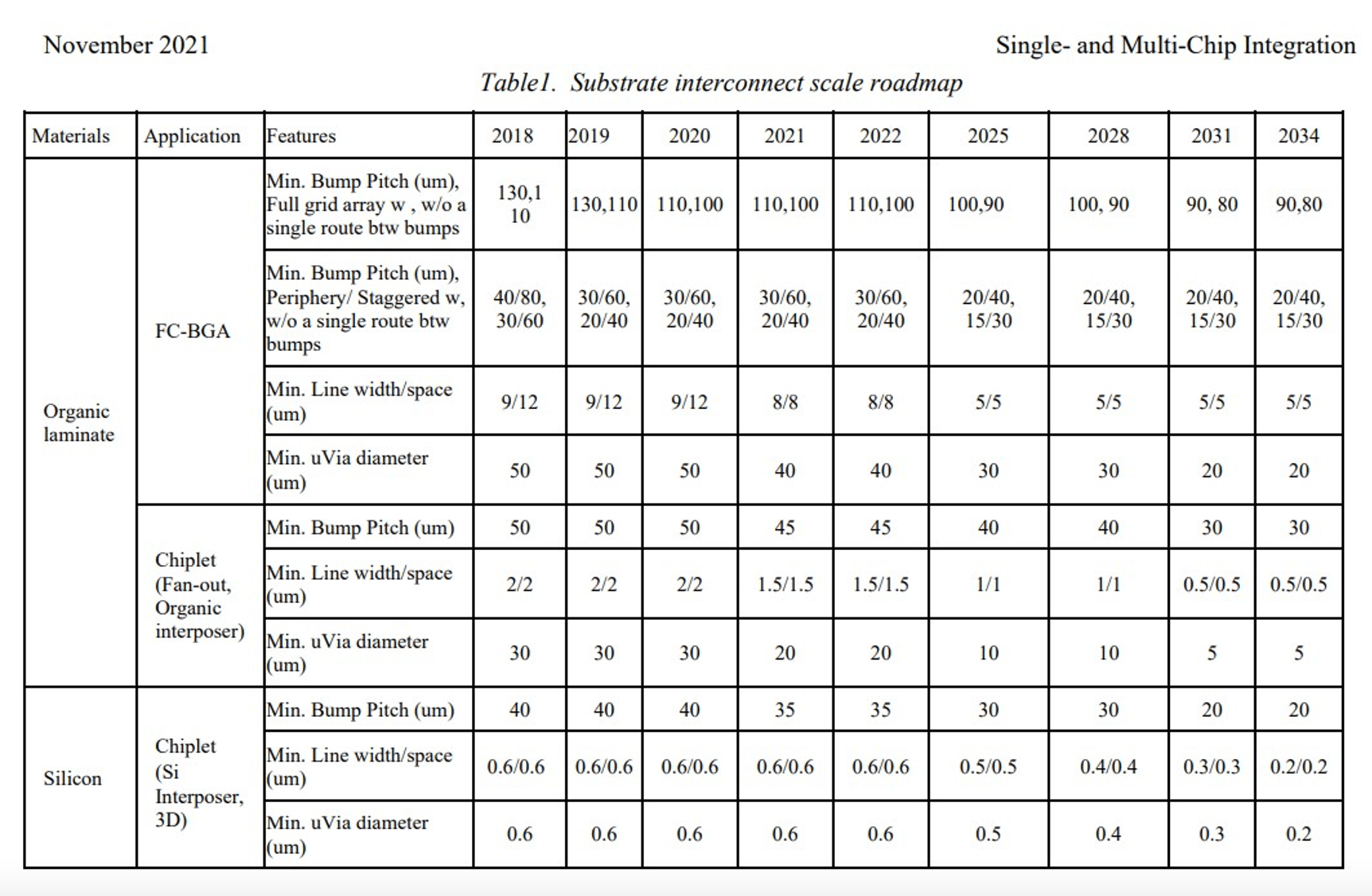

Kapitel 8 i färdplanen för heterogen integration [3] dokumenterar landskapet av nuvarande och planerade förpackningsteknologiska pitcher. Minsta tonhöjd för varje flip-chip-interconnect-teknologi finns i tabell 1 i underavsnitt 8.7 (sidan 41).

![Kapitel 8 i färdplanen för heterogen integration [3] dokumenterar landskapet av nuvarande och planerade förpackningsteknologiska pitcher. Minsta tonhöjd för varje flip-chip-interconnect-teknologi finns i tabell 1 i underavsnitt 8.7 (sidan 41).](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-7.png)

![Kapitel 8 i färdplanen för heterogen integration [3] dokumenterar landskapet av nuvarande och planerade förpackningsteknologiska pitcher. Minsta tonhöjd för varje flip-chip-interconnect-teknologi finns i tabell 1 i underavsnitt 8.7 (sidan 41).](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-8.png)

Motsvarande tabell för substratinterconnect (den del som ansluter paketet till kortet) finns i underavsnitt 8.8 (sidan 43).

Med varje förändring av sammankopplingsteknik kommer nya processer och deras begränsningar, som driver innovation, avkastningshantering och defektinspektion.

Bumping teknik gränser

Bumpteknik mäts genom stigning, storlek, höjd och elektriska och mekaniska egenskaper. Termiska överväganden varierar beroende på materialets CTE-fel. Skevhet är ett problem för större form och wafers, vilket förvärras av bakslipning av en wafer innan formen fästs.

"Det finns ett antal drivrutiner för tonhöjdsbegränsningar för varje typ av sammankoppling", säger ASE:s Gerber. "Från och med den traditionella sammankopplingen av lod-bump flip-chip bestäms pitch-kapaciteten av kollapshöjd för underfyllning, capture pad-pitch för trace-routing, capture-pad-pitch för bump-to-bump-kortrisk och flera andra tonhöjdsrelaterade känsligheter. Den förmonterade bumphöjden har en definierad höjd, men som IBM definierade C4-termen – Controlled Collapse Chip Connection – kommer diametern på lödbulten och capture pads storlek att avgöra sammankopplingens 'kollaps eller slutliga höjd'. Detta är den huvudsakliga stigningsbegränsande faktorn för att använda lodbullar relaterade till stigning."

Bumphöjden bestäms av design, men också bearbetningsval.

"För standardpläterade lödbullar och kopparpelare är höjderna för montering i allmänhet runt 70 µm till 75 µm, med kollapsade höjder efter montering på ~50 µm för att möjliggöra x,y,z utrymme för underfyllnadsflöde mellan gupparna. Microbumps kommer att ha mycket lägre bumphöjder och involvera plätering av mycket mindre lod. Specifikt kan mikrobulor vara mindre än 10 µm höga med reducerade Cu- och lödhöjder beroende på stigning och slutbehov, säger Amkors Scott. "Standardpläterade lodbullar används vanligtvis på stigningar från 130 µm till 250 µm. Under 130 µm finns det inte tillräckligt med xy utrymme mellan gupparna när man börjar med en 70 µm förmontering gupphöjd.”

Att skapa kopparpelare kräver fler bearbetningssteg än lödbullar.

"När vi övergick till världen från stansning till stans var tekniken annorlunda, för nu har du att göra med en oblat och planeriten är så bra jämfört med gjutna till substrat. Först skapar du kopparpelaren, på den första wafern som ska få lodet eller kopparpelaren finns det först en under bump metal (UBM). Det är ett litet lock över öppningen som går ner i kislet. Sedan bygger vi en kopparkärna av det och sätter sedan ett plåtlock på den. Så då den mottagande wafern, de ser ut som om de har en UBM-dyna där och den har vanligtvis någon plätering av nickelguldtyp så att den är snygg och ren”, förklarade Promex Industries Schaefer. Så istället för att ha en lätt fördjupning som ett laminatsubstrat, har du en lätt extrudering. Vi har upptäckt att vi faktiskt kan löda dem våta utan att "löda på dynan." Det är så de är designade och byggda. Den fungerar nästan som en lödning och en dyna eftersom det är en liten kupol i motsats till att försöka ta sig ner i ett hål.”

Fotolitografisteg som behövs för Cu-pelarbildning kommer med begränsningar såväl som substratdesignreglerna.

"För kopparpelare, som består av en kopparstolpe och ett lödlock i spetsen, kan kopparstolpens höjd definieras till begränsningen av en eller flera fotoresistskiktstjocklekar och när du minskar stigningen, kan bildförhållandet för cu post höjd till pitch blir begränsningen tillsammans med fotoresistmaterialet och bildverktygets kapacitet”, sa Gerber. "En sekundär begränsning för kopparpelarens sammankoppling är de substratdesignregler som används. För fin pitch >110um pitch används 2 primära metoder - BOT (Bond on Trace) eller ET - Embedded Trace, där kopparpelarens lödlock placeras ovanpå trace istället för en traditionell capture pad. Kopparpelarens storlek och form, inklusive begränsningarna ovan, kan ge en gräns för kapaciteten och färdplanen för att fortsätta att krympa planerna. Många av dessa begränsningar beror på förmågan att dirigera spår mellan pelarna på substratsidan. När ny teknik är tillgänglig, såsom RDL på wafer-nivå, kommer sammankopplingsfärdplanerna att drivas ytterligare, men fortfarande med begränsningar kring höjd/bildförhållandet för tillverkningsprocesser som underfill."

Andra håller med om att underfyllningsprocessen kommer med utmaningar. "När du får finare ton och mindre gupp blir de kortare. Det börjar bli svårt att hitta underfyllningar för att komma under. Underfyllningarna har historiskt utformats för att komma under ett gap på 5 mil, och nu kommer de ner till 3 mil, vilket är 75 mikron, säger Schaefer. "Nu börjar vi se 60 och 25 mikron gap. Jag är säker på att folk jobbar på nya underfyllningar. Men det finns mycket att jobba på. För det första, när du får finare partiklar, blir det mer som ett slam, vilket gör det svårare att rinna. Det här är en vägspärr som måste tas bort.”

Hantera avkastning

När stöttekniken blir mindre öppnar ytterligare bearbetningssteg - till exempel litografi för att skapa kopparpelare - nya möjligheter för avkastningsdetektorer. För en framgångsrik bindningsprocess är partiklar, ytföroreningar och lödtömning problematiska för utbytet. Dessa kräver processkontroller, mätteknik och inspektion.

Naturligtvis kontrolleras kontaminering. "Tier 1 OSATs investerar för att minska nivån av fabriksföroreningskällor och därför minska andelen defekter", säger Amkors Scott. "Pitch bidrar inte till defekter. Liknande nivåer av defekter finns oavsett tonhöjd."

Men pitch lägger till några av sina egna utmaningar. "Eftersom tonhöjden blir mindre och stötstorleken minskar är hanteringen av partikelkontamination mycket viktig. För andra typer av sammankopplingar som hybridbindning, där avstånden minskar under 30 µm och kontakten mellan yta och yta är viktig, är waferbaserad renrumsmiljö avgörande för avkastningen, säger ASE:s Gerber.

Förberedelserna för underfyllningsprocessen ska inte heller underskattas.

"Generellt med ett laminat, kommer du att göra en underfill efter att du har gjort flip chip," sade Promex Schaefer. "Vi bestämmer var vi ska placera den och hur den ska återföras. Vi rengör den för att få ut eventuellt flussmedel under springan mellan formen och substratet. Sedan ska vi underfylla med en epoxi som rinner. Den är designad för att blötas in och inte lämna tomrum och sådant. Men det finns en utmaning när vi kommer till finare plan. Gupparna blir lite kortare, och när de blir kortare blir gapet mellan chipet och underlaget mindre, så det är svårare att rengöra. Föreställ dig att du sätter ihop två glasskiva för att försöka få ut smutsen mellan dem.”

Mätteknik och inspektionsbehov

För att hantera processkontroll och avkastning spelar mät- och inspektionsverktyg en viktig roll. "Det finns tillgängliga verktyg på marknaden som kan hjälpa till att ge vägledning om sammankopplingsintegritet, förutom i process tvärsnittsanalys som används vid installation och vid definierade produktionsintervall", säger ASE:s Gerber.

Bumlingsprocessen och bindningsprocesserna har var och en specifika egenskaper som måste övervakas. För gupp fokuserar metrologi på diameter, höjd och planaritet. Mindre stigningar kräver strängare kontroll av guppdiameter och höjdkontroll. På liknande sätt, när bumphöjden krymper, blir fönstret för coplanaritet mindre. Normalt tillåts 10 % variation. Till exempel resulterar en höjd på 30 µm i en tillåten variation på ±3 µm. Att överskrida detta bidrar till misslyckad eller dålig bindning.

"Bindning görs vanligtvis med mass-reflow-ugnar", säger Mike Kelly, vice vd för avancerad paket- och teknologiintegration på Amkor. "Den initiala karakteriseringen av återflödesprocessen är etablerad med hjälp av shadow-moire för att kvantifiera skevheten under återflöde, och temperaturkartläggning av ugnarna för att säkerställa konsekvent temperaturkontroll av själva flip-chipdelen. Under installationen, mekanisk dyslyft och inspektion för att säkerställa god lödvätning. Dessutom appliceras flussmedel vanligtvis med ett "doppflöde", varvid formstötarna "doppas" i tunna, hårt kontrollerade fluxreservoarer. Visuell inspektion av dessa föremål görs på provtagningsbasis."

Ökad automatisering av visuell inspektion minskar beroendet av operatörer att se en bild och fatta ett beslut. Den exponentiella ökningen av bump-anslutningarna är en drivkraft. Ändringar av bindningsprocesser ger en annan. En självjusterad lödåterflödesprocess är en mogen teknologi. Med den termiska kompressionsbindning som vanligtvis används i avancerade förpackningar, finns det tillförlitlighetsmekanismer som klarar elektriska tester. Det leder i sin tur till användningen av röntgeninspektioner och mätverktyg för att se knölarna efter limning.

"För lågkomplexitetsförpackningar kan anläggningar komma undan med en operatör och manuell inspektion. För en del med 100 stötar är denna metod genomförbar. Vid 1,000 10,000 gupp är det definitivt en påfrestning. När en del har XNUMX XNUMX stötar är det ingen chans. Vi går längre än den här punkten och vi måste gå vidare till nästa metod”, konstaterade Frank Chen, chef för applikationer och produktledning på Bruker. "Kvaliteten och komplexiteten går hand i hand, för när du försöker göra något mer komplext kommer din avkastning att påverkas och det kommer att krävas en del nya verktyg. Och verktyg innebär både processverktyg och mätverktyg, så båda måste avancera parallellt. Från våra egna studier ser vi att när du väl når de där 1,000 XNUMX gupp, det är då du måste börja tänka "Min manuella teknik är otillräcklig och jag behöver något nytt."

En mängd olika inspektions- och mätverktyg finns tillgängliga för att stödja pakettillverkning.

”Det finns flera metoder som kan eller bör användas för att uppnå processkontroll. Först, traditionell 2D-inspektion (AOI) för 100 % inspektion av ytdefekter per processflöde (dvs. IQC, OQA, foto, rengöring, plätering, etc.) Därefter kan 2D-metrologi (AOI) användas för att styra bumpstorlek och diameterstorlek kontrollera. Dessutom kan 3D-metrologi (AOI) användas för inhämtning av mätinformation för en sampling av bumphöjd/samplanaritet (detta görs vanligtvis med en lasertrianguleringsbaserad teknologi), säger Nathan Peng, produktmarknadschef på På innovation. "Vidare kan 3D-metrologi rikta in sig på individuella bumphöjdsegenskaper, vanligtvis insamlade med interferometerteknik för vitt ljus. Det finns också metoder för att möjliggöra detektering av organiska rester på bump toppen som kan leda till fel med bump to pad-anslutning.”

Slutsats

Produkter som kräver högre sammankopplingsantal fortsätter att driva sammankopplingsfärdplanen. Varje flip-chip-teknologi har tillverkningsbegränsningar som involverar materialegenskaper, krympande storlekar som utmanar underfyllningsteknologier och ökad användning av litografi för att skapa sammankopplingsstrukturerna. Varje förändring i bindningsprocesser resulterar i en ökning av mät- och inspektionsstegen för att uppnå avkastnings- och kvalitetsmål.

Referensprojekt

- https://en.wikipedia.org/wiki/Flip_chip

- https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2021-edition.html

- HIR Kapitel 8 Single Chip och Multi Chip Integration, https://eps.ieee.org/images/files/HIR_2021/ch08_smcfinal.pdf

Relaterade berättelser:

Bump Co-planarity och inkonsekvenser orsakar avkastning, tillförlitlighetsproblem

Avancerade förpackningsutmaningar växer när chips och förpackningsstorlekar krymper; olika utrustning, teknik vinner dragkraft.

Bump-tillförlitlighet utmanas av latenta defekter

Automatiserade lösningar är på gång, men de kommer att ta tid att utveckla.

Stora förändringar framöver i kraftleverans, material och sammankopplingar

Hur tillverkning och förpackning kommer att förändras under de kommande decennierna.

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- PlatoAiStream. Web3 Data Intelligence. Kunskap förstärkt. Tillgång här.

- Minting the Future med Adryenn Ashley. Tillgång här.

- Köp och sälj aktier i PRE-IPO-företag med PREIPO®. Tillgång här.

- Källa: https://semiengineering.com/challenges-grow-for-creating-smaller-bumps-for-flip-chips/

- : har

- :är

- :inte

- :var

- $UPP

- 000

- 1

- 10

- 100

- 250

- 2D

- 3d

- 40

- 7

- 8

- a

- förmåga

- Able

- ovan

- Uppnå

- förvärv

- Handling

- handlingar

- faktiskt

- Dessutom

- Annat

- Lägger

- avancera

- avancerat

- Efter

- framåt

- LUFT

- rikta

- Alla

- tillåter

- tillåter

- längs

- också

- an

- analys

- och

- Annan

- vilken som helst

- tillämpningar

- tillämpas

- ÄR

- OMRÅDE

- områden

- runt

- AS

- aspekt

- aspekter

- Montage

- At

- bifoga

- Automation

- tillgänglig

- bort

- tillbaka

- boll

- grundläggande

- grund

- BE

- därför att

- blir

- varit

- innan

- Där vi får lov att vara utan att konstant prestera,

- nedan

- mellan

- Bortom

- Stor

- ombord

- bindning

- Bot

- båda

- SLUTRESULTAT

- byggt

- men

- by

- kom

- KAN

- lock

- kapacitet

- fånga

- Orsak

- utmanar

- utmanade

- utmaningar

- chans

- byta

- Förändringar

- Kapitel

- egenskaper

- chen

- chip

- Pommes frites

- val

- val

- närmare

- Collapse

- kollapsade

- komma

- kommer

- Gemensam

- vanligen

- jämfört

- komplex

- Komplexiteten

- komponenter

- databehandling

- begreppsmässig

- Oro

- Kontakta

- Anslutning

- anslutning

- Anslutningar

- ansluter

- överväganden

- konsekvent

- kontakta

- föroreningar

- fortsätta

- fortsätter

- bidra

- kontroll

- kontrolleras

- styrning

- kontroller

- Koppar

- Kärna

- Motsvarande

- kunde

- Par

- skapa

- skapas

- Skapa

- kritisk

- Aktuella

- För närvarande

- datum

- som handlar om

- årtionden

- Beslutet

- definierade

- definitivt

- leverans

- Efterfrågan

- densitet

- beroende

- avsatt

- Designa

- utformade

- Detektering

- Bestämma

- bestämd

- utveckla

- utvecklade

- enheter

- den

- olika

- svårt

- Direktör

- smuts

- do

- dokument

- gör

- gjort

- ner

- driv

- chaufför

- chaufförer

- grund

- under

- e

- E&T

- varje

- antingen

- inbäddade

- möjliggöra

- möjliggör

- änden

- ingenjör

- Teknik

- tillräckligt

- säkerställa

- Miljö

- Utrustning

- etablerade

- etc

- Eter (ETH)

- utvecklats

- exempel

- existerar

- expansionen

- förvänta

- dyra

- förklarade

- exponentiell

- anläggningar

- faktor

- fabrik

- Misslyckande

- Fig.

- slutlig

- hitta

- änden

- Förnamn

- platta

- Flexibilitet

- Flip

- flöda

- flöden

- FLÖDE

- fokuserar

- För

- för avkastning

- bildning

- hittade

- från

- ytterligare

- Vidare

- Få

- spalt

- luckor

- Allmänt

- allmänhet

- skaffa sig

- få

- glas

- Go

- Går

- kommer

- Gold

- god

- slipning

- Väx

- vägleda

- hantera

- Hård

- Har

- har

- höjd

- höjder

- hjälpa

- Hög

- högpresterande

- högre

- historiskt

- Hål

- HET

- Hur ser din drömresa ut

- How To

- html

- HTTPS

- Hybrid

- i

- IBM

- IEEE

- bild

- bild

- Imaging

- påverkade

- med Esport

- in

- Inklusive

- Öka

- ökat

- ökande

- alltmer

- individuellt

- informationen

- inledande

- Innovation

- istället

- integrering

- integritet

- sammankopplingar

- in

- Invest

- engagera

- IT

- artikel

- DESS

- sig

- liggande

- större

- Lasern

- lager

- leda

- Lämna

- mindre

- Nivå

- nivåer

- ljus

- tycka om

- BEGRÄNSA

- begränsning

- begränsningar

- gränser

- liten

- Lång

- se

- ser ut som

- Lot

- Låg

- Huvudsida

- göra

- GÖR

- ledning

- chef

- hantera

- manuell

- manuellt

- Produktion

- många

- kartläggning

- markera

- marknad

- Marknadsföring

- Materialet

- material

- mogen

- max-bredd

- betyder

- mekanisk

- mekanismer

- Möt

- möte

- Minne

- nämnts

- metall

- metod

- metoder

- Metrology

- mikron

- Mike

- minsta

- Mobil

- övervakas

- mer

- för det mesta

- flytta

- förflyttar

- mycket

- flera

- Natur

- Behöver

- behövs

- behov

- Nya

- Ny teknik

- Nästa

- trevligt

- Nickel

- Nej

- noterade

- nu

- antal

- mål

- of

- on

- gång

- ONE

- öppet

- öppning

- Operatören

- operatörer

- möjligheter

- motsatt

- or

- ekologisk

- ursprungligen

- Övriga

- vår

- ut

- över

- egen

- paket

- paket

- förpackning

- vaddera

- sida

- Parallell

- del

- partikel

- passera

- Personer

- Pelare

- Tonhöjd

- platser

- Plats

- plato

- Platon Data Intelligence

- PlatonData

- Spela

- Punkt

- dålig

- Populära

- populärt val

- placerad

- möjlig

- Inlägg

- kraft

- VD

- primär

- Innan

- process

- processer

- bearbetning

- Produkt

- produktledning

- Produktion

- Produkter

- projicerade

- egenskaper

- ge

- sköt

- sätta

- kvalitet

- som sträcker sig

- ratio

- nå

- verkligen

- mottagande

- minska

- Minskad

- minskar

- Oavsett

- relaterad

- tillförlitlighet

- tillit

- avlägsnas

- kräver

- Obligatorisk

- Kräver

- Resultat

- Risk

- färdplan

- färdplaner

- Roll

- Rum

- Rutt

- routing

- regler

- Nämnda

- Samma

- sekundär

- se

- se

- sett

- halvledare

- senior

- inställning

- flera

- Forma

- skifta

- Kort

- skall

- sida

- Signal

- Kisel

- liknande

- Liknande

- eftersom

- enda

- Storlek

- storlekar

- Diabilder

- något annorlunda

- mindre

- So

- Lösningar

- några

- något

- Alldeles strax

- Källa

- Källor

- Utrymme

- specifik

- specifikt

- standard

- starta

- Starta

- Steg

- fastklibbning

- Fortfarande

- Upplevelser för livet

- påkänning

- studier

- framgångsrik

- sådana

- stödja

- yta

- SVG

- bord

- Ta

- Målet

- Tekniken

- Teknologi

- termin

- Testning

- än

- den där

- Smakämnen

- Landskapet

- deras

- Dem

- tema

- sedan

- Där.

- därför

- termisk

- Dessa

- de

- saker

- Tänkande

- detta

- de

- fastän?

- tätt

- tid

- Tips

- till

- i dag

- tillsammans

- verktyg

- verktyg

- topp

- spåra

- dragkraft

- traditionell

- prova

- SVÄNG

- två

- Typ

- typer

- typiskt

- under

- på

- användning

- Begagnade

- med hjälp av

- vanligen

- utnyttja

- mängd

- mycket

- Vice President

- utsikt

- tömning

- var

- we

- VÄL

- när

- som

- vit

- Hela

- utbredd

- wikipedia

- kommer

- med

- utan

- Arbete

- arbetssätt

- fungerar

- världen

- X

- röntgen

- Avkastning

- utbyten

- dig

- Din

- zephyrnet