I integrerad kretsterminologi är en droop spänningsfallet som sker i en krets. Detta är ett välkänt fenomen och kan hända av följande orsaker. Strömförsörjningen faller under det driftsområde som ett chip är designat för, vilket resulterar i ett fall. Mer ström dras av de ledande elementen än vad de var konstruerade för, vilket resulterar i ett fall. Ibland kan signalstörningar eller brus på strömförsörjningen också orsaka spänningsfluktuationer, vilket resulterar i ett sjunkande.

Dropp kan påverka en krets funktion. Minskad prestanda hos chippet, vilket leder till längre behandlingstider är en sådan påverkan. Men följande är några av de mer allvarliga och/eller katastrofala konsekvenserna. Chipet skulle kunna dra mer ström för att bibehålla prestandanivån, vilket leder till ökad strömförbrukning och värmeavledning. Detta kan leda till minskad livslängd för chippet och i allvarliga fall, ett fullständigt fel på chipet på grund av variationer i inställning och hållning. Droops kan också orsaka datakorruption eller fel i utdata. Detta är ett mycket allvarligt problem för applikationer som beror på chipets noggrannhet och tillförlitlighet.

Naturligtvis tas fenomenet droops i beaktande när man designar chips och system. De vanligaste metoderna för att mildra sjunker är frånkoppling av strömförsörjning, spänningsreglering, kretsoptimering och strömhantering på systemnivå. Förhållandena och den driftsmiljö som chipet kommer att fungera i beaktas noggrant när man designar lösningar för att lindra släpp.

Dagens problem

När SoCs blir mer komplexa kan problem med hängande också bli ganska komplexa. En SoC:s design måste optimeras för prestanda, effekt, kostnad, formfaktor, etc. förutom att optimera för att minska sänkningar. Ibland kan dessa optimeringsmål konkurrera med varandra och motverka och avvägningar måste göras. Till exempel kan SoC-arkitekter höja driftspänningen, lägga till marginal, för att kringgå lokal och global nedgång, men denna ökning ökar effekten kvadratiskt. Alternativt kan designers få sin klockgenerering att anpassa sig till att sjunka, vilket gör prestandan till en funktion av kopplingstiden för klockgenereringen.

Följaktligen är stora SoCs i datacentrets datorer och AI-utrymme särskilt mottagliga för att sjunka. Kundernas arbetsbelastning är mycket varierande och dynamisk, vilket leder till betydande fluktuationer i bytesaktivitet och strömdragning. Naturligtvis har system inte råd att låta hängande problem försvinna. Det potentiella ansvaret från felaktig utdata eller katastrofala fel på ett chip är för högt för dagens system och applikationer.

Lokaliserade Droop-problem

Applikationsspecifika acceleratorer används i stor utsträckning tillsammans med generella processorer för att leverera den prestanda och energieffektivitet som krävs i dagens krävande datormiljöer. Men dessa acceleratorer samt det ökande antalet kärnor och arbetsbelastningens asymmetriska karaktär ökar risken för lokala spänningsfall. Dessa lokala spänningsfall är ett resultat av plötslig ökning av kopplingsaktiviteten och kan orsaka övergående fel och potentiella misslyckanden i uppdragsläge.

När lokal sänkning inträffar kan påverkan mildras genom dynamisk frekvensskalning. Detta uppnås genom att justera tidpunkten för en krets med hjälp av en programmerbar klocka. En programmerbar klocka tillåter att klockfrekvensen och timingen justeras dynamiskt baserat på kretsens nuvarande driftsförhållanden.

Movellus gör det enkelt att åtgärda lokaliserade droppar

Movellus, en ledande leverantör av digitala system-IP, har utvecklat produktfamiljen Aeonic Generate för att ta itu med lokala problem. Movellus Aeonic-portföljen erbjuder adaptiva klockningslösningar som levererar snabb hängrespons. Portföljen inkluderar det adaptiva klocksystemet. Byggstenarna är byggda med syntetiserbar Verilog, vilket gör dem flexibla i sig. Lösningarna är konfigurerbara, skanningsbara och processportabla för ett brett utbud av avancerade SoC-applikationer.

Aeonic Generate-produktfamiljen är också betydligt mindre än traditionella analoga lösningar. Som ett resultat kan designers instansiera IP:n med den granularitet som krävs utan någon betydande inverkan på området. Dessutom, när konstruktioner går över till finare processgeometrier, fortsätter Aeonic Generate-området att skalas, vilket gör det till en idealisk lösning för framtida konstruktioner.

Ett par användningsfall

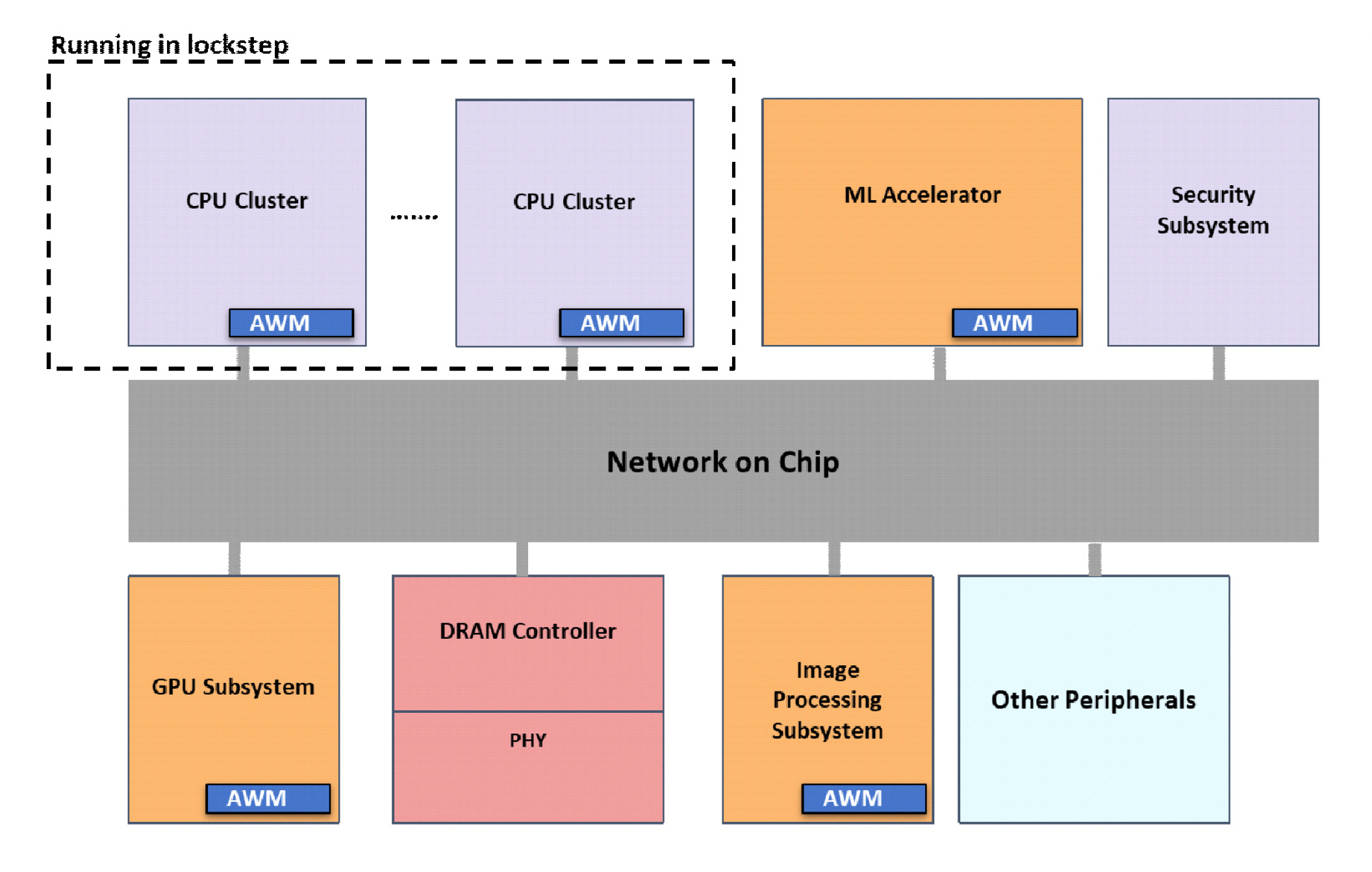

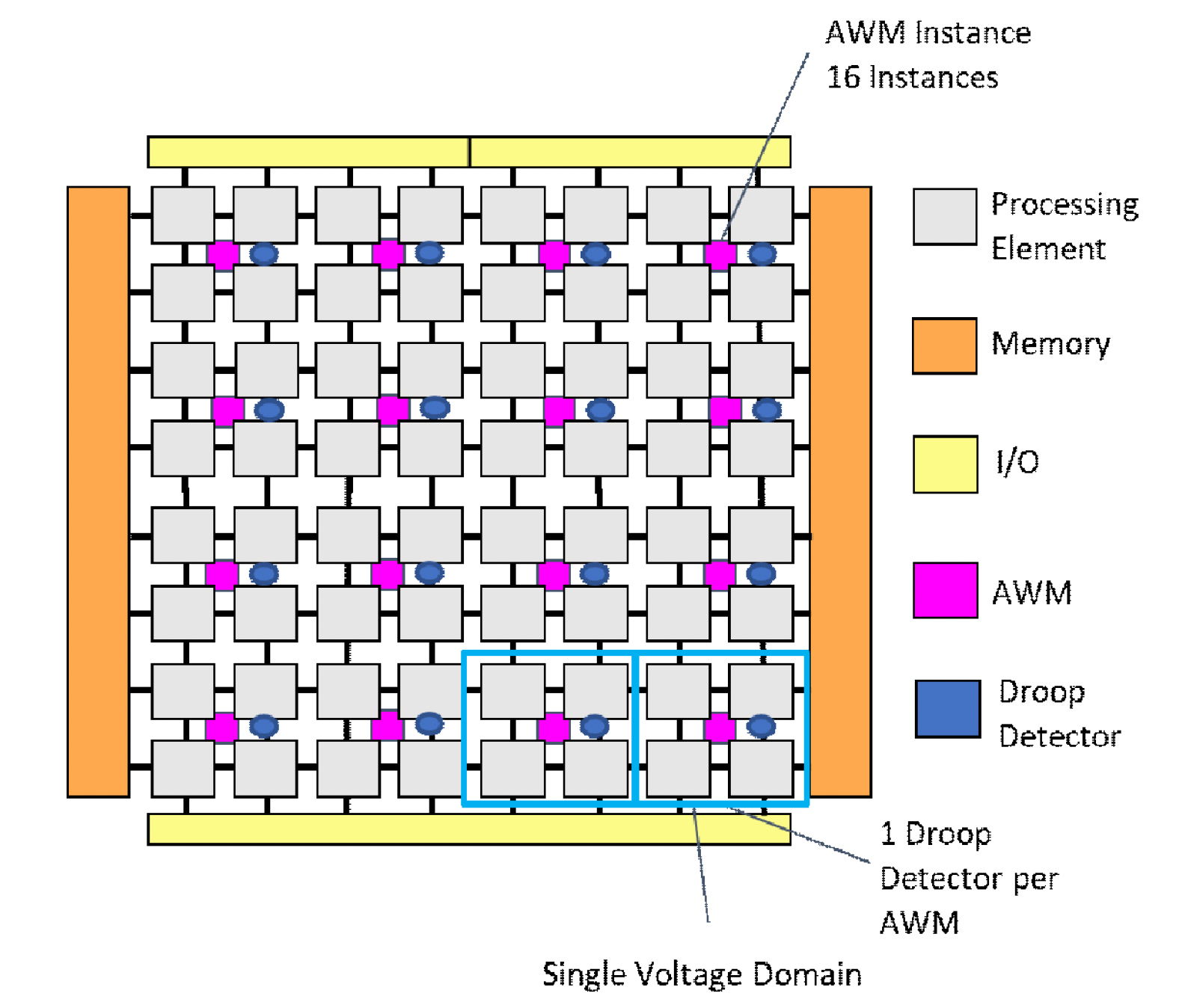

Följande bild från Movellus visar ett exempel på arkitektur för en ADAS-processor med Aeonic Generate AWM-plattformen för lokaliserat droop-stöd. En arkitekt skulle para ihop en AWM-modul med ett applikationsspecifikt underblock eller accelerator för att svara på arbetsbelastningsdrivna lokaliserade droppar inom fem klockcykler med felfria och snabba frekvensskiftningar. Det här tillvägagångssättet ger en tillförlitlig och effektiv lösning för att hantera utmaningarna med lokaliserade avbrott på ADAS-, 5G- och datacenternätverksmarknader.

Följande figur från Movellus visar ett exempel på arkitektur av ett hav av processor SoC med Aeonic Generate för lokaliserat droop-stöd. En arkitekt skulle para ihop en Aeonic Generate AWM-modul med en droop-detektor för processorklustret och tillhörande spänningsdomän för att snabbt svara på arbetsbelastningsdrivna lokaliserade droops. Detta gör att konstruktörer kan leverera lokaliserad och oberoende dropprespons utan att ändra prestandan hos närliggande processorkluster.

Sammanfattning

Lokaliserade spänningsfall kan förekomma i heterogena SoCs som innehåller applikationsspecifika acceleratorer. Dessa fall kan leda till tidsfel, tillfälliga fel och misslyckanden i uppdragsläge i ADAS, datacenternätverk och 5G-applikationer. Systemarkitekter kan implementera adaptiv klockning för att svara på dessa fall och mildra påverkan.

Movellus™ Aeonic Generate Adaptive Workload Module (AWM)-familjen av högpresterande IP-produkter för klockgenerering är en del av Aeonic Intelligent Clock Network™-arkitekturen. För mer information, se Movellus' Aeonic Generate™ AWM-sida.

Läs också:

Fördelar med storskaliga synkrona klockningsdomäner i AI-chipdesigner

Det är nu dags för smarta klocknätverk

Prestanda, kraft och area (PPA) fördelar genom intelligenta klocknätverk

Dela det här inlägget via:

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- Platoblockchain. Web3 Metaverse Intelligence. Kunskap förstärkt. Tillgång här.

- Källa: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :är

- 5G

- a

- accelerator

- acceleratorer

- noggrannhet

- uppnås

- aktivitet

- anpassa

- ADA:er

- Dessutom

- Dessutom

- adress

- adresse

- justerat

- avancerat

- AI

- tillåter

- och

- tillämpningar

- tillvägagångssätt

- arkitektur

- ÄR

- OMRÅDE

- AS

- associerad

- At

- baserat

- BE

- blir

- nedan

- Fördelarna

- Blockera

- Block

- Byggnad

- byggt

- by

- KAN

- Kan få

- kan inte

- försiktigt

- fall

- katastrofal

- Orsak

- Centrum

- utmaningar

- chip

- Pommes frites

- klocka

- kluster

- Gemensam

- konkurrera

- fullborda

- komplex

- Compute

- databehandling

- villkor

- övervägande

- anses

- konsumtion

- fortsätter

- Korruption

- Pris

- kunde

- Motverka

- Par

- Naturligtvis

- Aktuella

- kund

- cykler

- datum

- Data Center

- Datacenter

- dag

- leverera

- krävande

- Designa

- utformade

- konstruktörer

- design

- mönster

- utvecklade

- digital

- distribueras

- flera

- domän

- domäner

- dras

- Drop

- Droppar

- dynamisk

- dynamiskt

- varje

- effektivitet

- effektiv

- element

- Miljö

- miljöer

- fel

- etc

- exempel

- Misslyckande

- Falls

- familj

- Figur

- flexibel

- fluktuationer

- efter

- För

- formen

- Frekvens

- från

- fungera

- framtida

- generell mening

- generera

- generering

- skaffa sig

- Välgörenhet

- Go

- Mål

- hända

- händer

- Har

- Hög

- högpresterande

- hålla

- HTTPS

- idealisk

- Inverkan

- Konsekvenser

- genomföra

- in

- felaktig

- innefattar

- Öka

- ökat

- Ökar

- ökande

- oberoende

- informationen

- integrerade

- integrering

- Intelligent

- i sig själv

- IP

- fråga

- problem

- IT

- Large

- storskalig

- leda

- ledande

- Nivå

- ansvar

- livet

- lokal

- längre

- gjord

- bibehålla

- GÖR

- Framställning

- ledning

- Marginal

- Marknader

- max-bredd

- metoder

- Mildra

- förmildrande

- begränsning

- modul

- Moduler

- mer

- mest

- flytta

- Natur

- behov

- nät

- nätverk

- Brus

- i synnerhet

- antal

- of

- Erbjudanden

- on

- ONE

- drift

- Verksamhet

- optimering

- optimerad

- optimera

- Övriga

- produktion

- del

- prestanda

- utför

- Fenomenet

- plattform

- plato

- Platon Data Intelligence

- PlatonData

- portfölj

- Inlägg

- potentiell

- kraft

- Strömförsörjning

- process

- bearbetning

- Processorn

- processorer

- Produkter

- leverantör

- ger

- höja

- område

- snabb

- snabbt

- Läsa

- realtid

- skäl

- Minskad

- reglering

- tillförlitlighet

- pålitlig

- Obligatorisk

- Svara

- respons

- resultera

- resulterande

- Rise

- Risk

- Körning

- Skala

- skalning

- HAV

- allvarlig

- inställning

- svår

- Skift

- Visar

- Signal

- signifikant

- signifikant

- mindre

- smarta

- lösning

- Lösningar

- några

- Utrymme

- sådana

- plötslig

- leverera

- stödja

- apt

- system

- System

- Tandem

- Teknologi

- terminologi

- den där

- Smakämnen

- Området

- deras

- Dem

- Dessa

- Genom

- tid

- gånger

- Tidpunkten

- till

- dagens

- alltför

- traditionell

- användning

- mycket varierande

- via

- Spänning

- VÄL

- ALLBEKANT

- som

- bred

- Brett utbud

- brett

- kommer

- med

- inom

- utan

- skulle

- zephyrnet