Pred dobrima dvema desetletjema je uvedba PCI Express 1.0 zaznamovala prehod industrije s takrat vseprisotnih vzporednih na serijske vmesnike. Leta 2002 je bil potencial »PCIe« v avtomobilskih aplikacijah nepredviden – glede na takratno stanje računalništva v vozilu in primarno osredotočenost PCIe na uporabo namizij in podatkovnih centrov. Vendar pa danes, s pojavom povezanih vozil s skoraj človeškimi (si upam reči nadčloveškimi?) samovozečimi sposobnostmi, je vprašanje "Zakaj vključiti PCIe v avtomobile zdaj?" in več "Zakaj je trajalo tako dolgo, da je avtomobilska industrija uporabila PCIe?"

Vsako leto smo priča vse večji kompleksnosti avtomobilske elektronike. Prilagodljivi tempomat (pri katerem vozilo prilagodi svojo hitrost, da vzdržuje nastavljeno razdaljo do vozila pred njim) je bil nedolgo nazaj ekskluziven za luksuzna vozila višjega razreda. Danes se to zdi nenavaden trik v svetu, kjer lahko družina srednjega razreda kupi avto, ki sam krmili v prometu in okoli njega, sam poišče in zasede parkirno mesto ter tam počaka, dokler ga lastnik ne pokliče. Količina senzorskih podatkov, posnetkov kamere in čiste računalniške moči za dosego tega je preprosto osupljiva, pri čemer nekateri raziskovalci izračunajo, da se pretok podatkov v enem vozilu približa 200 Gbps!

Zanesljivost je bila vedno temeljna zahteva za avtomobilske sisteme. Pretekli oglasi za avtomobile so hvalili sposobnost znamke, da vas varno pripelje do cilja, in potrošniki so se zgrinjali k vozilom, ki so več časa preživela na cesti kot v mehanični delavnici. Ker so potrošniki in njihove družine zdaj odvisni ne le od zmožnosti njihovega vozila, da še naprej deluje, ampak tudi od njegove sposobnosti sprejemanja kritičnih odločitev in izvajanja voznih podvigov, ki presegajo zmožnosti ljudi, poudarek na zanesljivosti še nikoli ni bil večji. Dodajanje toplote, ki jo proizvaja vsa ta napredna elektronika, k že tako zahtevni in hitro spreminjajoči se temperaturi, vlažnosti in vibracijam avtomobilskega okolja, je za avtomobilske oblikovalce zastrašujoča naloga. Potrošniki, ki sprejmejo ponovni zagon svojih pametnih telefonov zaradi občasnih "zrušitev", niso presenetljivo neprizanesljivi do istih napak v svoji avtomobilski elektroniki - kjer bi lahko rezultat zlahka bila resnična nesreča z ustrezno hudimi posledicami. Na žalost so ti isti potrošniki neradi sprejeli, da sta kibernetska kriminaliteta in »hekanje« vedno bolj neprijetna realnost njihovega vsakdana, a tudi tu so posledice veliko hujše od celo najbolj grozljive kraje identitete.

Tako je jasno, da sodobna vozila potrebujejo medsebojno povezavo z visoko pasovno širino, izjemno zanesljivostjo in robustno varnostjo – vse lastnosti, ki so skupne PCI Express 6.0!

Pasovna širina PCIe

Od svojega začetka je bil PCI Express osredotočen na zagotavljanje najsodobnejše pasovne širine, zato ne preseneča, da trenutna specifikacija PCIe 6.0 zagotavlja do 256 GB/s pri izvajanju najširših (x16) povezav pri najvišji (64GT) /s) razpoložljiva hitrost. Z opravičilom za še en davni avtomobilski oglas, novi način FLIT in signalizacija PAM4, definirana v PCIe 6.0, pomenita "PCIe 6.0 ni specifikacija PCI Express vašega očeta!" Z ohranjeno popolno združljivostjo za prejšnje generacije s prejšnjimi generacijami PCIe se novo signaliziranje PAM4 uporablja samo pri 64GT/s, tradicionalno signaliziranje NRZ pa ostaja v uporabi pri 32GT/s in manj. Izzivi pri ohranjanju sprejemljivih stopenj bitnih napak pri tej novi hitrosti so vodili do znatnih sprememb v protokolu PCIe, zaradi česar je morda še bolj privlačen za avtomobilske oblikovalce, ki se osredotočajo na zanesljivost.

Nova struktura FLIT (FLow control unIT) s fiksno velikostjo omogoča uporabo vnaprejšnjega popravljanja napak (FEC), ki izboljša efektivno stopnjo bitnih napak s popravljanjem več napak znotraj FLIT-a, preden podatke obdelajo klasični mehanizmi za obravnavo napak PCIe. Ta novi način FLIT je potreben, ko povezave PCIe delujejo pri 64GT/s, vendar je dovoljen pri kateri koli definirani hitrosti povezave PCIe. Medtem ko je bil razvoj PCIe FLIT potreben za popravljanje napak, je prijeten stranski učinek izboljšanje učinkovitosti povezave v mnogih primerih. S konsolidacijo obremenitev na paket v obremenitev na FLIT je mogoče več majhnih paketov prenesti znotraj enega samega FLIT še učinkoviteje kot v prejšnjih generacijah PCIe.

Naprave PCIe 6.0 lahko izkoristijo največjo možno pasovno širino, ne glede na to, ali delujejo pri najnovejši hitrosti povezave 64GT/s ali eni od nižjih hitrosti povezave, ki so še vedno v celoti opredeljene in podprte v osnovni specifikaciji PCIe 6.0.

Zanesljivost PCIe

PCIe že od svoje prve izdaje ponuja sam po sebi zanesljiv mehanizem dostave. Vsak paket PCIe vključuje ciklično preverjanje redundance na ravni povezave (LCRC), ki se preveri takoj po prejemu. Protokol ACK/NAK (Acknowledged/Not-Acknowledged) zagotavlja nemoten strojni ponovni prenos napačnih paketov in vključuje časovne omejitve, da se zagotovi, da prekinjene povezave ne ostanejo neopažene. Kot je navedeno zgoraj, ko povezava PCIe deluje v načinu FLIT, obstaja dodatna plast zaščite, zagotovljena z uporabo FEC, ki se uporabi in morebitne napake popravijo, še preden se preveri LCRC. Pakete, ki ne prestanejo teh preverjanj, sprejemnik NAK-a, oddajnik pa sproži samodejno ponovno pošiljanje. To strojno upravljanje prenosov podatkov razvijalcem programske opreme omogoča uporabo naprav, povezanih s PCIe, kot da bi bile neposredno povezane s CPE, ne da bi morali skrbeti za dostavo posameznih prenosov.

PCIe 6.0 vključuje funkcijo Lane Margining (predstavljeno s PCIe 4.0), ki zagotavlja standardiziran mehanizem za vse komponente PCIe, da poročajo o količini rezerve, ki jo imajo med "dobrimi" signali, ki jih prejemajo, in točko okvare. S to funkcijo je mogoče slediti morebitnemu poslabšanju kakovosti signala v življenjski dobi komponente in sprožiti proaktivno ublažitev napak, kot je ponovna nastavitev parametrov signalizacije, zmanjšanje hitrosti povezave ali celo poziv k preventivni zamenjavi komponente pred odpovedjo.

PCI Express ponuja možnost uporabe Vendor Defined Messages (VDM) za razširitev protokola PCIe na številne načine. Avtomobilski oblikovalci lahko uporabljajo te VDM za informacije o srčnem utripu, upravljanje znotraj pasu in številne druge funkcije, ki lahko prispevajo k zanesljivosti celotnega avtomobilskega sistema PCIe.

PCIe varnost

Na avtomobilskem področju lahko besedna zveza »varnost vmesnika« pričara vizije filmskih tajnih agentov, ki ubijajo zlobne genije tako, da vdrejo v svoje samovozeče avtomobile, da se zapeljejo s pečin in eksplodirajo na spektakularen način, vendar je v ozadju dejansko več scenarijev iz resničnega sveta. premaknite na varne povezave PCIe. V svetu, kjer so bili narodi ujeti pri uporabi kibernetskih napadov za motenje orožja drugih narodov, ne bi smeli popolnoma izključiti filmskega zapleta o "vdoru v vozilo za atentat", vendar bi veliko enostavnejša pridobitna motivacija kraje dala spretnim tatovom spodbudo za takšne hekanje. Ker so avtomobilski proizvajalci zaprli vedno več varnostnih ranljivosti v tradicionalnih protivlomnih mehanizmih, kot so radiofrekvenčni sistemi za daljinsko odklepanje, bodo morali tatovi nujno usmeriti svojo pozornost globlje v notranjost vozila, kjer bi lahko medsebojne povezave PCIe sicer postale privlačna točka napada. Pogosto spregledana je tudi zamisel o varnosti vmesnika za uveljavljanje upravljanja digitalnih pravic – kjer je »napadalec« lahko lastnik vozila z neomejenim časom in brezplačnim dostopom do »napadljenega« vozila, ki namerava odkleniti plačljive funkcije, kot je avtonomna vožnja .

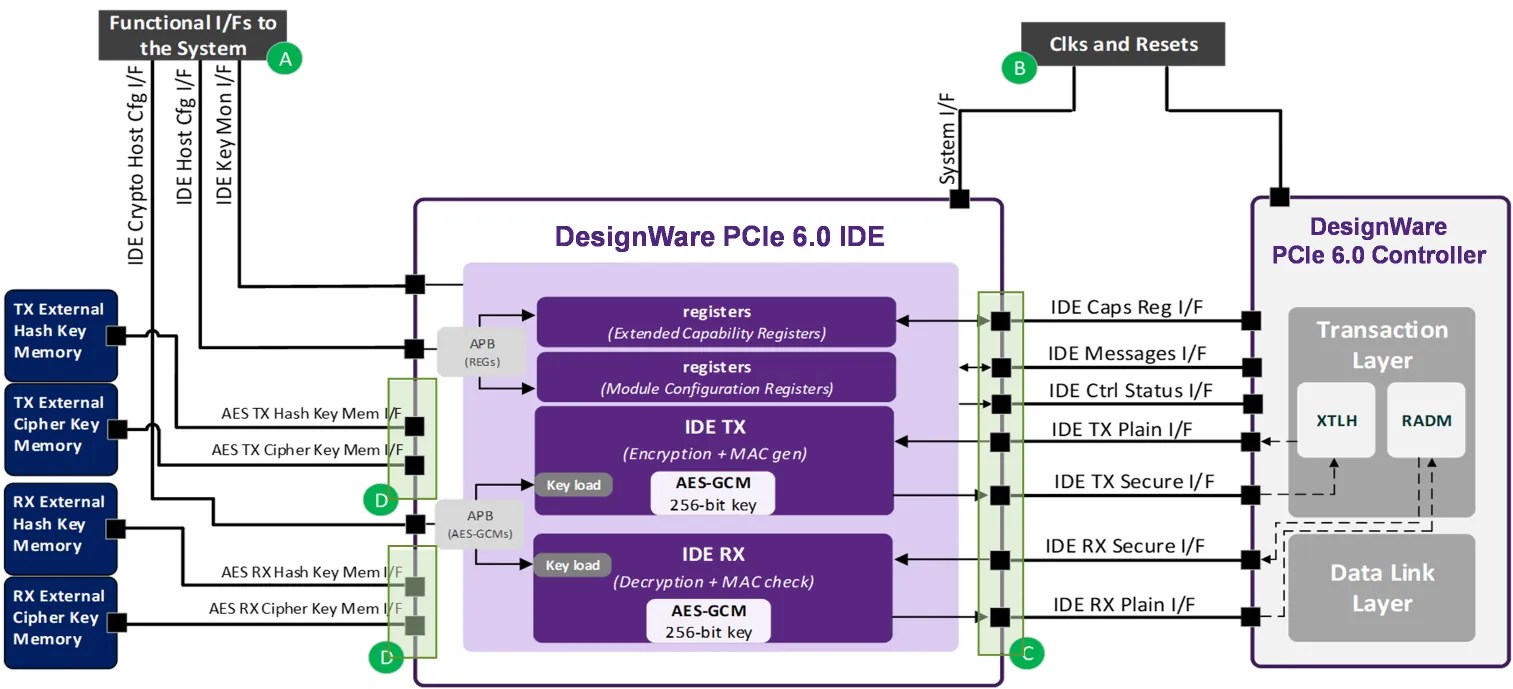

Ti in drugi dejavniki pomenijo, da morajo avtomobilski oblikovalci zdaj upoštevati vse svoje notranje vmesnike kot možne vektorje napadov. PCI Express vključuje funkcijo, imenovano Integrity and Data Encryption (IDE), ki napravam PCIe omogoča strojno šifriranje in preverjanje celovitosti paketov, prenesenih prek povezav PCIe. V bistvu IDE ščiti pred napadi na ravni strojne opreme, ki jih izvajajo usposobljeni napadalci s sofisticiranimi orodji in neposrednim dostopom do sistemov svojih žrtev. Paketi PCIe so posamično šifrirani in overjeni s kriptografskim algoritmom AES-GCM, da zagotovijo zaupnost in celovitost podatkov. Mehanizmi znotraj specifikacije IDE delujejo v celotnem skladu protokolov PCIe za zaščito pred napadi, specifičnimi za PCIe, kot je vsiljevanje ponovnih poskusov in vbrizgavanje slabih paketov pri poskusih vsiljevanja ponavljajočega se prenosa istih podatkov, da se razkrijejo uporabljeni kriptografski ključi. Zaradi teh interakcij protokolov na nizki ravni je treba IDE implementirati z roko v roki s krmilnikom PCIe, da bi v celoti izkoristili zaščitne mehanizme in zagotovili optimalne rešitve. Kot rezultat preverjanja celovitosti imajo povezave PCIe, zaščitene z IDE, še en sloj preverjanja zanesljivosti, saj bo celo nezlonamerna sprememba paketa PCIe, zaščitenega z IDE, sprožila odziv na sistemski ravni.

Slika 1: Primer implementacije Synopsys IDE znotraj krmilnika PCIe.

zaključek

Današnja povezana vozila se opirajo na računalniške platforme in arhitekture, ki zahtevajo medsebojne povezave z visoko pasovno širino, izjemno zanesljivostjo in robustno varnostjo. PCI Express 6.0 je edinstveno pozicioniran za izpolnjevanje teh zahtev s kombinacijo signalizacije do 64GT/s na stezo, številnih mehanizmov strojne opreme za zanesljivo dostavo in popolnega šifriranja podatkov s preverjanji integritete. Synopsys ponuja Krmilniki PCIe 6.0 in 5.0 z varnostnimi moduli IDE za pomoč oblikovalcem SoC pri zaščiti prenosov podatkov na PCIe pred posegi in fizičnimi napadi, skupaj z možnostmi za certifikate ISO 26262 in ASIL. Synopsys IP za PCI Express podpira vse te funkcije, da avtomobilskim oblikovalcem omogoči uporabo PCIe 6.0 v svojih naslednjih izdelkih.

Richard Salomon

Richard Solomon is the senior technical marketing manager for Synopsys’ DesignWare PCI Express Controller IP. He has been involved in the development of PCI chips dating back to the NCR 53C810 and pre-1.0 versions of the PCI spec. Prior to joining Synopsys, Solomon architected and led the development of the PCI Express and PCI-X interface cores used in LSI’s line of storage RAID controller chips. He has served on the PCI-SIG board of directors for more than 10 years, and is currently vice president of the PCI-SIG. He holds a BSEE from Rice University and 25 U.S. Patents, many of which relate to PCI technology.

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- PlatoData.Network Vertical Generative Ai. Opolnomočite se. Dostopite tukaj.

- PlatoAiStream. Web3 Intelligence. Razširjeno znanje. Dostopite tukaj.

- PlatoESG. Ogljik, CleanTech, Energija, Okolje, sončna energija, Ravnanje z odpadki. Dostopite tukaj.

- PlatoHealth. Obveščanje o biotehnologiji in kliničnih preskušanjih. Dostopite tukaj.

- vir: https://semiengineering.com/why-are-automotive-soc-designers-turning-to-pci-express-6-0/

- :ima

- : je

- :ne

- :kje

- $GOR

- 1

- 10

- 12

- 25

- 33

- a

- sposobnosti

- sposobnost

- O meni

- nad

- Sprejmi

- sprejemljiv

- sprejeta

- dostop

- doseganje

- čez

- dejansko

- prilagodljivo

- dodajanje

- Dodatne

- napredno

- Prednost

- prihod

- oglas

- spet

- proti

- agenti

- Avgust

- algoritem

- vsi

- Vse objave

- omogoča

- skupaj

- že

- Prav tako

- vedno

- znesek

- an

- in

- Še ena

- kaj

- privlačna

- aplikacije

- uporabna

- pristopi

- SE

- okoli

- AS

- At

- napad

- Napadi

- Poskusi

- pozornosti

- privlačen

- lastnosti

- overjena

- Samodejno

- automobile

- rabljena

- avtomobilska

- avtonomno

- Na voljo

- nazaj

- Slab

- pasovna širina

- baza

- BE

- postanejo

- bilo

- pred

- zadaj

- počutje

- spodaj

- koristi

- med

- Poleg

- Bit

- svet

- uprava

- Broken

- vendar

- by

- izračun

- se imenuje

- kliče

- kamera

- CAN

- kapaciteta

- voziček

- avtomobili

- primeri

- ujete

- center

- certificiranje

- izzivi

- izziv

- Spremembe

- spreminjanje

- preveriti

- preverjeno

- preverjanje

- Pregledi

- čipi

- klasična

- jasno

- zaprto

- združevanje

- Skupno

- združljivost

- popolnoma

- kompleksnost

- komponenta

- deli

- računanje

- računalniški

- računska moč

- poteka

- zaupnost

- povezane

- Posledice

- Razmislite

- utrjevanje

- Potrošniki

- prispevajo

- nadzor

- krmilnik

- popravljen

- bi

- CPU

- Crash

- kritično

- kriptografijo

- Trenutna

- Trenutno

- kibernetski napadi

- kibernetski kriminaliteti

- vsak dan

- datum

- Podatkovno središče

- dating

- desetletja

- odločitve

- globlje

- opredeljen

- dostavo

- dostava

- odvisno

- oblikovalci

- desktop

- destinacija

- Razvijalci

- Razvoj

- naprave

- DID

- digitalni

- digitalne pravice

- neposredna

- Neposreden dostop

- neposredno

- Direktorji

- Moti

- razdalja

- do

- pogon

- vožnjo

- 2

- enostavno

- Učinkovito

- učinkovitosti

- učinkovito

- Elektronika

- omogočajo

- šifriran

- šifriranje

- uveljaviti

- zagotovitev

- okolje

- Napaka

- napake

- Tudi

- Tudi vsak

- zlobni geniji

- Primer

- Ekskluzivno

- Razširi

- express

- ekstremna

- dejavniki

- FAIL

- Napaka

- družine

- družina

- daleč

- Moda

- Feature

- Lastnosti

- najdbe

- prva

- Pretok

- Osredotočite

- osredotočena

- za

- moč

- silijo

- Naprej

- brezplačno

- frekvenca

- iz

- spredaj

- Izpolnite

- polno

- v celoti

- funkcije

- temeljna

- v osnovi

- generacije

- dobili

- Daj

- dana

- Go

- taksist

- Ravnanje

- strojna oprema

- Imajo

- he

- pomoč

- tukaj

- visoka

- High-End

- več

- najvišja

- drži

- Vendar

- http

- HTTPS

- Ljudje

- i

- Ideja

- identiteta

- kraja identitete

- if

- takoj

- Izvajanje

- izvajali

- Izboljšanje

- izboljšuje

- in

- Spodbuda

- začetek

- vključuje

- vključi

- narašča

- individualna

- Posamezno

- Industrija

- industriji

- Podatki

- inherentno

- v notranjosti

- celovitost

- namen

- interakcije

- medsebojne povezave

- vmesnik

- vmesniki

- notranji

- v

- Uvedeno

- Predstavitev

- vključeni

- IP

- ISO

- IT

- ITS

- sam

- pridružil

- samo

- Imejte

- tipke

- Lane

- Zadnji

- plast

- Led

- manj

- življenje

- kot

- vrstica

- LINK

- Povezave

- živi

- Long

- nižje

- Luksuzni

- vzdrževati

- vzdrževanje

- Znamka

- IZDELA

- upravljanje

- upravitelj

- Proizvajalci

- več

- Marža

- označeno

- Trženje

- max širine

- Maj ..

- pomeni

- Mehanizem

- Mehanizmi

- sporočil

- morda

- ublažitev

- način

- sodobna

- več

- Najbolj

- Motivacija

- premikanje

- premakniti na varno

- Film

- veliko

- več

- morajo

- narodov

- NCR

- nujno

- Nimate

- nikoli

- Novo

- Naslednja

- št

- opozoriti

- zdaj

- številne

- občasno

- zaseda

- of

- off

- ponujen

- Ponudbe

- pogosto

- on

- ONE

- samo

- deluje

- deluje

- optimalna

- Možnost

- možnosti

- or

- Ostalo

- drugače

- ven

- več

- Splošni

- Lastnik

- paketi

- plačana

- vzporedno

- parametri

- parkiranje

- Patenti

- za

- opravlja

- PHP

- fizično

- Platforme

- platon

- Platonova podatkovna inteligenca

- PlatoData

- Točka

- pozicioniran

- mogoče

- Prispevkov

- potencial

- potencialno

- moč

- Predsednik

- prejšnja

- primarni

- Predhodna

- Proaktivna

- obdelani

- Proizvedeno

- Izdelki

- Dobiček

- zaščito

- zaščita

- varuje

- protokol

- zagotavljajo

- če

- zagotavlja

- nakup

- kakovost

- vprašanje

- radio

- RAID

- hitro

- Oceniti

- Cene

- resnični svet

- Reality

- kraljestvo

- prejema

- Zmanjšanje

- sprostitev

- zanesljivost

- zanesljiv

- zanašajo

- ostanki

- daljinsko

- ponovi

- zamenjava

- poročilo

- zahteva

- obvezna

- zahteva

- Zahteve

- raziskovalci

- Odgovor

- povzroči

- radiodifuzne retransmisije

- Riž

- pravice

- cesta

- robusten

- Pravilo

- tek

- s

- na žalost

- varno

- Enako

- zdrava pamet

- pravijo,

- scenariji

- brezšivne

- skrivnost

- zavarovanje

- Zavarovano

- varnost

- glej

- Zdi se,

- samo-vožnja

- višji

- senzor

- serijska

- služil

- nastavite

- huda

- Trgovina

- Signal

- signali

- pomemben

- preprosto

- saj

- sam

- spreten

- majhna

- pametne telefone

- So

- Software

- Razvijalci programske opreme

- rešitve

- nekaj

- prefinjeno

- Vesolje

- specifikacija

- spektakularen

- hitrost

- hitrosti

- porabljen

- sveženj

- osupli

- standardizirani

- Država

- state-of-the-art

- Še vedno

- shranjevanje

- Struktura

- taka

- Podprti

- Podpira

- presenečenje

- sistem

- sistemi

- Bodite

- Naloga

- tehnični

- Tehnologija

- kot

- da

- O

- Kraja

- njihove

- Tukaj.

- te

- jih

- ta

- tisti,

- vsej

- pretočnost

- čas

- do

- danes

- orodja

- Touted

- sledenje

- tradicionalna

- Prometa

- prenese

- transferji

- Prehod

- sprožijo

- OBRAT

- Obračalni

- dva

- nas

- pod

- nepredviden

- edinstveno

- Enota

- univerza

- neomejeno

- odklepanje

- dokler

- naprej

- uporaba

- Rabljeni

- uporabo

- Uporaben

- vozilo

- Vozila

- Prodajalec

- preverjeno

- vice

- Podpredsednica

- Žrtva

- vizije

- Ranljivosti

- čaka

- je

- načini

- we

- Orožje

- webp

- Dobro

- so bili

- kdaj

- ali

- ki

- medtem

- WHO

- zakaj

- bo

- z

- v

- brez

- delo

- svet

- skrbi

- bi

- bi dal

- leto

- let

- še

- jo

- Vaša rutina za

- zefirnet