Bilo je nazaj noter 1991 da je Cadence prvič objavil ime izdelka Virtuoso in tukaj smo 32 let kasneje in izdelek je živ in deluje precej dobro. Steven Lewis iz Cadence mi je sporočil nekaj novega, čemur pravijo Studio Virtuoz, in gre za oblikovanje IC po meri za resnični svet. V teh 32 letih smo bili priča koraku polprevodniškega procesa po Moorovem zakonu od 600 nm z uporabo planarnega CMOS, zmanjšanja do dobe FinFET pod 22 nm, doseganja GAA na 3 nm vozlišču. Jasno je, da so se zahteve orodja EDA spremenile, saj so manjša vozlišča prinesla nove fizične učinke, ki jih je bilo treba modelirati in simulirati, da se zagotovi prvi uspeh silicija.

Cadence Virtuoso Studio se osredotoča na pomoč oblikovalcem IC pri soočanju z današnjimi izzivi na šestih področjih:

- Povečana kompleksnost procesa

- Upravljanje z 10,000 s simulacijami vezij

- Avtomatizacija načrtovanja in migracija vezij

- Heterogena integracija

- AI

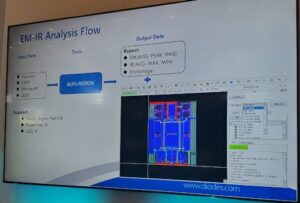

- Odjava, preverjanje in analiza med zasnovo

O Virtuozni ADE (Analog Design Environment) omogoča inženirjem vezja, da raziščejo svoje analogne, mešane signale in RFIC zasnove s pomočjo shematskega zajema in simulacije vezja. Arhitektura Virtuoso ADE je bila prenovljena za boljši nadzor opravil, zmanjšanje uporabe RAM-a in pospešitev simulacij z uporabo oblaka. Na primer, RAM, potreben za izvajanje Spectra na 10,000 s simulacijah, je bil zmanjšan s 420 MB na samo 18 MB za spremljanje simulacij, medtem ko so se ocene izrazov zmanjšale s 420 MB RAM-a na samo 280 MB.

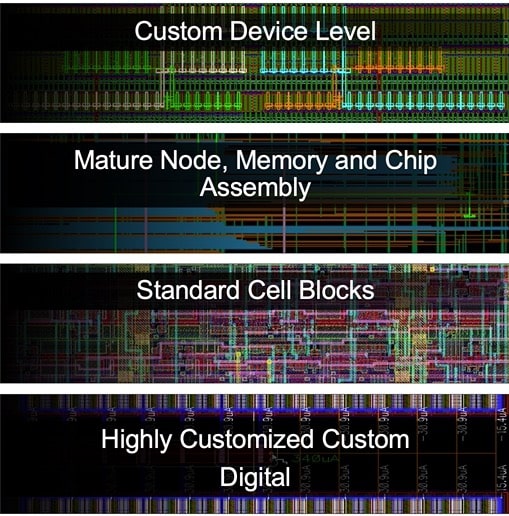

Posodobitve za Virtuoso Layout Suite vključujejo štiri izbire tehnologije kraja in poti, od katerih je vsaka prilagojena edinstveni nalogi v okolju Virtuoso:

Štiri tehnologije P&R

Pogoni DRC in LVS so del fizičnega preverjanja, njihovo izvajanje v paketnem načinu, popravljanje in ponavljanje pa vodi do dolgih razvojnih načrtov. Preverjanje v načrtu omogoča interaktivno uporabo DRC in LVS med delom na postavitvi IC, tako da so povratne informacije o tem, kaj spremeniti, hitro poudarjene, kar pospešuje produktivnost. Oblikovalec postavitve, ki uporablja zbirko Virtuoso Layout Suite, ima koristi od preverjanja v načrtovanju z uporabo Pegasus Tehnologija DRC in LVS.

Čipleti, 2.5D in 3D embalaža obsegajo tradicionalno ločena področja oblikovanja PCB, paketov in IC. Virtuoso Studio omogoča sooblikovanje in preverjanje paketov, modulov in IC-jev z:

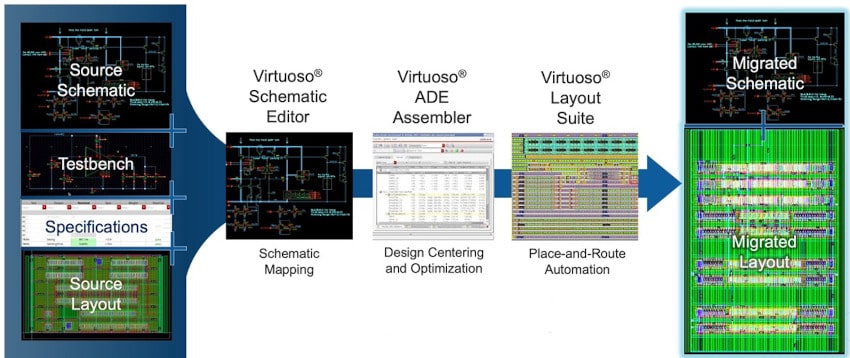

Če pogledamo v bližnjo prihodnost, lahko pričakujete, da se bodo pojavile podrobnosti o tem, kako se umetna inteligenca uporablja za samodejni prehod iz analogne sheme v postavitev na podlagi strojnega učenja in specifikacij. Te samodejno ustvarjene poskusne postavitve bodo dodatno pospešile delovno intenziven proces. Drugo razvojno področje za uporabo umetne inteligence je problem selitve analognega IP-ja po meri v novo procesno vozlišče. Ostani na vezi.

Prve stranke Virtuoso Studia vključujejo Analog Devices za sooblikovanje IC in paketa, vodilne potrošniške zasnove IC pri MediaTeku in migracijo procesov na osnovi AI pri Renesasu.

Povzetek

Virtuoso Studio je v izdajo 23.1 vključil nekaj impresivnih novih funkcij, ki jih lahko začnejo uporabljati oblikovalske skupine IC, da bodo bolj produktivne. Infrastruktura Virtuoso se je spremenila, da bi se soočila z izzivi Moorovega zakona, simulacije s simulacijami vezja 10,000 s so praktične, RFIC in modul 2.5D/3D sooblikovanja sta podprta, preverjanje DRC/LVS v zasnovi traja veliko manj časa in AI je ki se uporablja za avtomatizacijo analognih opravil.

Sorodni dnevniki

Delite to objavo prek:- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- Platoblockchain. Web3 Metaverse Intelligence. Razširjeno znanje. Dostopite tukaj.

- Kovanje prihodnosti z Adryenn Ashley. Dostopite tukaj.

- vir: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :ima

- : je

- $GOR

- 1

- 10

- 3d

- a

- O meni

- pospeševanje

- AI

- vsi

- omogoča

- skupaj

- in

- razglasitve

- uporabna

- Arhitektura

- SE

- OBMOČJE

- območja

- AS

- At

- avtomatizirati

- samodejno

- Avtomatizacija

- nazaj

- temeljijo

- BE

- bilo

- počutje

- spodaj

- Prednosti

- Boljše

- prinesel

- by

- Cadence

- klic

- CAN

- zajemanje

- izzivi

- spremenite

- možnosti

- jasno

- Cloud

- Potrošnik

- nadzor

- po meri

- Stranke, ki so

- dan

- zahteve

- Oblikovanje

- oblikovalec

- oblikovalci

- modeli

- Podrobnosti

- Razvoj

- naprave

- tem

- domen

- navzdol

- vsak

- Učinki

- omogoča

- Inženirji

- zagotovitev

- okolje

- Era

- vrednotenja

- Primer

- pričakovati

- raziskuje

- Lastnosti

- povratne informacije

- prva

- Osredotočite

- za

- štiri

- iz

- nadalje

- Prihodnost

- Go

- strani

- Imajo

- pomoč

- tukaj

- Poudarjeno

- Kako

- HTML

- HTTPS

- ICS

- Impresivno

- in

- vključujejo

- Infrastruktura

- interaktivno

- IP

- Job

- jpg

- dela

- zakon

- postavitev

- Interesenti

- učenje

- Lewis

- Long

- stroj

- strojno učenje

- marec

- max širine

- Srečati

- migracije

- način

- modul

- Moduli

- spremljanje

- več

- Ime

- Blizu

- potrebna

- Novo

- Nove funkcije

- Vozel

- vozlišča

- of

- on

- ONE

- paket

- pakete

- embalaža

- del

- fizično

- Kraj

- platon

- Platonova podatkovna inteligenca

- PlatoData

- Prispevek

- Praktično

- predstaviti

- problem

- Postopek

- Izdelek

- produktivno

- produktivnost

- dal

- hitro

- RAM

- dosegli

- pravo

- resnični svet

- Zmanjšana

- zmanjšanje

- sprostitev

- obvezna

- Pot

- Run

- tek

- skaliranje

- drugi

- glej podrobnosti

- polprevodnik

- ločena

- Silicij

- Simulacija

- SIX

- manj

- So

- nekaj

- Nekaj

- span

- specifikacije

- spekter

- hitrost

- Začetek

- bivanje

- studio

- uspeh

- apartma

- Podprti

- Bodite

- meni

- Naloga

- Naloge

- Skupine

- Tehnologija

- da

- O

- njihove

- te

- skozi

- čas

- do

- orodje

- tradicionalno

- sojenje

- edinstven

- Nadgradnja

- Uporaba

- uporaba

- Preverjanje

- preko

- Dobro

- Kaj

- medtem

- bo

- z

- deluje

- svet

- let

- zefirnet