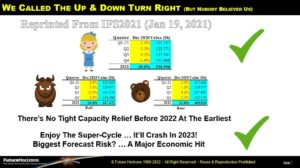

Mnoga verodostojna podjetja za analizo trga napovedujejo, da bo trg polprevodnikov v naslednjih šestih letih dosegel mejo bilijona dolarjev. Samo primerjajte to z več kot šestimi desetletji, ki so trajala, da je trg presegel mejo 500 milijard dolarjev. Predvidena stopnja rasti je res neverjetna in jo poganjajo hitro rastoči tržni segmenti, kot so visoko zmogljivo računalništvo (HPC), mobilne naprave, odjemalsko računalništvo in avtomobilska elektronika. Računalniško povpraševanje po sistemih prav tako narašča vsakih nekaj let z neverjetno hitrostjo. Izjemna rast sistemov, ki jih poganja umetna inteligenca (AI), in napredek v modelih globokega učenja nevronskih mrež sta zagotovo prispevala k temu in nas potegnila v »dobo SysMoore«. In multi-die sistemi postajajo bistveni za reševanje sistemskih zahtev SysMoore Era.

Glede na zgornje trende bo silicijev IP igral še pomembnejšo vlogo pri prihodnji rasti trga polprevodnikov. Včerajšnji standardni IP ne bo zmanjšal, ko gre za posebne zahteve PPA različnih aplikacij. Gre za diferenciran IP za posebne aplikacije in procese. V dobi SysMoore bi morala razvojna strategija IP temeljiti ne le na pričakovanju naslednjega vozlišča, temveč tudi na vertikalnih tržnih zahtevah, vodoravno (različice procesa) in nazaj, saj sistemi z več matricami omogočajo optimizacijo procesnih tehnologij.

Prejšnji teden Synopsys je napovedal razširjeno pogodbo s Samsung Foundry za razvoj širokega portfelja intelektualne lastnine za zmanjšanje tveganja oblikovanja in pospešitev uspeha silicija za avtomobilske, mobilne trge in trge HPC ter zasnove z več matricami. Imel sem priložnost poklepetati z Johnom Koeterjem, višjim podpredsednikom produktnega upravljanja in strategije za IP pri Synopsys. Moja razprava je bila osredotočena na razumevanje tega, kako je ta sporazum drugačen, in pomembno vlogo, ki so jo imeli podprti tržni segmenti in trend sistemov z več matricami pri doseganju razširjenega sporazuma. Sledi sinteza moje razprave s poudarkom na bistvenih točkah.

Proaktivno sodelovanje z upoštevanjem potreb vertikalnega trga

Synopsys in Samsung Foundry imata dolgo zgodovino sodelovanja, ko gre za razvoj IP. Splošno gledano je razvoj intelektualne lastnine v preteklosti vodilo specifično medsebojno povpraševanje strank. Glede na skrajšano povpraševanje po času do trga SysMoore Era si stranke ne morejo privoščiti čakanja na dolge razvojne cikle po specifičnih zahtevah IP. Razvoj intelektualne lastnine se mora začeti proaktivno na podlagi predvidevanja prihodnjega vertikalnega trga. In to počneta Synopsys in Samsung Foundry v skladu s tem razširjenim sporazumom. Analizirali bodo tržne segmente in razvili potreben IP za celostno obravnavanje vertikalnih tržnih potreb. Na primer, skupaj bodo razmislili o tem, kako bo izgledal ADAS čip naslednje generacije ali MCU naslednje generacije ali mobilni čip naslednje generacije, in proaktivno razvili IP za reševanje teh potreb. IP bo optimiziran tudi glede na potrebe končne aplikacije. Na primer, PCIe IP za trg HPC bo optimiziran za minimalno možno zakasnitev, medtem ko bo PCIe IP za avtomobilski trg optimiziran za zanesljivost v širšem temperaturnem območju.

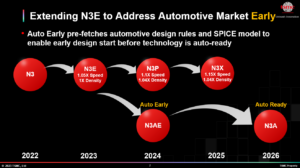

Konkretno za avtomobilski trg bo Synopsys optimiziral IP za Samsungova avtomobilska procesna vozlišča 8LPU, SF5A in SF4A, da bodo izpolnili stroge zahteve glede temperature 1. ali 2. stopnje in zanesljivosti AEC-Q100. Samodejni IP za ADAS SoC bo vključeval poročila o načinu načrtovanja napak in analizi učinkov (DFMEA), ki lahko prihranijo mesece truda pri razvoju avtomobilskih aplikacij SoC.

Predvidevanje sistemskih zahtev z več vložki

Ko se implementacije monolitnih čipov umaknejo implementacijam sistemov z več čipi, ne gre več le za naslednje napredno procesno vozlišče. Sistem z več matricami bi lahko imel različne matrice v različnih procesnih vozliščih in še vedno zagotavljal zahteve glede zmogljivosti in moči po nižji ceni v primerjavi z monolitno izvedbo. To odpira priložnost za razmislek o ustvarjanju naprednega IP-ja (recimo PCIe Gen6) za starejša procesna vozlišča za podporo I/O chipletov sistema z več die. Synopsys in Samsung proaktivno razmišljata o takšnih priložnostih in bosta razvila portfelj naprednega IP-ja na številnih procesnih vozliščih ter sodelovala pri razvoju hitrega IP-ja UCIe za komunikacijo čip-čip.

Razširitev sporazuma, ki vodi do povečanja IP odtisa

Kot rezultat zgoraj opredeljenih strategij sodelovanja IP se bo razpoložljivost IP za procese Samsung Foundry znatno povečala. Za stranke je to pomemben vzpon v smislu dostopa do IP v dobi po covidu, ko so jasne dobavne verige visoko na njihovem seznamu zahtev. S to pogodbo Synopsys IP, ki je na voljo ali je v razvoju za procese Samsung, vključuje logične knjižnice, vdelane pomnilnike, TCAM, GPIO, eUSB2, USB 2.0/3.0/3.1/4.0, USB-C/DisplayPort, PCI Express 3.0/4.0/5.0/6.0 , 112G Ethernet, Multi-Protocol 16G/32G PHYs, UCIe, HDMI 2.1, LPDDR5X/5/4X/4, DDR5/4/3, SD3.0/eMMC 5.1, MIPI C/D PHY in MIPI M-PHY G4 /G5.

Certificirani tokovi oblikovanja podjetja Synopsys pospešujejo čas do uspeha Silicija

Širok portfelj intelektualne lastnine enega samega prodajalca ima več prednosti, tako v poslovnem kot inženirskem smislu. Z inženirskega vidika bodo na primer neusklajenosti električnega omrežja ali lokacije nožic pri integraciji različnih blokov IP manj verjetne. Synopsys prav tako zelo tesno sodeluje s Samsungom na strani EDA pri razvoju in certificiranju različnih referenčnih tokov, ki naj bi pomagali pospešiti čas do uspeha silicija.

Če želite prebrati celotno sporočilo za javnost, kliknite tukaj. Za več informacij se obrnite na Synopsys.

Preberite tudi:

Zahteve za uspeh sistema Multi-Die

Avtomatizirana metoda za zagotavljanje, da so načrti odporni na napake na terenu

Delite to objavo prek:

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- EVM Finance. Poenoten vmesnik za decentralizirane finance. Dostopite tukaj.

- Quantum Media Group. IR/PR ojačan. Dostopite tukaj.

- PlatoAiStream. Podatkovna inteligenca Web3. Razširjeno znanje. Dostopite tukaj.

- vir: https://semiwiki.com/ip/330636-synopsys-expands-agreement-with-samsung-foundry-to-increase-ip-footprint/

- :ima

- : je

- :ne

- $GOR

- 1

- 300

- 500

- a

- O meni

- nad

- pospeši

- dostop

- Po

- ADA

- Naslov

- napredno

- napredek

- Prednosti

- po

- starost

- Sporazum

- AI

- vsi

- Prav tako

- an

- Analiza

- analizirati

- in

- razglasitve

- predvidevanje

- uporaba

- aplikacije

- SE

- prihod

- umetni

- Umetna inteligenca

- Umetna inteligenca (AI)

- AS

- At

- Avtomatizirano

- avtomobilska

- razpoložljivost

- Na voljo

- temeljijo

- BE

- postajajo

- bilo

- Billion

- Bloki

- tako

- široka

- poslovni

- vendar

- by

- CAN

- ne more

- Zagotovo

- Certified

- overiti

- verige

- čip

- jasno

- klik

- stranke

- tesno

- sodelovati

- sodelovanje

- prihaja

- Komunikacija

- primerjate

- v primerjavi z letom

- Izračunajte

- računalništvo

- Razmislite

- upoštevamo

- kontakt

- prispevali

- strošek

- bi

- par

- Ustvarjanje

- verodostojno

- kritično

- Cross

- stranka

- Stranke, ki so

- Cut

- ciklov

- desetletja

- globoko

- globoko učenje

- poda

- Povpraševanje

- zahteve

- Oblikovanje

- modeli

- Razvoj

- razvoju

- Razvoj

- drugačen

- razlikovati

- Razprava

- tem

- Dollar

- vozi

- učinek

- prizadevanje

- Elektronika

- vgrajeni

- omogočajo

- konec

- Inženiring

- zagotovitev

- Era

- bistvena

- Tudi

- Tudi vsak

- Primer

- razširiti

- širi

- Širitev

- express

- Napaka

- FAST

- podjetja

- Tokovi

- osredotočena

- po

- Odtis

- za

- Naprej

- Livarstvo

- iz

- polno

- Prihodnost

- prihodnjo rast

- splošno

- generacija

- Daj

- dana

- dogaja

- razred

- Mreža

- Pridelovanje

- Rast

- imel

- Imajo

- pomoč

- visoka

- High Performance Computing

- poudarjanje

- zgodovina

- Kako

- hpc

- HTTPS

- i

- identificirati

- Izvajanje

- Pomembno

- in

- vključujejo

- vključuje

- Povečajte

- Neverjetno

- Podatki

- primer

- Povezovanje

- Intelligence

- v

- IP

- IT

- John

- jpg

- samo

- Latenca

- vodi

- učenje

- manj

- knjižnice

- kot

- Verjeten

- Seznam

- kraj aktivnosti

- Logika

- Long

- več

- Poglej

- izgleda kot

- si

- upravljanje

- več

- znamka

- Tržna

- Analiza trga

- Prisotnost

- max širine

- MCU

- Srečati

- spomini

- Metoda

- minimalna

- Mobilni

- način

- modeli

- Monolit

- mesecev

- več

- več

- vzajemno

- my

- potrebna

- potrebe

- mreža

- Nevronski

- nevronska mreža

- Naslednja

- Naslednja generacija

- št

- Vozel

- vozlišča

- of

- starejši

- on

- samo

- Odpre

- Priložnosti

- Priložnost

- optimizacija

- Optimizirajte

- optimizirana

- or

- več

- preteklosti

- performance

- perspektiva

- platon

- Platonova podatkovna inteligenca

- PlatoData

- Predvajaj

- igral

- točke

- Portfelj

- mogoče

- Prispevek

- moč

- Električno omrežje

- napovedovanje

- Predsednik

- Postopek

- Procesi

- Izdelek

- upravljanje izdelkov

- napovedane

- območje

- Oceniti

- Cene

- dosežejo

- Preberi

- zmanjša

- Zmanjšana

- sprostitev

- zanesljivost

- Poročila

- zahteva

- Zahteve

- povzroči

- Tveganje

- vloga

- Samsung

- Shrani

- pravijo,

- segmentih

- polprevodnik

- višji

- shouldnt

- strani

- pomemben

- bistveno

- Silicij

- sam

- SIX

- So

- gledano

- specifična

- Začetek

- Še vedno

- strategije

- Strategija

- uspeh

- taka

- dobavi

- Napajalne verige

- podpora

- Podprti

- sistem

- sistemi

- Tehnologije

- Pogoji

- kot

- da

- O

- Prihodnost

- njihove

- jih

- ta

- tisti,

- čas

- do

- skupaj

- vzel

- ogromno

- Trend

- Trends

- Bilijona

- razumevanje

- us

- usb

- različnih

- Prodajalec

- vertikalno

- zelo

- preko

- Podpredsednica

- Počakaj

- je

- način..

- teden

- Dobro

- Kaj

- kdaj

- medtem ko

- ki

- širše

- bo

- z

- deluje

- let

- zefirnet