To je zanimiva ideja, ki uporablja špekulativni paralelizem, podprt s strojno opremo, za pospešitev simulacije, s preobratom, ki zahteva strojno opremo po meri. Paul Cunningham (višji podpredsednik/generalni direktor, preverjanje pri Cadence), Raúl Camposano (silicijev katalizator, podjetnik, nekdanji tehnični direktor Synopsysa in zdaj tehnični direktor Silvaca) in jaz nadaljujemo našo serijo raziskovalnih idej. Kot vedno so povratne informacije dobrodošle.

Inovacije

Izbira tega meseca je Chronos: Učinkovit špekulativni paralelizem za pospeševalnike. Avtorji so članek predstavili na konferenci o arhitekturni podpori za programske jezike in operacijske sisteme leta 2020 in so iz MIT.

Izkoriščanje paralelizma z uporabo večjedrnih procesorjev je ena od možnosti za aplikacije, kjer je vzporednost samoumevna. Drugi algoritmi morda ne bodo tako zlahka razdeljeni, vendar bi lahko imeli koristi od špekulativnega izvajanja, ki izkorišča intrinzični paralelizem. Običajno je špekulativna izvedba odvisna od koherence predpomnilnika, kar je veliko dodatnih stroškov, zlasti pri simulaciji. Ta metoda zaobide potrebo po skladnosti in fizično lokalizira izvajanje nalog za izračun ploščic s ciljnim objektom za branje in pisanje, kar zagotavlja, da je zaznavanje konfliktov mogoče zaznati lokalno, brez potrebe po globalnem upravljanju skladnosti. Naloge se lahko špekulativno izvajajo vzporedno; kakršen koli zaznan konflikt je mogoče odviti iz opravila prek njegovih podrejenih opravil, nato pa jih znova izvesti, ne da bi morali zaustaviti druge niti.

Tukaj je še ena točka. Ta metoda podpira simulacijo na podlagi zakasnitve, za razliko od večine tehnik pospeševanja strojne opreme.

Pavlov pogled

Vau, kako čudovit visokooktanski papir iz MIT! Ko me vprašajo o vzporednem računanju, takoj pomislim na niti, mutekse in koherenco pomnilnika. Tako so seveda zasnovani sodobni večjedrni procesorji. Vendar to ni edini način za podporo paralelizaciji v strojni opremi.

Ta članek predlaga alternativno arhitekturo za paralelizacijo, imenovano Chronos, ki temelji na urejeni čakalni vrsti opravil. Med izvajanjem se opravila izvajajo v vrstnem redu časovnega žiga in vsako opravilo lahko ustvari nova podnaloga, ki se dinamično dodajajo v čakalno vrsto. Izvajanje se začne s postavitvijo nekaterih začetnih opravil v čakalno vrsto in se konča, ko v čakalni vrsti ni več opravil.

Naloge v čakalni vrsti so vzporedno posredovane več procesnim elementom (PE) – kar pomeni, da Chronos špekulativno izvaja prihodnje naloge, preden je trenutna naloga dokončana. Če trenutno opravilo razveljavi morebitna špekulativno izvedena prihodnja opravila, so dejanja teh prihodnjih opravil »razveljavljena« in so ponovno postavljena v čakalno vrsto. Pravilna implementacija tega koncepta v strojno opremo ni enostavna, vendar je za zunanjega uporabnika čudovita: svoj algoritem samo kodirate, kot da se čakalna vrsta opravil zaporedno izvaja na enem PE. Ni vam treba kodirati nobenih muteksov ali skrbeti za zastoj.

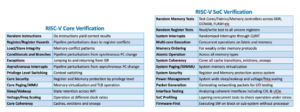

Avtorji implementirajo Chronos v SystemVerilog in ga prevedejo v FPGA. Velik del prispevka je posvečen razlagi, kako so implementirali čakalno vrsto opravil in kakršno koli potrebno odvijanje v strojni opremi za največjo učinkovitost. Chronos se primerja s štirimi algoritmi, ki so zelo primerni za arhitekturo, ki temelji na čakalni vrsti opravil. Vsak algoritem je implementiran na dva načina: prvič z uporabo posebnega PE, specifičnega za algoritem, in drugič z uporabo standardnega odprtokodnega 32-bitnega vdelanega CPU RISC-V kot PE. Zmogljivost Chronosa se nato primerja z večnitnimi programskimi implementacijami algoritmov, ki se izvajajo na strežniku Intel Xeon s podobno ceno kot FPGA, ki se uporablja za Chronos. Rezultati so impresivni – Chronos se meri od 3x do 15x bolje kot pri uporabi strežnika Xeon. Vendar pa me ob primerjavi tabele 3 s sliko 14 nekoliko skrbi, da je večina teh dobičkov prišla iz PE-jev, specifičnih za algoritem, in ne iz same arhitekture Chronos.

Glede na to, da je to spletni dnevnik za preverjanje, sem seveda povečal merilo uspešnosti simulacije na ravni vrat. Industrija EDA je veliko vložila v poskus vzporedne logične simulacije in izkazalo se je, da je težko videti velike dobičke, ki presegajo nekaj posebnih primerov uporabe. To je predvsem posledica delovanja večine simulacij v resničnem svetu, kjer prevladujejo navodila za nalaganje/shranjevanje, ki manjkajo v predpomnilniku L3 in gredo v DRAM. V tem prispevku je primerjal samo en testni primer in to je majhen 32-bitni seštevalnik za shranjevanje. Če berete ta blog in bi vas zanimala podrobnejša primerjalna analiza, mi prosim sporočite – če bi se lahko Chronos resnično dobro prilagodil simulacijam resničnega sveta, bi to imelo veliko komercialno vrednost!

Raúlov pogled

Glavni prispevek tega prispevka je Model izvajanja prostorsko lociranih urejenih nalog (SLOT). ki je učinkovit za pospeševalnike strojne opreme, ki izkoriščajo vzporednost in špekulacije, ter za aplikacije, ki dinamično ustvarjajo naloge med izvajanjem. Podpora za dinamični paralelizem je neizogibna za simulacijo in špekulativna sinhronizacija je privlačna možnost, vendar so stroški koherence previsoki.

SLOT se izogne potrebi po skladnosti tako, da vsako nalogo omeji na delovanje (pisanje) na enem objektu in podpira urejena opravila, da omogoči atomičnost več objektov. Aplikacije SLOT so urejena, dinamično ustvarjena opravila, za katera sta značilna časovni žig in id objekta. Časovni žigi določajo omejitve naročila; ID-ji objektov določajo odvisnosti podatkov, tj. naloge so odvisne od podatkov, če in samo če imajo isti ID objekta. (če obstaja odvisnost od branja, se lahko naloga izvede špekulativno). Zaznavanje konfliktov postane lokalno (brez zapletenih sledilnih struktur) s preslikavo ID-jev objektov v jedra ali ploščice in pošiljanjem vsake naloge tja, kjer je preslikan ID objekta.

O Chronos Sistem je bil implementiran v ogrodju AWS FPGA kot sistem s 16 ploščicami, vsaka s 4 aplikacijsko specifičnimi procesnimi elementi (PE), ki delujejo na 125MHz. Ta sistem se primerja z osnovno linijo, ki jo sestavlja 20-jedrni/40-nitni 2.4 GHz Intel Xeon E5-2676v3, izbran posebej, ker je njegova cena primerljiva s FPGA (približno 2 USD/uro). Z izvajanjem ene same naloge na enem PE je Chronos 2.45-krat hitrejši od izhodišča. Ko se število sočasnih nalog poveča, se izvedba Chronos poveča na samo-relativno pospešitev 44.9x na 8 ploščicah, kar ustreza 15.3x pospešitvi v primerjavi z izvedbo CPE. Primerjali so tudi izvedbo, ki temelji na RISC-V splošnega namena in ne na specifičnih aplikacijah PE; PE so bili 5x hitrejši od RISC-V.

Prispevek se mi je zdel impresiven, ker zajema vse od koncepta do definicije izvedbenega modela SLOT do izvedbe strojne opreme in podrobne primerjave s tradicionalnim CPE Xeon za 4 aplikacije. Prizadevanje je precejšnje, Chronos ima več kot 20,000 vrstic SystemVerilog. Rezultat je 5.4-kratna povprečna (od 4 aplikacij) pospešitev v primerjavi s programsko vzporednimi različicami zaradi večje vzporednosti in večje uporabe špekulativnega izvajanja. Prispevek je vreden branja tudi za uporabo pri nesimulacijskih nalogah; prispevek vključuje tri primere.

Delite to objavo prek:

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- Platoblockchain. Web3 Metaverse Intelligence. Razširjeno znanje. Dostopite tukaj.

- vir: https://semiwiki.com/eda/326261-speculation-for-simulation-innovation-in-verification/

- : je

- 000

- 2020

- 8

- a

- O meni

- pospeši

- pospešek

- pospeševalniki

- ACM

- dejavnosti

- dodano

- algoritem

- algoritmi

- alternativa

- vedno

- in

- privlačna

- uporaba

- specifično za aplikacijo

- aplikacije

- architectural

- Arhitektura

- SE

- AS

- At

- Avtorji

- AWS

- temeljijo

- Izhodišče

- BE

- lepa

- ker

- postane

- pred

- počutje

- merilo

- primerjalno

- koristi

- Boljše

- Poleg

- Big

- Bit

- Blog

- by

- predpomnilnik

- Cadence

- se imenuje

- CAN

- opravlja

- primeri

- Katalizator

- značilna

- otrok

- izbran

- Koda

- komercialna

- primerljiva

- v primerjavi z letom

- primerjavo

- Primerjava

- Končana

- kompleksna

- računanje

- Izračunajte

- Koncept

- sočasno

- Konferenca

- konflikt

- Sestavljeno

- omejitve

- naprej

- Prispevek

- Ustrezno

- Tečaj

- prevleke

- CPU

- ustvarjajo

- ustvaril

- CTO

- Trenutna

- po meri

- datum

- namenjen

- Odvisnost

- odvisno

- zasnovan

- podrobno

- Zaznali

- Odkrivanje

- težko

- dinamično

- dinamično

- e

- vsak

- enostavno

- učinkovitosti

- učinkovite

- prizadevanje

- elementi

- vgrajeni

- omogočajo

- konča

- zagotoviti

- Podjetnik

- zlasti

- vse

- Primeri

- izvršiti

- izvršitve

- izvedba

- pojasnjujejo

- Izkoristite

- hitreje

- povratne informacije

- Nekaj

- Slika

- prva

- za

- Nekdanji

- je pokazala,

- FPGA

- Okvirni

- iz

- Prihodnost

- zaslužek

- splošno

- ustvarjajo

- GHz Intel

- Globalno

- dogaja

- strojna oprema

- Imajo

- močno

- tukaj

- visoka

- Kako

- Vendar

- HTTPS

- velika

- i

- ID

- Ideja

- Ideje

- takoj

- izvajati

- Izvajanje

- izvajali

- izvajanja

- Impresivno

- in

- vključuje

- Poveča

- Industrija

- neizogibno

- začetna

- Inovacije

- Navodila

- Intel

- zainteresirani

- Zanimivo

- intrinzično

- investirali

- IT

- ITS

- sam

- Vedite

- jeziki

- linije

- lokalna

- lokalno

- nahaja

- Glavne

- IZDELA

- upravljanje

- kartiranje

- max širine

- največja

- pomeni

- Spomin

- Metoda

- morda

- manjka

- MIT

- Model

- sodobna

- več

- Najbolj

- več

- potrebno

- Nimate

- Novo

- Številka

- predmet

- of

- on

- ONE

- odprite

- open source

- deluje

- deluje

- Operacijski sistemi

- Možnost

- Da

- Ostalo

- zunaj

- P&E

- Papir

- vzporedno

- paul

- performance

- Fizično

- kramp

- platon

- Platonova podatkovna inteligenca

- PlatoData

- prosim

- Točka

- Prispevek

- predstavljeni

- Cena

- obravnavati

- procesorji

- Programiranje

- programskih jezikov

- predlaga

- dokazano

- Namen

- Dajanje

- precej

- Preberi

- reading

- pravo

- resnični svet

- Raziskave

- omejujoč

- povzroči

- Rezultati

- tek

- Enako

- Shrani

- Lestvica

- luske

- drugi

- pošiljanja

- višji

- Serija

- Rok

- Silicij

- Podoben

- Simulacija

- sam

- So

- Software

- nekaj

- vir

- specifična

- posebej

- špekulacije

- precejšen

- podpora

- Podpira

- Sinhronizacija

- sistem

- sistemi

- miza

- TAG

- ciljna

- Naloga

- Naloge

- tehnike

- da

- O

- te

- 3

- skozi

- Časovni žig

- do

- tudi

- Sledenje

- tradicionalna

- Twist

- uporaba

- uporabnik

- navadno

- Preverjanje

- preko

- način..

- načini

- dobrodošli

- Dobro

- Kaj

- ki

- z

- brez

- Čudovit

- svet

- vredno

- bi

- pisati

- Vaša rutina za

- zefirnet