Z vedno večjim številom podjetij, ki se zanimajo za naprave, ki temeljijo na RISC-V ISA, in vedno večjim številom jeder, pospeševalnikov in infrastrukturnih komponent, ki so na voljo bodisi komercialno bodisi v odprtokodni obliki, se končni uporabniki soočajo z vedno težjim izzivom zagotavljanje najboljše izbire.

Vsak uporabnik bo verjetno imel nabor potreb in pomislekov, ki so skoraj enaki prilagodljivosti ponudbe RISC-V, ki segajo daleč onkraj tradicionalnih meritev PPA v pomisleke glede varnosti in varnosti ali vprašanja kakovosti. To bi lahko vključevalo prilagodljivost zavarovanja za preverjanje, ki omogoča arhitekturno razširitev in potrebno preverjanje, ki jo spremlja.

Tradicionalno so bile uporabljene tri ravni izdelave prototipov — virtualni prototipi, emulacija in prototipi FPGA, vključno s hibridi med njimi. Vsaka platforma se nato uporablja za različne namene, vključno s preverjanjem programske opreme, arhitekturnim preverjanjem, funkcionalnim preverjanjem strojne opreme, analizo zmogljivosti in več.

Medtem ko se ekosistemi načrtovanja in programske opreme za RISC-V vzpostavljajo, ekosistemi konfiguracije in preverjanja zaostajajo in zahtevajo izgradnjo nove tehnologije. Prilagodljivost RISC-V je tista, ki ustvarja ogromne izzive za preverjanje, ki presega vse, kar je potrebno za preverjanje fiksnih procesorjev. Omogoča tudi skupen razvoj strojne in programske opreme, ne le mogoč, ampak tudi nujen.

Sorazvoj

V preteklosti je bila izbrana strojna oprema in nato razvita programska oprema za delovanje na njej. Pri RISC-V strojno opremo pogosto poganja programska oprema. "Prva stvar, ki jo morate izbrati, je, katere standardne možnosti RISC-V želite," pravi Simon Davidmann, ustanovitelj in izvršni direktor za Programska oprema Imperas. »Nabor funkcij RISC-V ima trenutno 200 ali 300 možnosti. Kako veste, ali bi vašemu algoritmu koristila enota s plavajočo vejico ali SIMD, strojni multiplikatorji ali celo vektorski motor? Izdelati morate zmogljivosti strojne opreme, ki jih boste potrebovali in si jih lahko privoščite za vrsto aplikacije ali naloge, za katero želite, da ta procesor opravlja. To samo po sebi postane majhen izziv.”

Za tovrstne kompromise so potrebni prototipi. »Če je cilj oblikovalca oceniti zmogljivost in ustreznost namenu, potem je virtualni prototip edina izvedljiva izbira,« pravi Steve Roddy, CMO pri Quadric. »Izdelava prototipov strojne opreme je več kot 10- do 50-krat zamudnejša kot izdelava modela SystemC podsistema ali celotnega SoC. Virtualni prototip SystemC na splošno deluje dovolj hitro, da odgovori na vprašanja o zmogljivosti, na primer, koliko sličic na sekundo prepustnosti lahko dobim s tem procesorskim jedrom ali kakšna je najvišja in povprečna pasovna širina, ki jo zahteva funkcija X, znotraj sprejemljive ovojnice natančnosti.«

Doseganje prave natančnosti je lahko težko. »Gre za natančnost in vašo sposobnost, da zelo hitro zavrtite model,« pravi Frank Schirrmeister, podpredsednik za rešitve in poslovni razvoj pri Arteris IP. »Prava natančnost je opredeljena s kakršnimi koli zahtevami vašega vprašanja in njihovo ustvarjanje ni nepomembno. Če ste ponudnik ASIP, jih boste lahko ustvarili iz katere koli predloge, ki jo imate. Odvisno od vprašanja boste morda potrebovali natančnost cevovoda, morda boste potrebovali natančnost pomnilnika, ni nujno, da je popolnoma natančen, toda ko imate vključen oddelek za CAD, se preveč bojijo odgovoriti na napačno vprašanje.«

Toda natančnost je kompromis v primerjavi s hitrostjo. »Medtem ko so nekateri virtualni prototipi ciklično natančni, ti pogosto delujejo prepočasi, da bi lahko imeli potrebno prepustnost programske opreme,« pravi Davidmann iz Imperasa. »Najbolj zmogljivi virtualni prototipi niso zmogljivi motorji, ker ne modelirajo procesorskih cevovodov. Na to gledajo z vidika programske opreme, kjer jo lahko prevedete in izvajate na strojni opremi, približno zmogljivost pa lahko vidite tako, da pogledate število navodil ali približne ocene časa. To bi moralo zadostovati za takšno arhitekturno odločitev.«

Pogosto je potrebnih več prototipov. »Prototipe običajno izdelujemo iz dveh razlogov,« pravi Venki Narayanan, višji direktor za programsko opremo in sistemski inženiring v poslovni enoti FPGA podjetja Microchip Technology. »Eden je za validacijo arhitekture, da zagotovimo, da izpolnjujemo vse metrike in zahteve glede učinkovitosti ter funkcionalno validacijo. Drugi razlog je razvoj vgrajene programske opreme in vdelane programske opreme. Uporabljamo različne ravni tehnik izdelave prototipov, pri čemer je najpogostejša uporaba lastnih FPGA za razvoj emulacijske platforme za arhitekturno in funkcionalno validacijo. Uporabljamo tudi arhitekturne modele, kot je QEMU, za gradnjo virtualnih platform tako za validacijo zmogljivosti kot za razvoj vgrajene programske opreme.«

Število možnosti narašča. »Podjetja danes na veliko načinov izdelujejo prototipe z RISC-V,« pravi Mark Himelstein, tehnični direktor za RISC-V International. »Ti segajo od računalnikov z eno ploščo na ravni izdelovalca do plošč za podjetja, ki podpirajo LINUX. Emulacijska okolja (kot je QEMU) omogočajo razvijalcem, da napredujejo s programsko opremo, preden je njihova strojna oprema dokončana, in povsod so že pripravljeni deli, od vdelanih sistemov na čipu (od podjetij, kot sta Espressif in Telink), do FPGA (od podjetij, kot je Microsemi), do prihajajočo ploščo Horse Creek podjetij Intel in SiFive.”

Vrne se k kompromisu med zmogljivostjo in natančnostjo. »Fizični prototipi zahtevajo veliko več truda pri načrtovanju, ker povezujete in sintetizirate pravi RTL, vendar zagotavljajo veliko večjo natančnost in prepustnost,« pravi Roddy iz Quadrica. »Fizični prototip v sistemu FPGA, ne glede na to, ali je domač ali ga proizvajajo velika podjetja EDA, zahteva veliko truda, da se pripravi. Lahko pa teče za red velikosti hitreje kot model SystemC in za več razredov hitreje kot polna simulacija na ravni vrat. Oblikovalske ekipe se običajno med postopkom izbire IP preusmerijo iz modelov, ki temeljijo na C, na fizične modele tako za preverjanje dejanske zasnove po izbiri IP kot kot platforma za razvoj sistemske programske opreme.«

Ko veste, kateri nabor funkcij želite v strojni opremi, lahko preverite, ali je nekdo že ustvaril rešitev, ki izpolnjuje večino vaših potreb. »Verjetno je, da bo pri vseh prodajalcih na voljo komercialna rešitev, ki bo imela tisto vrsto stvari, ki jo iščete,« pravi Davidmann. »Toda pri RISC-V vam te rešitve ni treba sprejeti takšne, kot je. Pomemben del vrednosti RISC-V je svoboda, da ga spremenite, prilagodite in dodate različne stvari, ki jih želite.«

Izbira izvedbe

Obstaja veliko načinov za implementacijo nabora funkcij, kot je število stopenj cevovoda ali špekulativne funkcije izvajanja. Vsak bo imel drugačen kompromis med močjo, zmogljivostjo in površino. »Vokus ISA, pa naj bo to RISC-V, Arm, Cadence Xtensa, Synopsysov ARC, v resnici ne vpliva na cilje in kompromise modeliranja in izdelave prototipov,« pravi Roddy. »Sistemski arhitekt mora odgovoriti na vprašanja o ciljih načrtovanja SoC ne glede na znamko procesorja. Na tehnični ravni je RISC-V resnično v stabilnem položaju na trgu glede na podporo orodij za modeliranje in analizo delovanja. Obstajajo številni konkurenčni proizvajalci jeder, vsak z različnimi izvedbami in funkcijami procesorja. Kot glavni sistemski CPE nima dolgoživosti kot Arm, zato ima manj igralcev ekosistema v svetu EDA široko potrjeno, za uporabo pripravljeno podporo za modeliranje za že pripravljena jedra RISC-V iz različnih prodajalcev RISC-V. Svet RISC-V kot jedro, ki ga je mogoče konfigurirati in spreminjati, zaostaja na ravni avtomatizacije nabora navodil, ki jo je Tensilica gradila 25 let. Tako ima RISC-V manj podpore za modeliranje kot že pripravljen gradnik in manj avtomatizacije za uporabo kot platforma za eksperimentiranje z nizom navodil.«

Toda to je le en vidik izvajanja, ki ga je treba oceniti. Kakšna je njegova kakovost? Če ga želite spremeniti, kako ga znova potrdite?

Uspešnost je najlažje oceniti. »To ni nič drugega kot obisk katerega koli tradicionalnega prodajalca procesorjev,« pravi Davidmann. »Rekli vam bodo, da vam to jedro daje toliko Dhrystones na vat, dali vam bodo tipične analitične podatke procesorja, ki pravijo, kako hitro teče ta mikroarhitektura. Imajo vse te podatke in vsakdo, ki licencira procesorsko jedro, bo seznanjen s temi podatki in se bo pogovoril z njimi ter dobil te informacije. Verjetno bodo imeli na svojem podatkovnem listu veliko izbirnih možnosti in rekli bodo: 'Če vklopite to možnost, dobite to ali ono.' Ogledate si ga lahko na podatkovnem listu, na spletnih mestih prodajalcev.«

Na tej ravni verjetno potrebujete natančnost cikla. »Vidim, da večina ljudi to črpa v emulator in skozenj vodi dovolj podatkov, da lahko sprejme razumno odločitev,« pravi Schirrmeister. »Ne vidim, da bi kmalu prešli na virtualne prototipe. Nekatera podjetja govorijo o prototipih FPGA, kjer imate svojo rešitev z eno ploščo. Odvisno od vprašanja, na katerega morate odgovoriti, se lahko odločite, da ga konfigurirate, ustvarite in nato črpate v FPGA, da prek njega poganjate več podatkov, z ustreznimi programskimi rutinami na vrhu. Industrija ima dovolj hitre vstopne poti v emulatorje in izdelavo prototipov, da to omogoča. Osnovna težava je v tem, da želite to odločitev sprejeti na podlagi čim bolj natančnih podatkov, vendar morda ne boste imeli teh natančnih podatkov takrat, ko se boste želeli odločiti.«

Mnogi od teh prototipov morajo vključevati več kot le procesor. »Virtualne platforme omogočajo integracijo z drugimi zunanjimi funkcijami fizične strojne opreme, kot so pomnilnik in senzorji, ki delujejo v resničnem okolju,« pravi Narayanan iz Microchipa. »Hibridni sistemi lahko združujejo virtualne platforme s fizičnimi prototipi za druge zunanje funkcije. Emulacija FPGA in izdelava prototipov pomagata pri iskanju napak, povezanih s časom, kot so pogoji dirke, saj je to bolj natančno in zunanje funkcije delujejo s hitrostjo.«

Preverjanje

Ker je načrtovanje procesorja že dolgo časa interno, ni javnega ekosistema preverjanja za izdelavo procesorja, funkcije RISC-V pa zahtevajo veliko bolj prilagodljivo rešitev preverjanja, kot je kadar koli obstajala v preteklosti. Ustvarjanje tega se šele začenja dogajati.

»Obstajajo industrijske meritve, kot sta Dhrystones ali CoreMark, tako da lahko ljudje primerjajo uspešnost,« pravi Davidmann. »Toda kako lahko primerjate kakovost preverjanja? Obstajati morajo enaki konkurenčni pogoji, tako da lahko vsak prodajalec reče: 'Tako delamo mi'. Za preverjanje potrebujemo nekaj meril kakovosti.«

Tu lahko pomaga odprtokodno gibanje. »Če pogledate ekosistem RISC-V, imate veliko število zelo izkušenih razvijalcev procesorjev,« pravi Schirrmeister. »Dve skrajnosti sta. Eno je, da dobim jedro od prodajalca in če ne deluje, imate težave z njim. Po drugi strani pa imam popolno svobodo in vse počnem sam. Nekje vmes med tema skrajnostma se razvija ravnovesje. Dobite nekaj, pri čemer vaš prodajalec zagotovi določeno količino preverjanja, nato pa so razširitve vaša lastna odgovornost.«

In tu pridejo na vrsto metrike. »Združljivost ISA je le prva stopnička na lestvici, polni zapletenosti, na katero se je povzpelo le nekaj podjetij,« pravi Dave Kelf, izvršni direktor za Breker Verification Systems. »Izdelava prototipov je morda edini način za popolno zagotovitev zanesljivega delovanja procesorja, vendar izkoriščanje resničnih delovnih obremenitev za pogon teh prototipov popraska površino dejanske pokritosti procesorja. To je v nasprotju s konkurenčnimi prizadevanji odprtega ISA, ki spodbuja pospešen razvoj in težave s časom do trga.«

Toda kaj so te meritve? »V skupini za kakovost OpenHW poskušamo ugotoviti, kakšne bi morale biti te metrike,« pravi Davidmann. »To vključuje stvari, kot je funkcionalna pokritost, saj ne gre samo za preprosta navodila. Za visokokakovosten procesor potrebujete veliko več kot to. Imeti morate metodologijo za preverjanje, kjer obstaja zaupanje, da vaše primerjave z referenco pokrivajo vse. Funkcionalna pokritost samo kaže, da imate test, vendar mora biti to povezano z metodologijo, ki primerja z neko obliko znane reference. Dodali bomo tehnologijo vnašanja napak, tako da bo mogoče ugotoviti, ali vaša preskusna naprava dejansko zazna težave.«

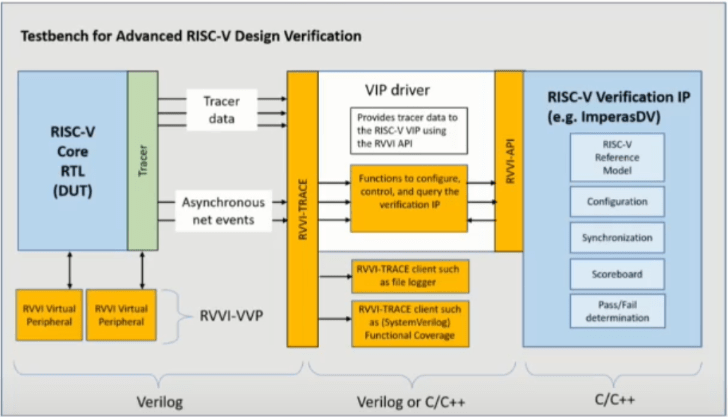

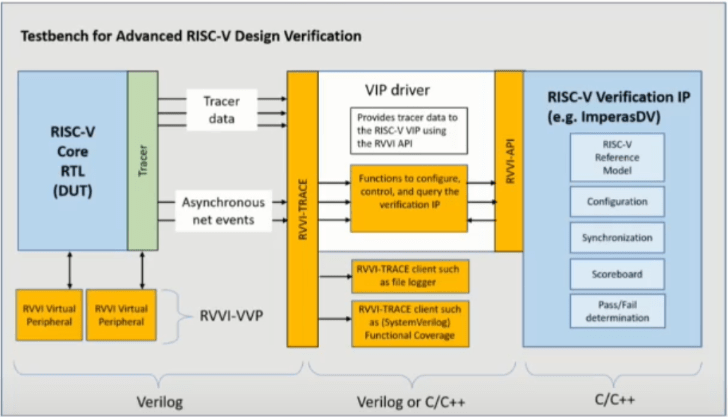

Slika 1: Definiranje arhitekture rešitve za preverjanje RISC-V. Vir: Imperas

Potreben bo nabor orodij. »Ko ekosistem RISC-V dozoreva, komercialne izvedbe začenjajo podpirati opredeljene tržne segmente,« pravi Ashish Darbari, ustanovitelj in izvršni direktor podjetja Axiomise. »Vidimo podporo za trge, kot je avtomobilski, ki zahtevajo skladnost s funkcionalno varnostjo. Vidimo podporo za IoT, ki zahteva varnost. Prodajalci RISC-V vlagajo v napredne tehnike preverjanja, vključno z virtualnimi prototipi za arhitekturno modeliranje in zmogljivost. Zdaj so na voljo orodja za zgodnje sprejemanje formalnih metod za odpravo hroščev zgodaj v procesu načrtovanja in izogibanje vstavljanju hroščev, ko se oblikovalci trudijo ujeti hrošče v kotnih primerih s simulacijo na vmesniku procesor-pomnilnik.«

Eno od orodij, ki bo potrebno, je zmožnost generiranja testnih primerov na podlagi seznama funkcij ali nabora zmogljivosti. "Avtomatizirano ustvarjanje testne vsebine za pogon prototipov, ki pravočasno upoštevajo kompleksnost preverjanja, je ključnega pomena," pravi Brekerjev Kelf. "Ti mehanizmi za ustvarjanje se zdaj začenjajo pojavljati na trgu."

zaključek

Ekosistem je dober le toliko, kolikor je dober njegov najšibkejši sestavni del, za RISC-V pa je to veriga orodij EDA. Razloga za to sta dva. Prvič, do nedavnega ni bilo komercialnega trga za orodja za preverjanje procesorja. Medtem ko so obstajali v preteklosti, so vsi izginili ali pa so bili raztopljeni v starih procesorskih podjetjih. Drugič, prilagodljivost RISC-V ISA ustvari nov pristop optimizacije na ravni sistema, ki zahteva nov nabor orodij. Potreben je čas, da se ta priložnost razume in da se pojavijo komercialna orodja, ki jo ustrezno obravnavajo.

Podobni

Najmanjši RISC-V

Ali obstaja prostor za še manjšo različico procesorja RISC-V, ki bi lahko nadomestil 8-bitne mikrokontrolerje?

RISC-V prehaja v mainstream

Odprtokodna procesorska jedra se začenjajo pojavljati v heterogenih SoC in paketih.

Učinkovito sledenje v RISC-V

Kako delati z novim standardom za odpravljanje napak RISC-V.

Kako varni so čipi RISC-V?

Odprta koda sama po sebi ne zagotavlja varnosti. Še vedno gre za osnove oblikovanja.

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- Platoblockchain. Web3 Metaverse Intelligence. Razširjeno znanje. Dostopite tukaj.

- vir: https://semiengineering.com/selecting-the-right-risc-v-core/

- 1

- 10

- a

- sposobnost

- Sposobna

- O meni

- nad

- pospešeno

- pospeševalniki

- Sprejmi

- sprejemljiv

- Račun

- natančnost

- natančna

- dejansko

- Naslov

- Sprejetje

- napredno

- po

- proti

- algoritem

- vsi

- že

- znesek

- Analiza

- Analitično

- in

- in infrastrukturo

- odgovor

- zdi

- uporaba

- pristop

- primerno

- Lok

- architectural

- Arhitektura

- OBMOČJE

- ARM

- vidik

- ocenili

- Avtomatizirano

- Avtomatizacija

- avtomobilska

- Na voljo

- povprečno

- nazaj

- pasovna širina

- temeljijo

- Osnovni

- ker

- postane

- postajajo

- pred

- Začetek

- počutje

- koristi

- BEST

- med

- Poleg

- Big

- Bit

- Block

- svet

- blagovne znamke

- prinašajo

- splošno

- Bug

- hrošči

- izgradnjo

- Building

- zgrajena

- poslovni

- poslovni razvoj

- CAD

- Zmogljivosti

- lahko

- wrestling

- ceo

- nekatere

- izziv

- izzivi

- kvote

- spremenite

- čipi

- izbira

- možnosti

- Izberite

- Plezal

- CMO

- zavarovanje

- kako

- komercialna

- komercialno

- Skupno

- Podjetja

- primerjate

- združljivost

- tekmuje

- konkurenčno

- dokončanje

- zapletenosti

- skladnost

- komponenta

- deli

- računalniki

- Skrbi

- Pogoji

- zaupanje

- konfiguracija

- Povezovanje

- premislekov

- vsebina

- Core

- bi

- skupaj

- pokritost

- kritje

- CPU

- ustvaril

- ustvari

- Ustvarjanje

- Oblikovanje

- potok

- CTO

- Trenutno

- datum

- Dave

- Odločitev

- definiranje

- poda

- zahteve

- Oddelek

- Odvisno

- razporejeni

- Oblikovanje

- proces oblikovanja

- oblikovalci

- Razvoj

- razvili

- Razvijalci

- razvoju

- Razvoj

- naprave

- drugačen

- težko

- Direktor

- Ne

- dont

- navzdol

- pogon

- vozi

- vožnjo

- med

- vsak

- Zgodnje

- najlažje

- ekosistem

- Ekosistemi

- prizadevanje

- prizadevanja

- bodisi

- vgrajeni

- omogoča

- Motor

- Inženiring

- Motorji

- dovolj

- zagotovitev

- zagotoviti

- Podjetje

- Celotna

- Vpis

- okolje

- okolja

- enako

- Equilibrium

- ustanovljena

- ocene

- oceniti

- Tudi

- VEDNO

- vse

- izvedba

- izkušen

- razširitev

- razširitev

- razširitve

- zunanja

- skrajnosti

- Obraz

- seznanjeni

- Moda

- FAST

- hitreje

- Feature

- Lastnosti

- Nekaj

- Polje

- Slika

- Najdi

- iskanje

- prva

- fit

- Všita

- prilagodljivost

- prilagodljiv

- obrazec

- formalno

- Ustanovitelj

- Ustanovitelj in izvršni direktor

- FPGA

- Svoboda

- iz

- polno

- v celoti

- funkcija

- funkcionalno

- funkcije

- Osnove

- splošno

- ustvarjajo

- ustvarjajo

- generacija

- dobili

- pridobivanje

- Daj

- daje

- Go

- Cilji

- dogaja

- dobro

- več

- skupina

- Pridelovanje

- Garancija

- se zgodi

- strojna oprema

- pomoč

- Pomaga

- visoka kvaliteta

- domači

- Konj

- Kako

- HTTPS

- velika

- vpliv

- izvajati

- Izvajanje

- in

- vključujejo

- vključuje

- Vključno

- narašča

- vedno

- Industrija

- Podatki

- Infrastruktura

- Navodila

- integrirati

- Intel

- zainteresirani

- vmesnik

- Facebook Global

- vlaganjem

- vključeni

- Internet stvari

- IP

- Vprašanja

- IT

- sam

- Job

- Ključne

- Otrok

- Vedite

- znano

- lestev

- velika

- Legacy

- Stopnja

- ravni

- vzvod

- licenciranje

- Verjeten

- linux

- Seznam

- Long

- dolgo časa

- dolgoživost

- Poglej

- si

- je

- Glavne

- Znamka

- avtomat

- IZDELA

- več

- znamka

- Tržna

- Prisotnost

- zori

- max širine

- Srečati

- Spomin

- Metodologija

- Metode

- Meritve

- minimalna

- Model

- modeliranje

- modeli

- spremenite

- več

- Najbolj

- Gibanje

- premikanje

- potrebno

- Nimate

- potrebe

- Novo

- Številka

- številne

- Cilj

- Kvota

- Ponudbe

- ONE

- odprite

- open source

- deluje

- Delovanje

- Priložnost

- optimizacija

- Možnost

- možnosti

- Da

- naročila

- Ostalo

- lastne

- pakete

- del

- deli

- preteklosti

- Peak

- ljudje

- performance

- fizično

- plinovod

- pivot

- platforma

- Platforme

- platon

- Platonova podatkovna inteligenca

- PlatoData

- igralci

- igranje

- Točka

- Pogled na točko

- Stališče

- možnosti

- mogoče

- moč

- Predsednik

- verjetno

- problem

- Težave

- Postopek

- Procesor

- procesorji

- Napredek

- pravilno

- Prototip

- prototipi

- prototipov

- zagotavljajo

- če

- Ponudnik

- javnega

- Črpalka

- črpanje

- Namen

- namene

- kakovost

- vprašanje

- vprašanja

- Dirka

- območje

- pripravljen

- pravo

- resnični svet

- Razlog

- razumno

- Razlogi

- Pred kratkim

- Ne glede na to

- zanesljiv

- zamenjajte

- zahteva

- obvezna

- zahteva

- Zahteve

- zahteva

- Odgovornost

- soba

- Run

- tek

- Varnost

- Varnost in zaščita

- drugi

- zavarovanje

- varnost

- segmentih

- izbran

- izbiranje

- izbor

- višji

- senzorji

- nastavite

- več

- shouldnt

- Prikaži

- Razstave

- pomemben

- Simon

- Enostavno

- Simulacija

- sam

- Počasi

- manj

- So

- Software

- Razvoj programske opreme

- Rešitev

- rešitve

- nekaj

- nekdo

- Nekaj

- nekje

- Kmalu

- vir

- hitrost

- porabljen

- Spin

- stabilna

- postopka

- standardna

- Začetek

- Steve

- Še vedno

- Boj

- taka

- apartma

- podpora

- Površina

- sistem

- sistemi

- Bodite

- meni

- Pogovor

- pogovor

- Skupine

- tehnični

- tehnike

- Tehnologija

- Predloga

- Test

- O

- njihove

- zato

- stvar

- stvari

- 3

- skozi

- pretočnost

- čas

- zamudno

- krat

- čas

- do

- danes

- skupaj

- tudi

- orodja

- vrh

- Skupaj za plačilo

- sledenje

- tradicionalna

- OBRAT

- tipičen

- tipično

- razumel

- Enota

- prihajajoče

- uporaba

- uporabnik

- Uporabniki

- potrjeno

- potrjevanje

- vrednost

- raznolikost

- Prodajalec

- prodajalci

- Preverjanje

- različica

- preživetja

- Podpredsednica

- Poglej

- Virtual

- virtualne platforme

- želim

- načini

- spletne strani

- Kaj

- Kaj je

- ali

- ki

- medtem

- bo

- v

- delo

- telovaditi

- svet

- bi

- Napačen

- X

- let

- Vaša rutina za

- zefirnet