Dve nedavni algoritemski tehnologiji, ki temeljita na programski opremi –– avtonomna vožnja (ADAS/AD) in generativna umetna inteligenca (GenAI) – skrbita, da skupnost polprevodniških inženirjev ponoči pokonci prespi.

Medtem ko sta ADAS na ravni 2 in 3 na dobri poti, sta AD na stopnji 4 in 5 daleč od realnosti, kar povzroča padec navdušenja in denarja glede tveganega kapitala. Danes GenAI pritegne pozornost in tvegani kapitalisti vneto vlagajo milijarde dolarjev.

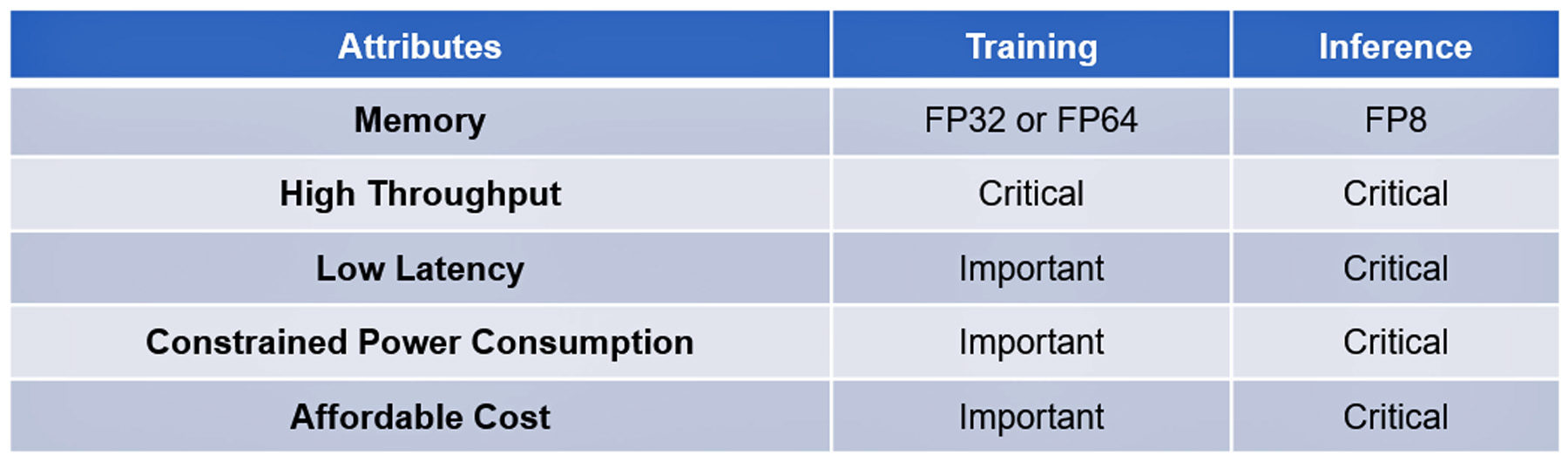

Obe tehnologiji temeljita na sodobnih, kompleksnih algoritmih. Obdelava njihovega usposabljanja in sklepanja ima nekaj skupnih lastnosti, nekatere kritične, druge pomembne, a ne bistvene: Glej tabelo I.

Izjemen napredek programske opreme v teh tehnologijah do zdaj ni bil ponovljen z napredkom algoritemske strojne opreme za pospešitev njihovega izvajanja. Na primer, najsodobnejši algoritemski procesorji nimajo dovolj zmogljivosti, da bi odgovorili na poizvedbe ChatGPT-4 v eni ali dveh sekundah po ceni 2 ¢ na poizvedbo, kar je merilo uspešnosti, ki ga je določilo iskanje Google, ali za obdelavo ogromnih podatkov senzorji AD zberejo v manj kot 20 milisekundah.

To je bilo vse dokler francosko zagonsko podjetje VSORA ni vložilo možganov v reševanje ozkega grla spomina, znanega kot spominski zid.

Zid spomina

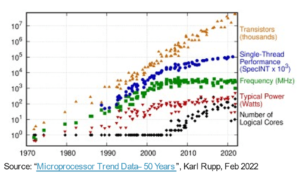

Pomnilniški zid CPE sta leta 1994 prvič opisala Wulf in McKee. Od takrat so dostopi do pomnilnika postali ozko grlo računalniške zmogljivosti. Napredek v zmogljivosti procesorja se ni odrazil v napredku pri dostopu do pomnilnika, zaradi česar morajo procesorji vedno dlje čakati na podatke, ki jih posredujejo pomnilniki. Na koncu učinkovitost procesorja pade daleč pod 100-odstotno izkoriščenost.

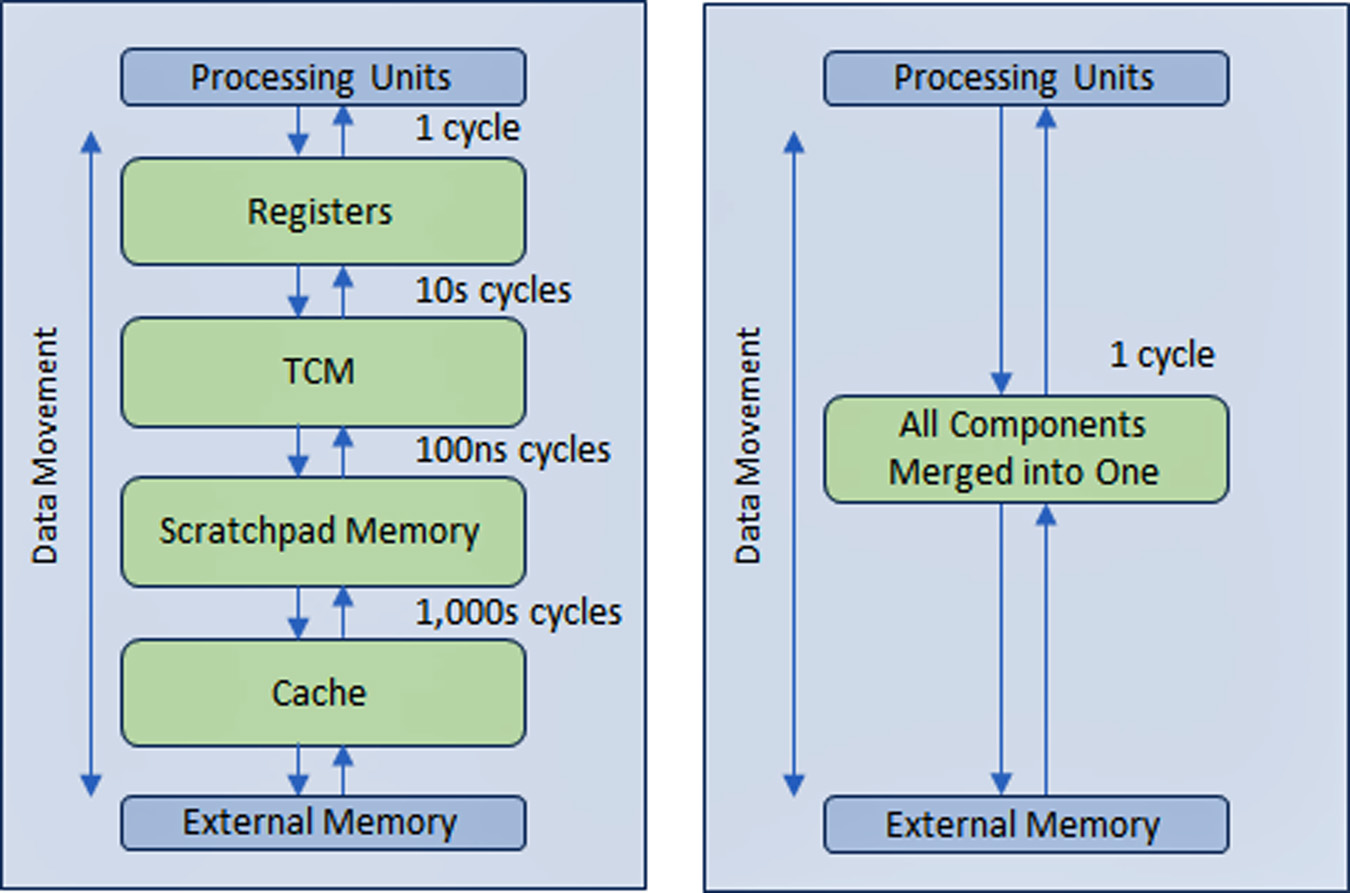

Za rešitev problema je polprevodniška industrija ustvarila večnivojsko hierarhično pomnilniško strukturo z več nivoji predpomnilnika bližje procesorju, ki zmanjša količino prometa s počasnejšimi glavnimi in zunanjimi pomnilniki.

Zmogljivost procesorjev AD in GenAI je bolj kot pri drugih vrstah računalniških naprav odvisna od široke pasovne širine pomnilnika.

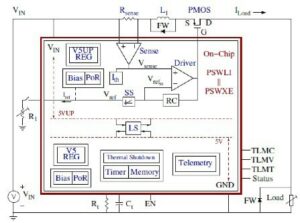

VSORA, ustanovljena leta 2015 za ciljanje na aplikacije 5G, je izumila patentirano arhitekturo, ki strne hierarhično pomnilniško strukturo v velik visokopasovni, tesno sklopljeni pomnilnik (TCM), do katerega dostopate v enem taktu.

Z vidika procesorskih jeder je TCM videti in deluje kot morje registrov v količini megabajtov v primerjavi s kbajti dejanskih fizičnih registrov. Možnost dostopa do katere koli pomnilniške celice v TMC v enem ciklu zagotavlja visoko hitrost izvajanja, nizko zakasnitev in nizko porabo energije. Zahteva tudi manj površine silicija. Nalaganje novih podatkov iz zunanjega pomnilnika v TCM med obdelavo trenutnih podatkov ne vpliva na prepustnost sistema. V osnovi arhitektura omogoča 80+% izkoriščenost procesorskih enot s svojo zasnovo. Kljub temu obstaja možnost dodajanja predpomnilnika in pomnilnika za beležko, če načrtovalec sistema tako želi. Glej sliko 1.

Prek registru podobne pomnilniške strukture, implementirane v skoraj vse pomnilnike v vseh aplikacijah, prednosti pomnilniškega pristopa VSORA ni mogoče preceniti. Običajno vrhunski procesorji GenAI zagotavljajo enomestno odstotno učinkovitost. Na primer, procesor GenAI z nominalno prepustnostjo enega petaflopa nominalne zmogljivosti, vendar manj kot 5-odstotno učinkovitostjo, zagotavlja uporabno zmogljivost manj kot 50 teraflopov. Namesto tega arhitektura VSORA dosega več kot 10-krat večjo učinkovitost.

Algoritemski pospeševalnik VSORA

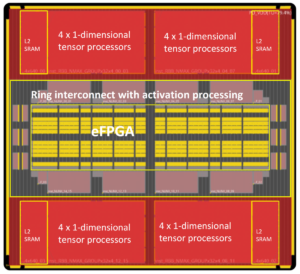

VSORA je predstavila dva razreda algoritemskih pospeševalnikov – družino Tyr za aplikacije AD in družino Jotunn za pospeševanje GenAI. Oba zagotavljata neverjetno prepustnost, minimalno zakasnitev, nizko porabo energije v majhnem silikonskem odtisu.

Z nominalno zmogljivostjo do treh petaflopov se ponašajo s tipično učinkovitostjo implementacije 50–80 % ne glede na vrsto algoritma in največjo porabo energije 30 vatov/petaflops. To so zvezdniške lastnosti, o katerih še ni poročal noben konkurenčen pospeševalnik AI.

Tyr in Jotunn sta v celoti programabilna in vključujeta zmožnosti AI in DSP, čeprav v različnih količinah, ter podpirata sprotno izbiro aritmetike od 8-bitne do 64-bitne na osnovi celih števil ali plavajoče vejice. Njihova programirljivost se prilagaja vesolju algoritmov, zaradi česar so algoritmsko agnostični. Podprtih je tudi več različnih vrst redkosti.

Atributi procesorjev VSORA jih poganjajo v ospredje konkurenčne krajine algoritemske obdelave.

Podporna programska oprema VSORA

VSORA je zasnovala edinstveno platformo za zbiranje/validacijo, prilagojeno njeni arhitekturi strojne opreme, da bi zagotovila, da imajo njene kompleksne, visoko zmogljive naprave SoC veliko programske podpore.

Razpon hierarhičnih stopenj preverjanja/validacije –– ESL, hibrid, RTL in vrata –, ki naj bi oblikovalca algoritmov postavil v pilotsko kabino, algoritemskemu inženirju zagotavlja povratne informacije s pritiskom na gumb kot odgovor na raziskovanje prostora načrtovanja. To mu pomaga izbrati najboljši kompromis med zmogljivostjo, zakasnitvijo, močjo in površino. Programsko kodo, napisano na visoki ravni abstrakcije, je mogoče preslikati tako, da uporabniku pregledno cilja na različna procesna jedra.

Vmesništvo med jedri se lahko izvaja znotraj istega silicija, med čipi na istem tiskanem vezju ali prek povezave IP. Sinhronizacija med jedri se upravlja samodejno v času prevajanja in ne zahteva programskih operacij v realnem času.

Ovira za avtonomno vožnjo L4/L5 in generativno sklepanje z umetno inteligenco na robu

Uspešna rešitev mora vključevati tudi možnost programiranja na terenu. Algoritmi se hitro razvijajo, poganjajo jih nove ideje, ki čez noč zastarijo včerajšnje stanje tehnike. Omembe vredna prednost je možnost nadgradnje algoritma na terenu.

Medtem ko podjetja hiperscale sestavljajo ogromne računalniške farme z množico svojih najzmogljivejših procesorjev za obvladovanje naprednih algoritmov programske opreme, je pristop praktičen samo za usposabljanje, ne pa za sklepanje na robu.

Usposabljanje običajno temelji na 32-bitni ali 64-bitni aritmetiki s plavajočo vejico, ki ustvarja velike količine podatkov. Ne nalaga stroge zakasnitve in dopušča visoko porabo energije ter znatne stroške.

Sklepanje na robu se običajno izvaja na podlagi 8-bitne aritmetike s plavajočo vejico, ki generira nekoliko manjše količine podatkov, vendar zahteva brezkompromisno zakasnitev, nizko porabo energije in nizke stroške.

Vpliv porabe energije na zakasnitev in učinkovitost

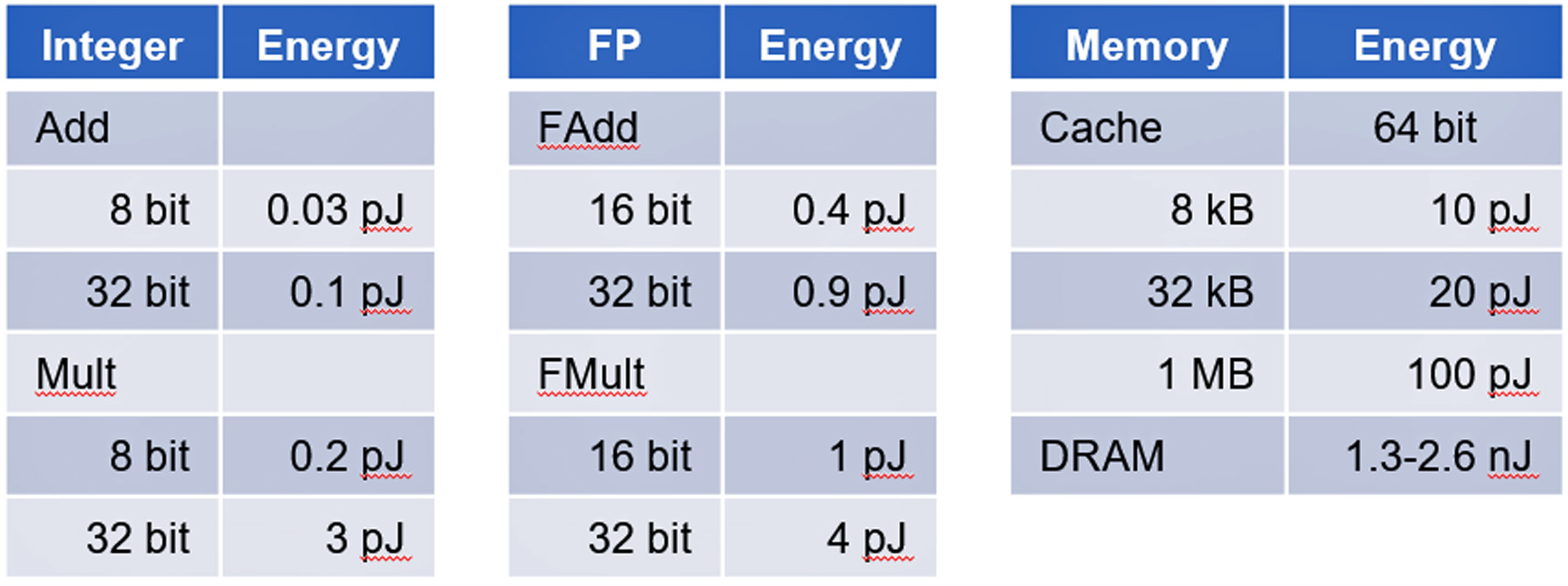

Porabo energije v CMOS IC prevladuje gibanje podatkov in ne obdelava podatkov.

Študija univerze Stanford, ki jo je vodil profesor Mark Horowitz, je pokazala, da poraba energije pri dostopu do pomnilnika porabi za rede velikosti več energije kot osnovni digitalni logični izračuni. Glej tabelo II.

Pospeševalnika AD in GenAI sta odlična primera naprav, v katerih prevladuje prenos podatkov, kar predstavlja izziv za omejitev porabe energije.

zaključek

Sklepanje AD in GenAI predstavlja netrivialne izzive za doseganje uspešnih implementacij. VSORA lahko zagotovi celovito strojno rešitev in podporno programsko opremo za izpolnitev vseh kritičnih zahtev za upravljanje AD L4/L5 in GenAI, kot je pospeševanje GPT-4, po komercialno sprejemljivih stroških.

Več podrobnosti o VSORA in njenih Tyr in Jotunn najdete na www.vsora.com.

O Lauru Rizzattiju

Lauro Rizzatti je poslovni svetovalec pri VSORA, inovativno zagonsko podjetje, ki ponuja silicijeve IP rešitve in silicijeve čipe, ter priznani svetovalec za preverjanje in industrijski strokovnjak za emulacijo strojne opreme. Pred tem je opravljal funkcije v vodstvu, produktnem trženju, tehničnem trženju in inženiringu.

Preberite tudi:

Soitec načrtuje prihodnost polprevodniške industrije

ISO 21434 za razvoj SoC, ki upošteva kibernetsko varnost

Prediktivno vzdrževanje v kontekstu avtomobilske funkcionalne varnosti

Delite to objavo prek:

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- PlatoData.Network Vertical Generative Ai. Opolnomočite se. Dostopite tukaj.

- PlatoAiStream. Web3 Intelligence. Razširjeno znanje. Dostopite tukaj.

- PlatoESG. Ogljik, CleanTech, Energija, Okolje, sončna energija, Ravnanje z odpadki. Dostopite tukaj.

- PlatoHealth. Obveščanje o biotehnologiji in kliničnih preskušanjih. Dostopite tukaj.

- vir: https://semiwiki.com/automotive/336201-long-standing-roadblock-to-viable-l4-l5-autonomous-driving-and-generative-ai-inference-at-the-edge/

- :ima

- : je

- :ne

- $GOR

- 000

- 1

- 10

- 1800

- 1994

- 20

- 30

- 50

- 5G

- a

- sposobnost

- O meni

- abstrakcija

- pospeši

- pospešek

- plin

- pospeševalniki

- dostop

- dostopna

- Dostop

- Doseči

- Dosega

- čez

- aktov

- dejanska

- Ad

- ADA

- dodajte

- Naslov

- napredno

- napredek

- Prednost

- svetovalec

- vplivajo

- AI

- algoritem

- algoritmični

- algoritmi

- vsi

- omogoča

- Prav tako

- znesek

- zneski

- an

- in

- odgovor

- kaj

- aplikacije

- pristop

- Arhitektura

- SE

- OBMOČJE

- Umetnost

- AS

- At

- pozornosti

- lastnosti

- samodejno

- avtomobilska

- avtonomno

- pasovna širina

- temeljijo

- Osnovni

- V bistvu

- BE

- postanejo

- bilo

- spodaj

- merilo

- BEST

- med

- milijardah

- tako

- poslovni

- vendar

- by

- predpomnilnik

- CAN

- ne more

- Zmogljivosti

- Kapital

- povzroča

- celica

- izziv

- izzivi

- čipi

- razredi

- Ure

- Cockpit

- Koda

- sesuje

- komercialno

- skupnost

- Podjetja

- konkurenčno

- kompleksna

- zapleten

- celovito

- Kompromis

- izračuni

- Izračunajte

- računalništvo

- povezava

- svetovalec

- poraba

- vsebujejo

- ozadje

- strošek

- stroški

- skupaj

- CPU

- ustvaril

- kritično

- Trenutna

- vrhunsko

- cikel

- datum

- obdelava podatkov

- poda

- dostavi

- daje

- gosto

- odvisno

- opisano

- Oblikovanje

- zasnovan

- oblikovalec

- Podrobnosti

- naprave

- drugačen

- digitalni

- števk

- do

- ne

- dolarjev

- vozi

- vožnjo

- Drop

- Kapljice

- nestrpno

- Edge

- učinkovitosti

- bodisi

- konec

- energija

- Poraba energije

- inženir

- Inženiring

- zagotovitev

- navdušenje

- ZOI

- bistvena

- ustanovljena

- VEDNO

- razvijajo

- Primer

- Primeri

- izvedba

- strokovnjak

- zunanja

- družina

- daleč

- Kmetije

- povratne informacije

- Nekaj

- Polje

- Slika

- prva

- plavajoči

- Odtis

- za

- ospredju

- je pokazala,

- Ustanovljeno

- francosko

- iz

- v celoti

- funkcionalno

- Prihodnost

- ustvarja

- generativno

- Generativna AI

- Google Search

- več

- ročaj

- strojna oprema

- Imajo

- he

- Hero

- Pomaga

- jo

- visoka

- visokozmogljivo

- najvišja

- ga

- Horowitz

- http

- HTTPS

- velika

- Hybrid

- i

- ICS

- Ideje

- if

- ii

- Izvajanje

- izvedbe

- izvajali

- Pomembno

- naložila

- in

- vključujejo

- Industrija

- Strokovnjak za industrijo

- inovativne

- primer

- Namesto

- integrirati

- v

- Uvedeno

- Izmišljeno

- Invest

- investirali

- IP

- IT

- ITS

- jpg

- Skoki

- vzdrževanje

- znano

- Pokrajina

- velika

- Latenca

- Led

- manj

- Stopnja

- ravni

- kot

- nalaganje

- Logika

- dolgoletni

- več

- POGLEDI

- nizka

- Glavne

- vzdrževanje

- Izdelava

- upravlja

- upravljanje

- mandati

- znamka

- Trženje

- ogromen

- max širine

- Srečati

- spomini

- Spomin

- milisekund

- minimalna

- sodobna

- Denar

- več

- Gibanje

- več

- množice

- Novo

- noč

- opozoriti

- vredno omeniti

- zdaj

- zastarela

- of

- ponujanje

- on

- ONE

- samo

- operacije

- or

- Da

- naročila

- Ostalo

- drugi

- več

- čez noč

- pretirano

- patentiran

- Peak

- za

- odstotek

- performance

- opravljeno

- perspektiva

- fizično

- platforma

- platon

- Platonova podatkovna inteligenca

- PlatoData

- Veliko

- Točka

- pozicije

- možnost

- Prispevek

- moč

- Praktično

- prej

- Predsednik

- problem

- Postopek

- obdelani

- obravnavati

- Procesor

- procesorji

- Izdelek

- Učitelj

- programabilno

- Programiranje

- Napredek

- Propel

- dal

- poizvedbe

- območje

- hitro

- Preberi

- v realnem času

- Reality

- nedavno

- zmanjšuje

- Ne glede na to

- registri

- izjemno

- podvojeno

- Prijavljeno

- zahteva

- Zahteve

- zahteva

- Odgovor

- Enako

- MORJE

- Iskalnik

- sekund

- glej

- izbor

- polprevodnik

- senzorji

- več

- Delite s prijatelji, znanci, družino in partnerji :-)

- Delnice

- shouldnt

- je pokazala,

- Silicij

- saj

- sam

- majhna

- So

- Software

- Rešitev

- rešitve

- SOLVE

- nekaj

- nekoliko

- vir

- Vesolje

- hitrost

- porabljen

- Stanford

- Univerza Stanford

- zagon

- Država

- state-of-the-art

- Stellar

- Še vedno

- racionaliziran

- stroga

- Struktura

- študija

- precejšen

- uspešno

- podpora

- Podprti

- Podpora

- Sinhronizacija

- sistem

- miza

- prilagojene

- ciljna

- ciljanje

- tehnični

- Tehnologije

- kot

- da

- O

- Prihodnost

- njihove

- Njih

- Tukaj.

- te

- jih

- ta

- 3

- skozi

- pretočnost

- tesno

- čas

- krat

- do

- danes

- sledenje

- tradicionalna

- Prometa

- usposabljanje

- pregledno

- dva

- tip

- Vrste

- tipičen

- tipično

- edinstven

- enote

- Vesolje

- univerza

- dokler

- nadgradnja

- uporabno

- uporabnik

- uporabo

- VC-ji

- podjetje

- tveganega kapitala

- Preverjanje

- Proti

- preko

- preživetja

- praktično

- prostornine

- Počakaj

- Wall

- je

- način..

- Dobro

- kdaj

- medtem

- široka

- želje

- z

- v

- pisni

- še

- donosov

- zefirnet