Pri delovanju sodobnih naprav CPE od 80 % do 90 % porabe energije in časovnih zakasnitev povzroči pretok podatkov med CPE in pomnilnikom zunaj čipa. Da bi zmanjšali to skrb glede zmogljivosti, oblikovalci svojim procesorjem dodajajo dodaten pomnilnik na čipu. Tradicionalno je bil SRAM najpogosteje uporabljen tip pomnilnika procesorja na čipu. Na žalost je SRAM trenutno omejen na velikost več sto megabajtov. Ta omejitev pomnilnika na čipu morda ne zadostuje za vrhunske aplikacije.

Prihodnje aplikacije CPE, kot je programiranje jezikovnega modela AI in obdelava slik za 8K UHD video, bodo zahtevale pasovno širino dostopa do V/I pomnilnika v območju 10 terabajtov/s. Za izpolnitev teh zahtev glede pasovne širine bo moral biti pomnilnik procesorja na čipu večji od 1 terabajta. Za izpolnitev teh prihodnjih zahtev po pomnilniku na čipu bo morda potrebna alternativa SRAM. Ena od možnih rešitev te težave bi bila uporaba uporovnega pomnilnika z naključnim dostopom (ReRAM). [1,2,3]

Naprava ReRAM je obstojna pomnilniška celica, ki vsebuje memristorske materiale. Ti materiali delujejo kot dielektrični izolator. Ko se uporabi dovolj visoka napetost, se oblikuje prevodna pot. Tipični spominski materiali, ki se uporabljajo kot memristorji, vključujejo HfO2, Ta2O5in TiO2. [4] Uporovno stanje pomnilniške celice je mogoče prebrati z uporabo elektronskih vezij, da se ugotovi, ali je pomnilniška celica programirana ali izbrisana, in tako identificira stanje pomnilniškega bita. Pomnilniške celice ReRAM lahko zložite navpično, kot je arhitektura 3D-NAND, da povečate gostoto shranjevanja.

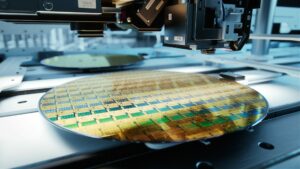

V tem članku, Virtualna izdelava SEMulator3D bo uporabljen za iskanje poti procesa in vizualizacijo potencialnih arhitektur 3D ReRAM. Ocenili bomo upor celice kot funkcijo oblike pomnilniške celice, skupaj z zmogljivostjo Id-Vg vgrajenega kanalskega tranzistorja v napravi ReRAM.

Model 3D ReRAM je prikazan na sliki 1. Naprava ima 64 plasti besednih črt (WL) s stebri, postavljenimi v šesterokotno razmaknjeno matriko. Besedne črte so oblikovane z izmeničnimi plastmi kovinskih prevodnikov in oksidnega dielektrika. Stebri so vgravirani skozi WL, nato pa se na stranske stene stebrov nanese tanka plast spominskega materiala. Pomnilniški material se odstrani z dna in vrha stebrov, pri čemer ostane samo material na stranskih stenah stebra. Stebri so nato napolnjeni z ognjevarno kovino in volframom.

Pod matričnimi plastmi so kontakti in kovinski medsebojni priključki na vir, odtok in vrata vsestranskih tranzistorjev z učinkom polja (GAA FET). Odtok tranzistorja se poveže s stebrom pomnilniškega niza in se združi z vezjem WL, da zagotovi funkcijo vsaki pomnilniški celici.

Spominska celica je sestavljena iz dveh kovinskih elektrod: kovinskega prevodnika in elektrode iz ognjevarne kovine (slika 2). Med virtualno simulacijo procesa te naprave bomo uporabili procesne spremenljivke za nastavitev in ponastavitev memristorja. Namerno uporabljena napetost bo ustvarila mikroskopske prevodne poti, imenovane prevodni filamenti. Ko se uporabijo električni signali različnih polaritet, se nabiti ioni znotraj memristorja premaknejo, da tvorijo (nastavijo) ali raztopijo (ponastavijo) prevodno žarilno nitko.

Upornost prevodnega filamenta se spreminja pri različnih programskih napetostih. Stanje nizkega upora je v območju 10 k ohmov (nastavljeno), stanje visokega upora pa v območju 1 M ohmov (ponastavitev). [5] Razvili smo virtualni model za prikaz preklopnih uporov naprave 3D ReRAM z rezultati, prikazanimi na sliki 3. Stanje memristorja z visokim uporom je približno 100-krat večji upor kot stanje z nizkim uporom.

Nato je bil izveden navidezni načrt eksperimentov (DOE), da bi bolje razumeli korelacijo med razmerjem odpornosti pomnilniške celice ter velikostjo in obliko pomnilniške celice. Spremenljivke eksperimenta so bile CD stebra, debelina WL in debelina memristorja. Analiza rezultatov DOE kaže, da sta steber CD in debelina memristorja povzročila najpomembnejši odziv. Slika 4 prikazuje konturni diagram razmerja upornosti pomnilniške celice v primerjavi s tema dvema spremenljivkama. Pri visokih vrednostih polmera stebra in debeline memristorja je prišlo do 3-kratne spremembe upora pomnilniške celice. Razlike v obliki pomnilniške celice v preučevanem območju ne bodo vplivale na zmožnost branja pomnilniških stanj memristorja, lahko pa bi vplivale na zmožnost razločevanja programskih stanj v večbitni napravi na celico.

Memristor je mogoče programirati z uporabo toka < 0.10 uA in napetosti < 0.5 V. Te nastavitve napetosti in toka bodo memristorjem (pomnilnik ReRAM) omogočile enostavno integracijo kot pomnilnik na čipu v napredne logične naprave. Simulacija naprave SEMulator3D je predhodno pokazala, da bi moral biti GAA FET tranzistor pod poljem sposoben poganjati napetost in tok, ki ju zahtevata nastavljena in ponastavljena stanja pomnilniške celice memristorja. [6]

Dve veliki težavi sodobnih naprav CPE sta poraba energije in čas zakasnitve, ki nastane zaradi premikanja podatkov med CPE in pomnilnikom zunaj čipa. Povečanje velikosti pomnilnika na čipu lahko reši te težave. V tej študiji smo uporabili SEMulator3D za raziskovanje integracije alternative SRAM (ReRAM) za CPE za pomnilnik na čipu. Uporabili smo virtualni model za boljše razumevanje korakov postopka in morebitnih težav pri postavitvi posameznih memristorskih celic. Izvedli smo tudi študije, da bi preučili nastavljena in ponastavljena stanja memristorja ter učinek dimenzij naprave (oblika in velikost pomnilniške celice) na odpornost besedne linije. Poudarili smo, da je vgrajeni pomnilnik ReRAM mogoče integrirati z napredno logiko z uporabo električnega izhoda tranzistorja GAA pFET za nastavitev in ponastavitev memristorskih celic. Ti rezultati potrjujejo, da je uporovni pomnilnik z naključnim dostopom (ReRAM) obetavna alternativa vgrajenemu pomnilniku SRAM za prihodnje logične aplikacije z visoko pasovno širino.

Reference

- Lanza, Mario (2014). "Pregled uporovnega preklapljanja v dielektrikih z visokim k-om: gledišče na nanometru z uporabo prevodnega mikroskopa na atomsko silo". Materiali, zv. 7, številka 3, str. 2155-2182, doi:10.3390/ma7032155.

- N. Sedghi, et al, »Vloga dušikovega dopinga v ALD Ta2O5 in njegov vpliv na večnivojsko preklapljanje celic v RRAM«, marec 2017, Applied Physics Letters, DOI:10.1063/1.4978033

- Y. Bai, et al, »Študija večnivojskih karakteristik za 3D navpični uporovni preklopni pomnilnik«, znanstvena poročila, zvezek 4, številka članka: 5780 (2014)

- Chen, YC, Sarkar, S., Gibbs, JG, Huang, Y., Lee, JC, Lin, CC, in Lin, CH (2022). »Dvojnofunkcionalni uporovni pomnilnik nano spiralne oblike za uporabo nizov prečnih palic z nizko porabo.«, ACS Applied Engineering Materials, 1(1), 252-257.

- Y. Wu, et al, »Nanometer-Scale HfOx RRAM«, IEEE Electron Device Letters, zvezek: 34, številka: 8, avgust 2013), doi:10.1109/LED.2013.2265404

- V. Sreenivasulu, et al, »Analiza vezja in optimizacija GAA Nanowire FET za nizko moč in visoko preklapljanje«, 11. november 2021, Računalništvo, doi:10.1007/s12633-022-01777-6.

Brett Lowe

Brett Lowe je vodja ekipe za polprevodniške procese in integracijo pri Coventorju, raziskovalnem podjetju Lam. Na področju razvoja polprevodniške tehnologije dela že več kot 35 let. Svojo kariero je začel pri Philips Semiconductors, kjer je delal v proizvodnji in razvoju procesov kot procesni inženir na področjih fotolitografije, suhega jedkanja in mokrih procesov. Nato je osem let preživel v Zilogu, kjer je delal na razvoju procesov enote. Pozneje se je Brett pridružil podjetju Micron Technology, kjer je delal pri razvoju in integraciji procesov DRAM in 3D NAND. Pri Coventorju se osredotoča na podporo strankam podjetja pri njihovem 3D modeliranju polprevodniških procesov in zahtevah po razvoju tehnologije.

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- PlatoData.Network Vertical Generative Ai. Opolnomočite se. Dostopite tukaj.

- PlatoAiStream. Web3 Intelligence. Razširjeno znanje. Dostopite tukaj.

- PlatoESG. Ogljik, CleanTech, Energija, Okolje, sončna energija, Ravnanje z odpadki. Dostopite tukaj.

- PlatoHealth. Obveščanje o biotehnologiji in kliničnih preskušanjih. Dostopite tukaj.

- vir: https://semiengineering.com/developing-reram-as-next-generation-on-chip-memory-for-machine-learning-image-processing-and-other-advanced-cpu-applications/

- :ima

- : je

- :ne

- :kje

- 1

- 10

- 100

- 10K

- 11

- 16

- 1M

- 2013

- 2014

- 2017

- 2021

- 2022

- 35%

- 3d

- 400

- 7

- 75

- 8

- 8k

- a

- sposobnost

- Sposobna

- dostop

- čez

- Zakon

- dodajanje

- Dodatne

- napredno

- vplivajo

- AI

- AL

- vsi

- Vse objave

- ublažiti

- omogočajo

- skupaj

- Prav tako

- alternativa

- an

- Analiza

- in

- uporaba

- aplikacije

- uporabna

- približno

- Arhitektura

- SE

- območja

- Array

- članek

- AS

- At

- atomsko

- Avgust

- b

- pasovna širina

- BE

- bilo

- začel

- Boljše

- med

- Bit

- črna

- Bottom

- rjav

- Sveženj

- vendar

- by

- se imenuje

- CAN

- Kariera

- povzročilo

- CD

- celica

- Celice

- center

- spremenite

- Channel

- lastnosti

- zaračuna

- združuje

- podjetje

- Podjetja

- v primerjavi z letom

- računalnik

- Računalništvo

- Skrb

- dirigent

- Potrdi

- povezuje

- vsebuje

- poraba

- kontakti

- Vsebuje

- Korelacija

- bi

- CPU

- ustvarjajo

- ustvaril

- Cross

- Trenutna

- Trenutno

- Stranke, ki so

- Temnomodra

- datum

- zamuda

- zamude

- izkazati

- Dokazano

- Gostota

- deponiran

- Oblikovanje

- oblikovalci

- Ugotovite,

- razvili

- razvoju

- Razvoj

- naprava

- naprave

- Razlika

- razlike

- drugačen

- dimenzije

- razločevanje

- prikazano

- prikazovalniki

- DOE

- možganov

- risanje

- pogon

- posuši

- med

- E&T

- vsak

- enostavno

- Edge

- učinek

- 8

- Electronic

- vgrajeni

- energija

- Poraba energije

- inženir

- Inženiring

- oceniti

- Eter (ETH)

- preučiti

- izvršeno

- poskus

- Poskusi

- FET

- Polje

- Slika

- napolnjena

- Osredotočite

- za

- moč

- obrazec

- oblikovana

- Obrazci

- je pokazala,

- iz

- funkcija

- Prihodnost

- vrata

- Gates

- generacija

- graf

- več

- Zelen

- Imajo

- he

- visoka

- več

- Poudarjeno

- njegov

- HTTPS

- huang

- Stotine

- ID

- identifikacijo

- IEEE

- if

- slika

- in

- vključujejo

- Povečajte

- narašča

- Navedite

- individualna

- vplivajo

- v notranjosti

- integrirati

- integrirana

- integracija

- v

- razišče

- vprašanje

- ITS

- pridružil

- Lam

- jezik

- pozneje

- plast

- plasti

- postavitev

- vodi

- učenje

- odhodu

- Lee

- levo

- kot

- Limited

- lin

- Logika

- nizka

- stroj

- strojno učenje

- velika

- upravitelj

- proizvodnja

- marec

- Mario

- Material

- materiali

- max širine

- Maj ..

- Srečati

- Spomin

- kovinski

- Mikron

- Model

- modeliranje

- sodobna

- več

- Najbolj

- premikanje

- Gibanje

- Nimate

- potrebna

- Naslednja

- november

- Številka

- of

- OHM

- on

- ONE

- samo

- Delovanje

- optimizacija

- or

- Ostalo

- izhod

- pot

- poti

- za

- performance

- Philips

- Fizika

- steber

- stebri

- pink

- postavi

- platon

- Platonova podatkovna inteligenca

- PlatoData

- Točka

- Pogled na točko

- mogoče

- Prispevkov

- potencial

- moč

- prej

- problem

- Težave

- Postopek

- obravnavati

- Program

- programirana

- Programiranje

- obetaven

- zagotavljajo

- naključno

- območje

- razmerje

- Preberi

- Rdeča

- Odstranjeno

- Poročila

- zahteva

- obvezna

- Zahteve

- Raziskave

- Odpornost

- Odgovor

- Rezultati

- pregleda

- Pravica

- vloga

- s

- Znanost

- znanstveno

- Oddelek

- polprevodnik

- Polprevodniki

- nastavite

- nastavitve

- Oblikujte

- shouldnt

- pokazale

- strani

- signali

- pomemben

- Simulacija

- Velikosti

- Rešitev

- SOLVE

- vir

- porabljen

- zloženi

- Država

- Države

- Koraki

- shranjevanje

- študiral

- Študije

- študija

- taka

- Podpora

- skupina

- Tehnologija

- Razvoj tehnologije

- kot

- da

- O

- Graf

- Vir

- Država

- njihove

- POTEM

- Tukaj.

- te

- ta

- skozi

- Tako

- čas

- krat

- čas

- do

- vrh

- proti

- tradicionalno

- dva

- tip

- tipičen

- pod

- razumeli

- na žalost

- Enota

- uporaba

- Rabljeni

- uporabo

- Vrednote

- različnih

- Proti

- vertikalno

- navpično

- Video

- Poglej

- Virtual

- vizualizacija

- Napetost

- Obseg

- vs

- je

- we

- webp

- so bili

- kdaj

- medtem

- bele

- pogosto

- bo

- z

- delal

- deluje

- bi

- wu

- let

- zefirnet