Chiplets je poenostavil eno področje oblikovanja, a odprl pandorino skrinjico na drugi strani. Kompleksnost simulacije vsakega čiplet je nižja, zdaj pa je povezava med čipletom postala zapletena. Ljudje eksperimentirajo z različnimi protokoli medsebojnega povezovanja, različicami UCIe, spreminjajo nastavitve UCIe, hitrosti vmesnika, število fizičnih plasti in tako eno. Zdaj mešanici dodajte podedovane standarde, kot je AXI, nove protokole, kot je PICe6.0, in skladnost predpomnilnika.

Skratka, to ustvari popolnoma nov niz poskusov. Tisti, za katerega tradicionalna emulacija in modeliranje RTL ne delujeta. Najprej se morate potruditi pri arhitekturnem kompromisu, ne le pri izbiri komponent. To bo pomenilo, da boste morali izvesti analizo prometa, particioniranje aplikacij, dimenzioniranje sistema in vpliv različnih vrst fizične plasti. Poleg tega se bo merilo uspešnosti zelo razlikovalo glede na aplikacijo.

Specifikacija UCIe je nova in ni jasnih meril. Poleg tega specifikacija UCIe zagotavlja le smernice glede zakasnitve in moči. Oba sta strogi zahtevi. To pomeni, da je študija Power-Performance-Area neizogibna. Ker imate pretvorbo protokol-protokol-protokol, kot je PCIe 6.0 v UCIe v AXI, je nastavitev modeliranja zapletena.

Ena od rešitev je, da si ogledate sistemsko modeliranje z uporabo VisualSim iz mirabilis Oblikovanje. Nedavno so lansirali model IP na ravni sistema UCIe in bodo prikazali številne primere uporabe medsebojnega povezovanja na Chiplet Summit. Za usmerjanje oblikovalcev so objavili vodnik z veliko primeri uporabe, pričakovanimi rezultati glede zmogljivosti in možnostmi optimizacije. Na vrhu imajo tako predstavitev referatov kot stojnico. Upam, da se vidimo tam!

Tukaj je tudi povezava za papir, ki ga lahko ljudje dobijo: Modeliranje zmogljivosti heterogenega računalniškega sistema, ki temelji na UCIe Interconnect Architecture

Povzetek:

Današnje kompleksne zasnove čipov na vodilnih vozliščih so na splošno sestavljene iz več matric (ali čipletov). Pristop omogoča matrice različnih proizvajalcev ali procesov, pa tudi IP za večkratno uporabo. Oblikovalci potrebujejo model sistemske ravni za ovrednotenje različnih izvedb tako zapletenih situacij.

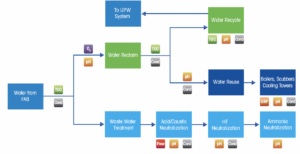

Primer sistema je sestavljen iz V/I čipleta, jedrnega čipleta z nizko porabo energije, visoko zmogljivega jedrnega čipleta, avdio-video čipleta in analognega čipleta, ki so med seboj povezani s standardom Universal Chiplet Interconnect Express (UCIe).

Naša ekipa je upoštevala več scenarijev in konfiguracij, vključno z naprednimi in standardnimi paketi, raznolikimi prometnimi profili in viri ter časovnikom za razširitev dosega in ocenjevanje dogodkov ob časovni omejitvi. Prepoznavanje prednosti in slabosti medsebojne povezave UCIe za aplikacije za misije nam je pomagalo pridobiti optimalno konfiguracijo za vsak podsistem, da bi izpolnili zahteve glede zmogljivosti, moči in funkcionalnosti.

O Mirabilis Design Inc.

Mirabilis Design je programsko podjetje iz Silicijeve doline, ki ponuja programsko opremo in rešitve za usposabljanje za prepoznavanje in odpravljanje tveganj v specifikaciji izdelka, natančno napovedovanje človeških in časovnih virov, potrebnih za razvoj izdelka, in izboljšanje komunikacije med različnimi inženirji.

ekipe.

VisualSim Architect združuje intelektualno lastnino, modeliranje na ravni sistema, simulacijo, analizo okolja in aplikacijske predloge za znatno izboljšanje konstrukcije modela, simulacije, analize in preverjanja RTL. Okolje omogoča načrtovalcem, da se hitro približajo dizajnu, ki izpolnjuje raznolik nabor soodvisnih časovnih in energetskih zahtev. Uporablja se zelo zgodaj v procesu načrtovanja vzporedno s (in kot pomoč) pisni specifikaciji in pred implementacijo (na primer RTL, programska koda ali shema) izdelka.

Preberite tudi:

WEBINAR: Kako doseči 95 %+ natančno merjenje moči med raziskovanjem arhitekture

Preslikava SysML v arhitekturo strojne opreme

Tečaji oblikovanja na podlagi modelov za študente

Delite to objavo prek:

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- PlatoData.Network Vertical Generative Ai. Opolnomočite se. Dostopite tukaj.

- PlatoAiStream. Web3 Intelligence. Razširjeno znanje. Dostopite tukaj.

- PlatoESG. Ogljik, CleanTech, Energija, Okolje, sončna energija, Ravnanje z odpadki. Dostopite tukaj.

- PlatoHealth. Obveščanje o biotehnologiji in kliničnih preskušanjih. Dostopite tukaj.

- vir: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- :ima

- : je

- :ne

- a

- natančna

- natančno

- Doseči

- dodajte

- napredno

- Pomoč

- omogoča

- skupaj

- Prav tako

- an

- Analiza

- in

- Še ena

- uporaba

- aplikacije

- pristop

- Arhitektura

- SE

- OBMOČJE

- AS

- At

- temeljijo

- BE

- postanejo

- pred

- merilo

- meril

- med

- tako

- Pasovi

- vendar

- predpomnilnik

- CAN

- Lahko dobiš

- primeri

- čip

- jasno

- Koda

- združuje

- Komunikacija

- podjetje

- popolnoma

- kompleksna

- kompleksnost

- deli

- računalništvo

- Ravnanje

- konfiguracija

- šteje

- vsebuje

- Gradbeništvo

- zbližati

- Pretvorba

- Core

- tečaji

- ustvari

- dokazuje

- Odvisno

- Oblikovanje

- proces oblikovanja

- oblikovalci

- modeli

- Razvoj

- drugačen

- razne

- med

- vsak

- Zgodnje

- prizadevanje

- odpravo

- emulacija

- omogoča

- okolje

- oceniti

- dogodki

- Primer

- Pričakuje

- eksperimentiranje

- Poskusi

- express

- razširiti

- prva

- za

- iz

- spredaj

- funkcionalno

- splošno

- dobili

- Navodila

- vodi

- strojna oprema

- Imajo

- pomagal

- tukaj

- visokozmogljivo

- upam,

- Kako

- Kako

- HTTPS

- človeškega

- i

- identificirati

- identifikacijo

- vpliv

- Izvajanje

- izvedbe

- izboljšanje

- in

- Vključno

- intelektualne

- intelektualne lastnine

- medsebojno povezani

- vmesnik

- IP

- IT

- jpg

- samo

- Latenca

- začela

- plast

- plasti

- Legacy

- Stopnja

- kot

- LINK

- Poglej

- veliko

- nizka

- nižje

- Proizvajalci

- max širine

- pomeni

- pomeni

- Merjenje

- Srečati

- ustreza

- Mission

- mix

- Model

- modeliranje

- modeliranje

- več

- Nimate

- Novo

- št

- vozlišča

- zdaj

- Številka

- pridobi

- of

- on

- ONE

- samo

- odprite

- odprt

- optimalna

- optimizacija

- možnosti

- or

- pakete

- Papir

- vzporedno

- performance

- fizično

- platon

- Platonova podatkovna inteligenca

- PlatoData

- Prispevek

- moč

- napovedovanje

- predstavitev

- Postopek

- Procesi

- Izdelek

- Profili

- nepremičnine

- protokoli

- zagotavlja

- zagotavljanje

- objavljeno

- hitro

- dosežejo

- Preberi

- Pred kratkim

- obvezna

- Zahteve

- viri

- Rezultati

- za večkratno uporabo

- Tveganje

- scenariji

- glej

- izbiranje

- nastavite

- nastavitve

- nastavitev

- več

- bistveno

- Silicij

- Silicon Valley

- poenostavljeno

- Simulacija

- situacije

- So

- Software

- Rešitev

- rešitve

- specifikacija

- hitrosti

- preživeti

- standardna

- standardi

- prednosti

- stroga

- študija

- taka

- Vrh

- sistem

- skupina

- predloge

- da

- O

- Tukaj.

- jih

- ta

- čas

- do

- tradicionalna

- Prometa

- usposabljanje

- Vrste

- Universal

- us

- uporaba

- Rabljeni

- uporabo

- Valley

- variacije

- Preverjanje

- zelo

- preko

- pomanjkljivosti

- Dobro

- ki

- bo

- z

- delo

- pisni

- jo

- zefirnet