Это было в 1991 что Cadence впервые объявила о названии продукта Virtuoso, и вот мы 32 года спустя, и продукт жив и работает достаточно хорошо. Стивен Льюис из Cadence рассказал мне о чем-то новом, что они называют Виртуозная студия, и все дело в индивидуальном дизайне ИС для реального мира. За эти 32 года мы видели, как полупроводниковый процесс продвигался по закону Мура от 600 нм с использованием планарных КМОП, уменьшался до эпохи FinFET ниже 22 нм, достигая GAA на 3-нм узле. Очевидно, что требования к инструментам EDA изменились, поскольку меньшие узлы привели к новым физическим эффектам, которые необходимо было смоделировать и смоделировать, чтобы обеспечить успех первого кремния.

В центре внимания Cadence Virtuoso Studio — помощь разработчикам интегральных схем в решении современных задач в шести областях:

- Повышенная сложность процесса

- Обработка 10,000 XNUMX симуляций схем

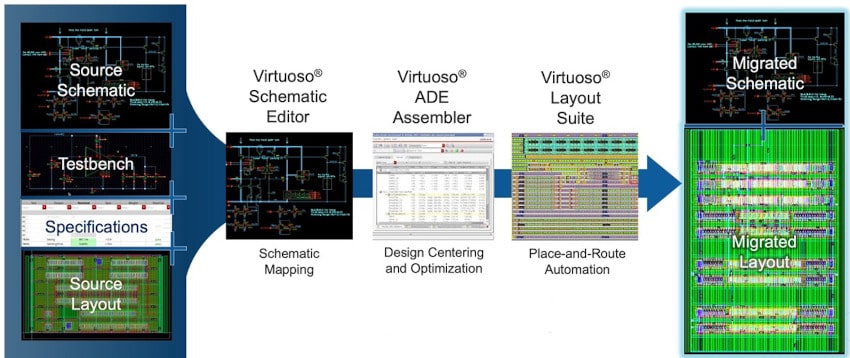

- Автоматизация проектирования и миграция схем

- Гетерогенная интеграция

- AI

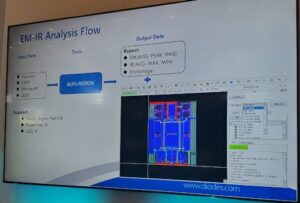

- Подписание, проверка и анализ проекта

Ассоциация Виртуозная АДЭ (Analog Design Environment) позволяет инженерам-схемотехникам исследовать свои аналоговые, смешанные и высокочастотные интегральные схемы с помощью схемы и моделирования. Архитектура Virtuoso ADE была переработана для лучшего управления заданиями, уменьшения использования оперативной памяти и ускорения моделирования за счет использования облака. Например, ОЗУ, необходимое для запуска Spectre на 10,000 420 симуляций, было уменьшено с 18 МБ до всего 420 МБ для мониторинга моделирования, а для оценки выражений ОЗУ уменьшилось с 280 МБ до всего XNUMX МБ.

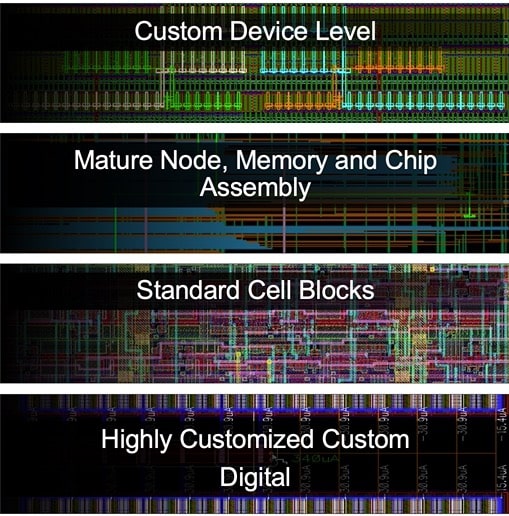

Обновления Набор виртуозных макетов включает четыре варианта места и технологии маршрута, каждый из которых подходит для уникальной задачи в среде Virtuoso:

Четыре технологии P&R

Запуски DRC и LVS являются частью физической проверки, и запуск их в пакетном режиме с исправлением и повторением приводит к длительным графикам разработки. Проверка в проекте позволяет интерактивно использовать DRC и LVS при работе над компоновкой ИС, поэтому отзывы о том, что нужно изменить, быстро выделяются, что повышает производительность. Дизайнер макетов, использующий Virtuoso Layout Suite, выигрывает от проверки в процессе разработки с помощью Pegasus Технология DRC и LVS.

Чиплеты, 2.5D- и 3D-упаковка охватывают традиционно отдельные области проектирования печатных плат, корпусов и интегральных схем. Virtuoso Studio позволяет совместно разрабатывать и проверять пакеты, модули и интегральные схемы:

Заглядывая в ближайшее будущее, вы можете ожидать появления подробностей о том, как ИИ применяется для автоматического перехода от аналоговой схемы к компоновке на основе машинного обучения и спецификаций. Эти автоматически сгенерированные пробные макеты еще больше ускорят очень трудоемкий процесс. Вторая область разработки для применения ИИ — это проблема миграции пользовательского аналогового IP-адреса на новый узел процесса. Следите за обновлениями.

Первыми клиентами Virtuoso Studio являются Analog Devices для совместной разработки ИС и упаковки, передовые потребительские разработки ИС в MediaTek и миграция процессов на основе ИИ в Renesas.

Обзор

Virtuoso Studio добавила в версию 23.1 несколько впечатляющих новых функций, которые могут начать использовать команды разработчиков интегральных схем, чтобы работать более продуктивно. Инфраструктура Virtuoso была изменена, чтобы соответствовать требованиям закона Мура, симуляции цепей за 10,000 2.5 секунд стали практичными, поддерживается совместная разработка RFIC и модуля 3D/XNUMXD, встроенная проверка DRC/LVS занимает гораздо меньше времени, а искусственный интеллект применяется для автоматизации аналоговых задач.

Похожие статьи

Поделитесь этим постом через:- SEO-контент и PR-распределение. Получите усиление сегодня.

- Платоблокчейн. Интеллект метавселенной Web3. Расширение знаний. Доступ здесь.

- Чеканка будущего с Эдриенн Эшли. Доступ здесь.

- Источник: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :имеет

- :является

- $UP

- 1

- 10

- 3d

- a

- О нас

- ускоряющий

- AI

- Все

- позволяет

- вдоль

- и

- объявило

- прикладной

- архитектура

- МЫ

- ПЛОЩАДЬ

- области

- AS

- At

- автоматизировать

- автоматически

- автоматизация

- назад

- основанный

- BE

- было

- не являетесь

- ниже

- Преимущества

- Лучшая

- принес

- by

- Каденция

- призывают

- CAN

- захватить

- проблемы

- изменение

- выбор

- явно

- облако

- потребитель

- контроль

- изготовленный на заказ

- Клиенты

- день

- запросы

- Проект

- дизайнер

- дизайнеры

- конструкций

- подробнее

- Разработка

- Устройства

- дело

- доменов

- вниз

- каждый

- эффекты

- позволяет

- Инженеры

- обеспечивать

- Окружающая среда

- Эпоха

- оценки

- пример

- ожидать

- Больше

- Особенности

- Обратная связь

- First

- Фокус

- Что касается

- 4

- от

- далее

- будущее

- Go

- рука

- Есть

- помощь

- здесь

- Выделенные

- Как

- HTML

- HTTPS

- ICS

- впечатляющий

- in

- включают

- Инфраструктура

- интерактивный

- IP

- работа

- JPG

- труд

- закон

- Планировка

- Лиды

- изучение

- Льюис

- Длинное

- машина

- обучение с помощью машины

- Март

- макс-ширина

- Встречайте

- миграция

- режим

- модуль

- Модули

- Мониторинг

- БОЛЕЕ

- имя

- Возле

- необходимый

- Новые

- Новые функции

- узел

- узлы

- of

- on

- ONE

- пакет

- пакеты

- коробок

- часть

- физический

- Часть

- Платон

- Платон Интеллектуальные данные

- ПлатонДанные

- После

- практическое

- представить

- Проблема

- процесс

- Продукт

- производительный

- производительность

- положил

- быстро

- Оперативная память

- достигнув результата

- реальные

- реальный мир

- Цена снижена

- снижение

- освободить

- обязательный

- дорога

- Run

- Бег

- масштабирование

- Во-вторых

- смотрите подробности

- полупроводник

- отдельный

- кремний

- моделирование

- ШЕСТЬ

- меньше

- So

- некоторые

- удалось

- пролет

- спецификации

- Spectre

- скорость

- Начало

- оставаться

- студия

- успех

- suite

- Поддержанный

- взять

- принимает

- Сложность задачи

- задачи

- команды

- Технологии

- который

- Ассоциация

- их

- Эти

- Через

- время

- в

- инструментом

- Традиционно

- суд

- созданного

- Обновление ПО

- Применение

- использование

- проверка

- с помощью

- ЧТО Ж

- Что

- в то время как

- будете

- работает

- Мир

- лет

- зефирнет