Старая фраза о том, что лекарство хуже болезни, уместна при обсуждении MBIST для крупных SOC, где параллельное выполнение многих тестов MBIST может превысить возможности сети распределения питания (PDN). Встроенная самопроверка памяти (MBIST) обычно запускается автоматически при включении питания. Из-за желания ускорить тесты и время загрузки чипа эти тесты часто выполняются параллельно. Проблема в том, что они могут легко производить коммутационную активность, которая на порядок выше уровней, обнаруживаемых при обычной работе микросхемы. Действительно, эти более высокие уровни коммутационной активности могут не только вызвать падение напряжения питания, влияющее на результаты испытаний, но и сильное выделение тепла может повредить микросхемы. Эти эффекты могут привести к неправильному биннингу или к прямым и скрытым отказам.

Решение состоит в моделировании активности MBIST для прогнозирования нагрузки на PDN и связанных с ней тепловых эффектов. Имея результаты моделирования, разработчики могут правильно решить, сколько и какие блоки памяти можно тестировать параллельно. Однако это не всегда возможно в больших SOC с большим количеством блоков памяти, поскольку время моделирования может быть непомерно высоким. С уровнем ворот и даже менее точным моделированием RTL может оказаться невозможным выполнить достаточное количество циклов для получения необходимой информации.

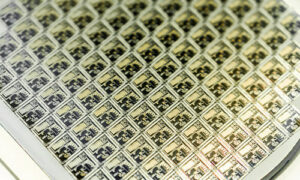

В официальном документе под названием «Анализ последствий использования MBIST для энергопотребления» Siemens EDA рассматривает, как разработчики могут провести достаточное моделирование, чтобы принять обоснованные решения о стратегии тестирования перед лентой. Siemens работала с ARM над одним из своих тестовых чипов, чтобы создать тестовый пример, в котором они могли применить аппаратную эмуляцию с помощью приложений DFT и Power для аппаратного эмулятора Siemens Veloce. Во-первых, приложение Veloce DFT используется для вывода внутренней активности во время эмуляции MBIST. Приложение использует стандартный язык тестового интерфейса (STIL) и создает стандартные выходные файлы.

Приложение Veloce Power берет информацию об активности из прогонов MBIST для создания кривых, профилей мощности и тепловых карт, которые могут указывать на пики мощности, превышающие указанные пределы. С помощью этой информации инженеры-испытатели могут принимать обоснованные решения о последовательности MBIST.

Тестовый пример ARM, описанный в официальном документе Siemens, содержит 176 миллионов логических элементов. В этом тестовом примере компания Siemens использовала систему Veloce с 6 платами Veloce Strato. Запуск эмулятора Veloce занял всего 26 часов, что в 15,600 XNUMX раз быстрее, чем моделирование на уровне ворот. Еще одним преимуществом потока Veloce является то, что приложение Power передает информацию об активности в потоковом режиме на электроинструменты в потоке, экономя дисковое пространство и время. Результаты тестов показали несколько всплесков мощности, которые нарушили проектные спецификации SOC. Выходные данные приложения Veloce Power показывают общие уровни мощности в результате моделирования, а также отдельные вклады мощности для часов, комбинационной логики и памяти. Точно так же есть информация о том, где на кубике используется мощность. Эта информация позволяет легко определить, где есть проблемы.

Поиск таких проблем требует выполнения миллионов или миллиардов тактов. Ограничения программных симуляторов делают невозможным выполнение необходимого анализа. Эмуляция предлагает уникальный способ тщательного изучения влияния MBIST и других тестовых операций на электроэнергию задолго до кремния. Технический документ Siemens дает представление о методе мощности, используемом в реальном тестовом примере. Технический документ доступен для загрузки для чтения на веб-сайте Siemens.

Поделитесь этим постом через: Источник: https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- О нас

- анализ

- приложение

- Программы

- ARM

- доступен

- не являетесь

- Вызывать

- чип

- чипсы

- Часы

- содержит

- может

- лечение

- Проект

- Болезнь

- в течение

- легко

- Инженеры

- События

- События

- быстрее

- First

- поток

- найденный

- ворота

- порождать

- Аппаратные средства

- High

- Как

- HTTPS

- промышленность

- информация

- IT

- язык

- большой

- вести

- уровень

- уровни

- загрузка

- Длинное

- Карты

- миллиона

- миллионы

- необходимый

- сеть

- Предложения

- Операционный отдел

- заказ

- Другое

- бумага & картон

- мощностью

- Проблема

- Профили

- Reading

- Итоги

- Run

- Бег

- экономия

- Сименс

- моделирование

- Software

- Space

- скорость

- Стратегия

- потоковый

- поставка

- система

- тестXNUMX

- Тестирование

- тестов

- тепловой

- Через

- время

- инструменты

- созданного

- обычно

- Вебсайт

- технический документ

- работавший