С момента своего дебюта в 1980-х годах с общими локальными сетями со скоростью 10 Мбит/с по коаксиальным кабелям Ethernet постоянно развивался, и теперь он потенциально может поддерживать скорости до 1.6 Тбит/с. Этот прогресс позволил Ethernet обслуживать более широкий спектр приложений, таких как потоковая передача в реальном времени, сети радиодоступа и промышленное управление, подчеркивая важность надежной передачи пакетов и качества обслуживания. Учитывая, что в настоящее время пропускная способность Интернета достигает ~500 Тбит/с, растет потребность в улучшенной внутренней обработке трафика внутри центра обработки данных. Хотя отдельные серверы еще не работают на уровне терабит в секунду, общий трафик центров обработки данных приближается к этому масштабу, что побуждает группу IEEE 802.3dj предпринять усилия по стандартизации и требует надежных контроллеров Ethernet и SerDes для управления расширяющимся потоком данных. На фоне растущих требований межпроцессорная связь уже достигает этих скоростей.

Межпроцессорная связь приводит к необходимости скоростей 1.6T с минимальной задержкой. Хотя отдельные устройства ограничены присущими им вычислительными мощностями и размером чипа, объединение чипов может значительно расширить эти возможности. Ожидается, что за первым поколением приложений последуют межкоммутационные соединения внутри центров обработки данных, что позволит объединить высокопроизводительные процессоры и память, повысив масштабируемость и эффективность облачных вычислений.

Инициатива IEEE 802.3dj: развитие стандартов Ethernet для обеспечения совместимости со скоростью 1.6 Тбит/с

Соответствие развивающимся усилиям по стандартизации имеет решающее значение для бесперебойной совместимости экосистем. Группа IEEE 802.3dj находится в процессе разработки будущего стандарта Ethernet, который будет охватывать физические уровни и параметры управления для скоростей от 200G до 1.6 Терабит в секунду. Целью группы является скорость передачи данных Ethernet MAC 1.6 Тбит/с, стремясь к тому, чтобы максимальная частота битовых ошибок не превышала 10–13 на уровне MAC. Дополнительные возможности включают в себя дополнительные 16- и 8-полосные интерфейсы модулей подключения (AUI), подходящие для различных приложений микросхем, с использованием SerDes 112G и 224G. Физически спецификация 1.6 Тбит/с предполагает передачу через 8 пар медных твинаксиальных кабелей на расстояние до одного метра и 8 пар оптоволокна на расстояния от 500 метров до 2 км. Хотя полная ратификация стандарта ожидается к весне 2026 года, основной набор функций планируется завершить к 2024 году.

Накладные расходы на полосу пропускания и коррекция ошибок в подсистемах Ethernet 1.6T

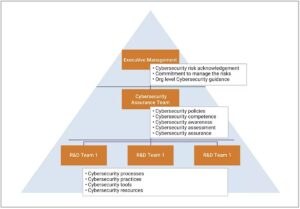

Рис. 1: Схема, изображающая компоненты подсистемы Ethernet 1.6T.

В более ранних итерациях Ethernet PCS в первую очередь фокусировалась на кодировании данных для надежного обнаружения пакетов. Однако с переходом на скорости Ethernet 1.6T необходимость в прямой коррекции ошибок (FEC) становится очевидной, особенно для противодействия ухудшению сигнала даже на коротких каналах. Для этой цели 1.6T Ethernet продолжает использовать FEC Рида-Соломона. Этот подход создает кодовое слово, содержащее 514 10-битных символов, закодированных в блок из 544 символов, что приводит к увеличению нагрузки на полосу пропускания на 6%. Эти кодовые слова FEC распределяются по физическим каналам AUI, так что каждый физический канал (8 для Ethernet 1.6T) не несет в себе целое кодовое слово. Этот метод не только обеспечивает дополнительную защиту от пакетов ошибок, но также обеспечивает распараллеливание на дальнем конце декодера, тем самым уменьшая задержку.

Приложение Physical Medium Attachment (PMA), оснащенное редуктором и SerDes, передает сигнал Ethernet на передаваемые каналы. Для Ethernet 1.6T это включает 8 каналов, каждый из которых работает со скоростью 212 Гбит/с, что составляет 6 % накладных расходов FEC. Используемый метод модуляции представляет собой 4-уровневую импульсно-амплитудную модуляцию (PAM-4), которая кодирует два бита данных для каждого символа передачи, тем самым эффективно удваивая полосу пропускания в сочетании с традиционным подходом без возврата нуля (NRZ). Механизм передачи основан на цифро-аналоговом преобразовании, а на приемной стороне аналого-цифровое преобразование в сочетании с DSP обеспечивает точное извлечение сигнала.

Кроме того, важно отметить, что Ethernet PCS вводит «внешний FEC», который охватывает сквозной канал Ethernet. Для поддержки каналов с большей досягаемостью в разработке находится дополнительный уровень коррекции ошибок для отдельных физических линий, вероятно, с использованием кода Хэмминга FEC. Ожидается, что эта коррекция найдет свое основное применение в модулях оптических приемопередатчиков, где такая коррекция обязательна.

Рис. 2. Диаграмма, показывающая дополнительные накладные расходы, добавляемые при использовании объединенного FEC для расширенного охвата.

В примерной системе, изображенной на рисунке 2, MAC и PCS соединены через оптический модуль и оптоволоконный участок. PCS имеет коэффициент ошибок по битам 10.-5 по каналу оптического модуля плюс ошибки самого оптического канала. Использование одного сквозного RS-FEC недостаточно для достижения 10-13 Стандарт Ethernet, что делает соединение ненадежным. Альтернативой может быть тройная реализация отдельного RS FEC на каждом прыжке, что значительно увеличит затраты и задержку. Более эффективным решением является интеграция каскадного кода Хэмминга FEC специально для оптического канала, учитывающего типичные случайные ошибки оптических соединений. Этот внутренний уровень FEC создает дополнительное расширение скорости линии с 212 Гбит/с до 226 Гбит/с, поэтому важно, чтобы SerDes мог поддерживать эту скорость линии.

Проблемы с задержкой в системах Ethernet 1.6T

Рис. 3: Путь задержки для подсистемы Ethernet 1.6T.

На задержку Ethernet влияют различные компоненты: очередь передачи, продолжительность передачи, время прохождения среды, а также несколько времен обработки и приема. Чтобы представить это, рассмотрим рисунок 3, на котором показана комплексная подсистема Ethernet 1.6T. Хотя на задержку может влиять время реакции удаленного приложения, этот фактор является внешним по отношению к Ethernet и поэтому часто исключается при анализе задержки. Минимизация задержки на интерфейсе Ethernet требует понимания конкретных обстоятельств. Например, задержка может не быть основной проблемой для магистральных соединений между коммутаторами из-за задержек, присущих более медленным клиентским каналам. Расстояние также играет роль; большая длина приводит к большей задержке. Конечно, это не означает, что мы должны игнорировать задержку в других сценариях: уменьшение задержки всегда является целью.

Задержка передачи по своей сути привязана к скорости Ethernet и размеру кадра. В частности, для системы Ethernet 1.6T передача пакета минимального размера требует 0.4 нс — по сути, один кадр Ethernet за такт тактовой частоты 2.5 ГГц. С другой стороны, передача стандартного кадра максимального размера занимает 8 нс, а для больших кадров — 48 нс. Выбранная среда дополнительно определяет задержку. Например, оптическое волокно обычно имеет задержку 5 нс на метр, тогда как медный кабель немного быстрее — 4 нс на метр.

Значительная часть общей задержки связана с контроллером приемника. Декодер RS FEC по своей сути вносит задержку. Чтобы инициировать исправление ошибок, система должна получить 4 кодовых слова, что при скорости 1.6 Тбит/с составляет 12.8 нс. Последующие действия, включая исправление ошибок и буферизацию, увеличивают эту задержку. Хотя продолжительность хранения кодового слова FEC остается постоянной, задержка во время приема сообщения зависит от конкретной реализации. Тем не менее, задержку можно оптимизировать, используя тщательно продуманные стратегии цифрового проектирования.

По сути, существует неизбежная задержка, обусловленная механизмом FEC и физическим расстоянием или длиной кабеля. Помимо этих факторов, ключевую роль в минимизации задержки контроллера Ethernet играет опыт проектирования. Использование комплексного решения, которое интегрирует и оптимизирует MAC, PCS и PHY, открывает путь к наиболее эффективной реализации с низкой задержкой.

Обзор

Рис. 4. Успех первого прохождения кремния для Synopsys 224G Ethernet PHY IP, выполненного по 3-нм техпроцессу, демонстрирующий высоколинейные глаза PAM-4.

Ethernet со скоростью 1.6 Тбит/с предназначен для приложений, наиболее требовательных к полосе пропускания и чувствительных к задержке. С появлением технологии 224G SerDes в сочетании с достижениями в области MAC и PCS IP теперь доступны комплексные решения, которые постоянно соответствуют развивающимся стандартам 1.6T Ethernet. Кроме того, из-за задержки, присущей протоколу, и методам исправления ошибок, цифровая и аналоговая конструкция IP должна тщательно разрабатываться опытными разработчиками, чтобы избежать ненужной задержки в тракте данных.

Достижение максимальной производительности для конструкций SoC 1.6T требует эффективно оптимизированной архитектуры и тщательного проектирования каждого компонента чипа. Это подчеркивает экономию энергии и сводит к минимуму площадь кремния, делая скорость передачи данных 1.6 Тл реальностью. Проверенный на базе кремния Synopsys 224G Ethernet PHY IP подготовила почву для 1.6T MAC и контроллера PCS. Используя передовые методы проектирования, анализа, моделирования и измерения, Synopsys продолжает обеспечивать исключительную целостность сигнала и характеристики джиттера, обеспечивая комплексное решение Ethernet, включая MAC+PCS+PHY.

- SEO-контент и PR-распределение. Получите усиление сегодня.

- PlatoData.Network Вертикальный генеративный ИИ. Расширьте возможности себя. Доступ здесь.

- ПлатонАйСтрим. Интеллект Web3. Расширение знаний. Доступ здесь.

- ПлатонЭСГ. Углерод, чистые технологии, Энергия, Окружающая среда, Солнечная, Управление отходами. Доступ здесь.

- ПлатонЗдоровье. Биотехнологии и клинические исследования. Доступ здесь.

- Источник: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :имеет

- :является

- :нет

- :куда

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- доступ

- доступной

- Бухгалтерский учет

- точный

- Достигать

- через

- активно

- добавленный

- дополнительный

- Дополнительно

- Принятие

- достижения

- опережения

- против

- Стремясь

- разрешено

- уже

- причислены

- Несмотря на то, что

- всегда

- среди

- суммы

- усиливать

- an

- анализ

- и

- Ожидаемый

- Применение

- Приложения

- подхода

- архитектура

- МЫ

- AS

- At

- избежать

- Back-конец

- задник

- Пропускная способность

- BE

- становится

- между

- Beyond

- Немного

- Заблокировать

- поддерживать

- стимулирование

- Приносит

- строит

- но

- by

- кабель

- Кабели

- CAN

- мощности

- нести

- проблемы

- каналы

- чип

- чипсы

- выбранный

- обстоятельства

- клиент

- Часы

- облако

- облачных вычислений

- код

- сочетании

- комбинируя

- Связь

- полный

- завершение

- компонент

- компоненты

- комплексный

- содержащий

- вычисление

- Беспокойство

- связь

- подключенный

- Коммутация

- СОХРАНЕНИЕ

- Рассматривать

- соображения

- последовательный

- продолжается

- непрерывно

- способствовать

- контроль

- контроллер

- Конверсия

- Медь

- Основные

- Расходы

- противодействовать

- курс

- проработаны

- создает

- Текущий

- данным

- Datacenter

- дебют

- задержки

- доставить

- Спрос

- требующий

- запросы

- изображающая

- Проект

- дизайнеры

- конструкций

- обнаружение

- Устройства

- диктат

- различный

- Интернет

- старательно

- дисплеев

- расстояние

- распределенный

- не

- удвоившись

- два

- продолжительность

- в течение

- каждый

- Ранее

- экосистема

- Эффективный

- фактически

- затрат

- эффективный

- эффективно

- усилия

- появление

- подчеркивает

- подчеркивающий

- занятых

- используя

- позволяет

- позволяет

- охватывает

- конец

- впритык

- обеспечивает

- Весь

- ошибка

- ошибки

- эскалация

- сущность

- существенный

- по существу

- Эфир (ETH)

- Даже

- Каждая

- очевидный

- развивается

- пример

- исключительный

- исключенный

- расширяющийся

- расширение

- ожидаемый

- эксперту

- опыта

- продлить

- простирающийся

- и, что лучший способ

- добыча

- Глаза

- фактор

- факторы

- далеко

- быстрее

- Особенности

- Показывая

- фигура

- Найдите

- Во-первых,

- Первое поколение

- поток

- внимание

- следует

- след

- Что касается

- формулирование

- вперед

- КАДР

- от

- далее

- поколение

- дает

- большой

- группы

- Группы

- Рост

- рука

- Управляемость

- High

- высокая производительность

- очень

- Однако

- HTML

- HTTPS

- императив

- реализация

- значение

- важную

- улучшенный

- in

- В других

- включают

- В том числе

- повышение

- individual

- промышленность

- влияние

- свойственный

- по существу

- инициировать

- Инициатива

- пример

- Интегрируется

- интеграции.

- целостность

- Интерфейс

- интерфейсы

- Интернет

- Взаимодействие

- в

- внутренний

- вводить

- Представляет

- введение

- включает в себя

- IP

- IT

- итерации

- ЕГО

- саму трезвость

- JPG

- Переулок

- Задержка

- слой

- слоев

- Длина

- уровни

- Используя

- Вероятно

- линия

- линий

- LINK

- связи

- жить

- дольше

- Низкий

- макинтош

- Создание

- управлять

- управление

- макс-ширина

- максимальный

- Май..

- значить

- измерение

- механизм

- средний

- Память

- сообщение

- метод

- методы

- дотошный

- минимальный

- минимизировать

- сводит к минимуму

- минимизация

- модуль

- Модули

- БОЛЕЕ

- самых

- должен

- приближается

- Необходимость

- сетей

- Тем не менее

- нет

- в своих размышлениях

- сейчас

- цель

- of

- .

- on

- ONE

- только

- операционный

- оптимизированный

- оптимизирует

- Опция

- or

- Другое

- за

- общий

- пар

- параметры

- особенно

- путь

- ПК

- для

- производительность

- выступления

- физический

- Физически

- трубопровод

- основной

- Платон

- Платон Интеллектуальные данные

- ПлатонДанные

- играет

- плюс

- потенциал

- мощностью

- практиками

- в первую очередь

- первичный

- процесс

- обработка

- процессоры

- прогрессия

- прогнозируемых

- защиту

- протокол

- импульс

- цель

- Нажимать

- Радио

- случайный

- ассортимент

- Обменный курс

- Стоимость

- достигать

- достигнув результата

- реакция

- Реальность

- Получать

- получение

- прием

- снижение

- складская

- остатки

- оказание

- требуется

- ограниченный

- в результате

- надежный

- Роли

- укоренившийся

- Бег

- Масштабируемость

- Шкала

- Сценарии

- бесшовные

- Во-вторых

- видел

- сегмент

- чувствительный

- отдельный

- служить

- обслуживание

- набор

- несколько

- общие

- Короткое

- должен

- Showcasing

- сигнал

- существенно

- кремний

- моделирование

- Размер

- So

- Решение

- Решения

- пролеты

- возглавляет

- конкретный

- конкретно

- Спецификация

- скорость

- весна

- Этап

- стандарт

- стандартизация

- стандартов

- диск

- стратегий

- потоковый

- последующее

- существенный

- успех

- такие

- подходящее

- поддержка

- символ

- система

- с учетом

- принимает

- техника

- снижения вреда

- Технологии

- чем

- который

- Ассоциация

- их

- Там.

- тем самым

- следовательно

- Эти

- этой

- Через

- Таким образом

- клещ

- Связанный

- время

- раз

- в

- топ

- традиционный

- трафик

- перевод

- передавать

- Тройной

- два

- типичный

- типично

- неизбежный

- понимание

- предпринимать

- Ед. изм

- Предстоящие

- на

- через

- использовать

- с помощью

- визуализации

- Путь..

- we

- когда

- который

- в то время как

- Шире

- в

- бы

- еще

- зефирнет

- нуль