В терминологии интегральных схем падение напряжения — это падение напряжения, происходящее в цепи. Это хорошо известное явление, и оно может произойти по следующим причинам. Напряжение питания падает ниже рабочего диапазона, на который рассчитан чип, что приводит к падению напряжения. Проводящие элементы потребляют больше тока, чем было рассчитано, что приводит к падению напряжения. Иногда помехи сигнала или шум в источнике питания также могут вызывать колебания напряжения, приводящие к его падению.

Спады могут повлиять на работу схемы. Одним из таких последствий является снижение производительности чипа, приводящее к увеличению времени обработки. Но ниже приведены некоторые из наиболее серьезных и/или катастрофических последствий. Чип может потреблять больше тока для поддержания уровня производительности, что приводит к увеличению энергопотребления и рассеивания тепла. Это может привести к сокращению срока службы чипа, а в тяжелых случаях — к его полному выходу из строя из-за изменений в настройке и фиксации. Провисания также могут привести к повреждению данных или ошибкам в выводе. Это очень серьезная проблема для приложений, которые зависят от точности и надежности чипа.

Естественно, явление провалов серьезно учитывается при проектировании микросхем и систем. Наиболее распространенными методами уменьшения провалов являются развязка источника питания, регулирование напряжения, оптимизация схемы и управление питанием на уровне системы. При разработке решений по снижению провалов тщательно учитываются условия и операционная среда, в которых будет работать чип.

Современные проблемы

Поскольку SoC становятся более сложными, проблемы с падением производительности также могут стать довольно сложными. Конструкция SoC должна быть оптимизирована с точки зрения производительности, мощности, стоимости, форм-фактора и т. д., а также оптимизации для предотвращения провалов. Иногда эти цели оптимизации могут конкурировать друг с другом и идти вразрез, и приходится идти на компромисс. Например, разработчики SoC могут повысить рабочее напряжение, добавив запас, чтобы обойти локальный и глобальный спад, но это повышение приводит к квадратичному увеличению мощности. В качестве альтернативы разработчики могут адаптировать генерацию тактовой частоты к спаду, что делает производительность функцией времени переключения генерации тактовой частоты.

Следовательно, крупные SoC в вычислительных центрах центров обработки данных и в сфере искусственного интеллекта особенно подвержены спадам. Рабочие нагрузки клиентов очень разнообразны и динамичны, что приводит к значительным колебаниям активности коммутации и потребления тока. Конечно, системы не могут позволить себе оставить без внимания проблемы с падением производительности. Потенциальная ответственность за неточные выходные данные или катастрофический отказ микросхемы слишком высока для сегодняшних систем и приложений.

Локализованные проблемы с провисанием

Ускорители для конкретных приложений широко используются в сочетании с процессорами общего назначения для обеспечения производительности и энергоэффективности, необходимых в современных требовательных вычислительных средах. Но эти ускорители, а также растущее количество ядер и асимметричный характер рабочих нагрузок увеличивают риск локальных провалов напряжения. Эти локальные падения напряжения являются результатом внезапного увеличения коммутационной активности и могут вызвать временные сбои и потенциальные сбои в режиме работы.

При возникновении локального спада влияние можно смягчить за счет динамического масштабирования частоты. Это достигается путем регулировки времени схемы с помощью программируемых часов. Программируемые часы позволяют динамически регулировать тактовую частоту и синхронизацию в зависимости от текущих условий работы схемы.

Movellus упрощает устранение локальных провисаний

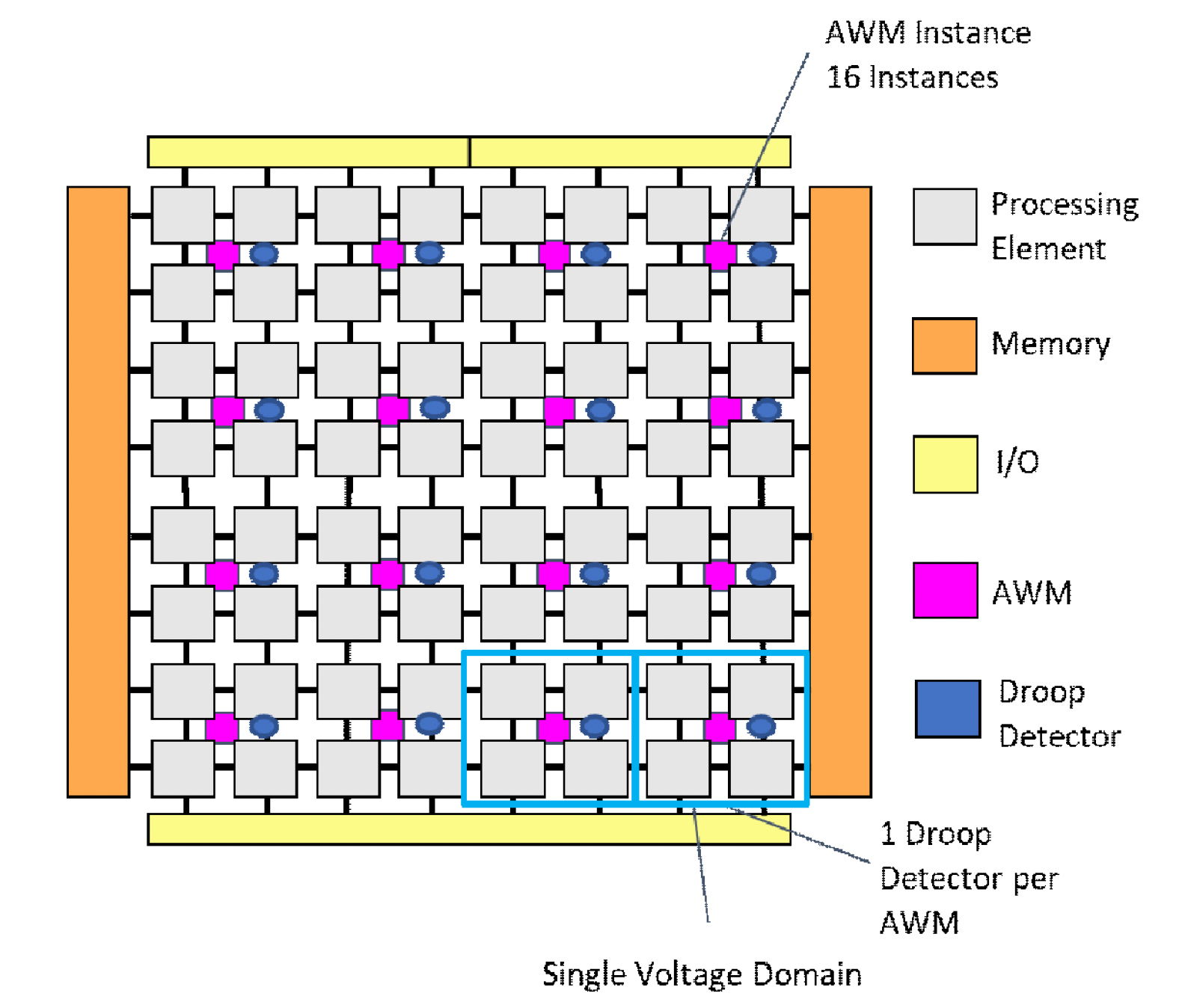

Компания Movellus, ведущий поставщик цифровых систем IP, разработала семейство продуктов Aeonic Generate для устранения локальных сбоев. Портфолио Movellus Aeonic предлагает решения для адаптивной синхронизации, которые обеспечивают быструю реакцию на падение частоты. В портфолио имеется адаптивная система синхронизации. Строительные блоки построены на синтезируемом Verilog, что делает их чрезвычайно гибкими. Решения являются настраиваемыми, сканируемыми и переносимыми для широкого спектра современных приложений SoC.

Семейство продуктов Aeonic Generate также значительно меньше традиционных аналоговых решений. В результате проектировщики могут создавать экземпляры IP с необходимой степенью детализации без какого-либо существенного влияния на область. Кроме того, по мере перехода к более тонкой геометрии процесса область Aeonic Generate продолжает масштабироваться, что делает ее идеальным решением для будущих проектов.

Несколько вариантов использования

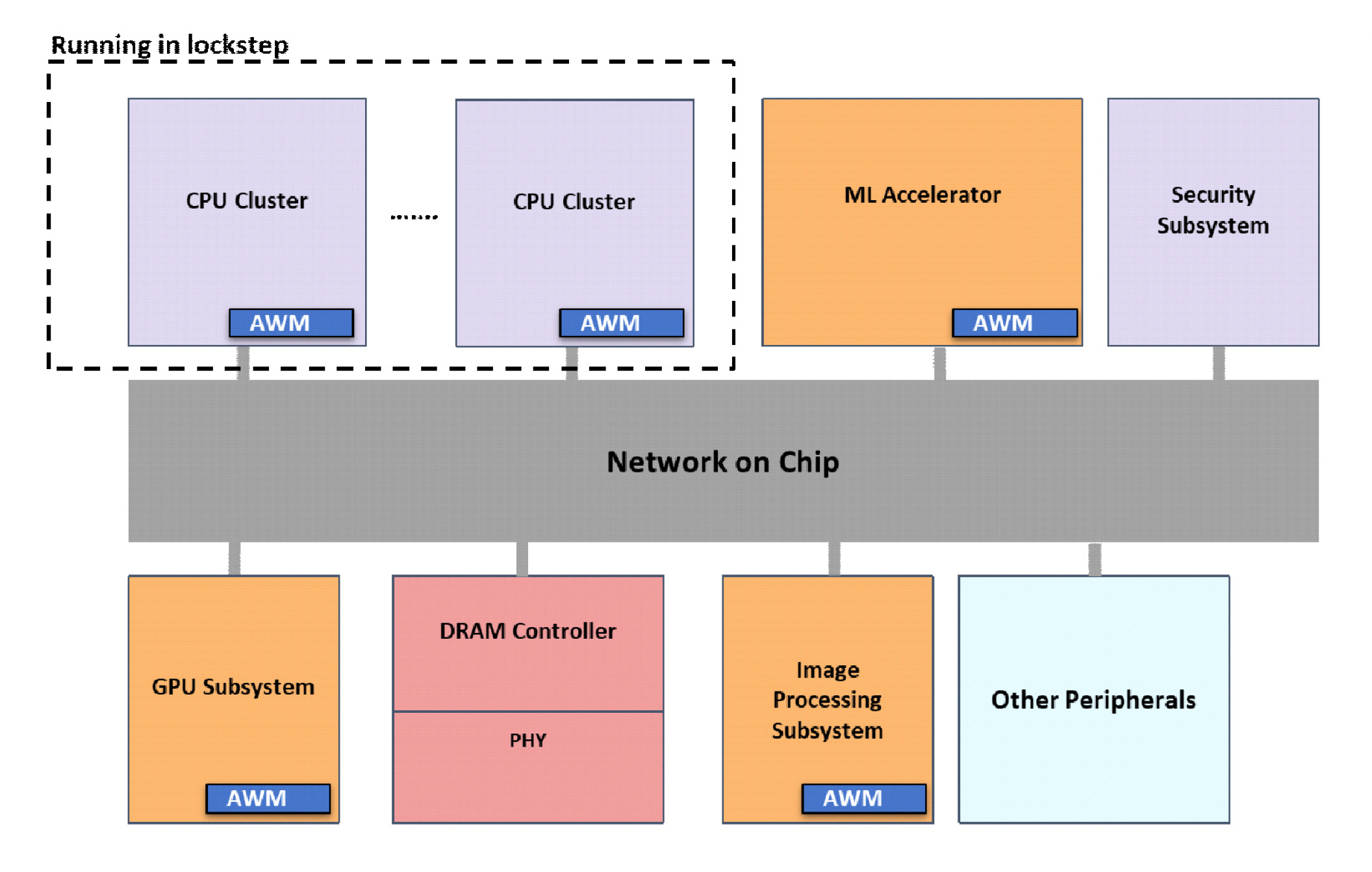

На следующем рисунке от Movellus показан пример архитектуры процессора ADAS с платформой Aeonic Generate AWM для поддержки локализованного падения. Архитектор соединяет модуль AWM с подблоком или ускорителем для конкретного приложения, чтобы реагировать на локальные провалы, вызванные рабочей нагрузкой, в течение пяти тактовых циклов с быстрыми сдвигами частоты без сбоев. Этот подход обеспечивает надежное и эффективное решение для решения проблем локализованных сбоев на рынках ADAS, 5G и сетей центров обработки данных.

На следующем рисунке от Movellus показан пример архитектуры процессорного SoC с Aeonic Generate для локализованной поддержки провалов. Архитектор соединит модуль Aeonic Generate AWM с детектором падения напряжения для кластера процессоров и соответствующей областью напряжения, чтобы быстро реагировать на локальные падения напряжения, вызванные рабочей нагрузкой. Это позволяет разработчикам обеспечить локализованную и независимую реакцию на падение производительности без изменения производительности соседних кластеров процессоров.

Обзор

Локализованные провалы напряжения могут возникать в гетерогенных SoC, содержащих ускорители для конкретных приложений. Эти спады могут привести к сбоям синхронизации, временным сбоям и сбоям в режиме миссии в ADAS, сетях центров обработки данных и приложениях 5G. Системные архитекторы могут реализовать адаптивную синхронизацию, чтобы реагировать на эти спады и смягчать их последствия.

Семейство высокопроизводительных IP-продуктов для генерации тактовых импульсов Movellus™ Aeonic Generate Adaptive Workload Module (AWM) является частью архитектуры Aeonic Intelligent Clock Network™. Для получения дополнительной информации обратитесь к Movellus'у. Страница Aeonic Generate™ AWM.

Читайте также:

Пришло время для сетей умных часов

Преимущества производительности, мощности и площади (PPA) благодаря интеллектуальным тактовым сетям

Поделитесь этим постом через:- SEO-контент и PR-распределение. Получите усиление сегодня.

- Платоблокчейн. Интеллект метавселенной Web3. Расширение знаний. Доступ здесь.

- Источник: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :является

- 5G

- a

- ускоритель

- ускорители

- точность

- достигнутый

- деятельность

- приспосабливать

- АДА

- дополнение

- Дополнительно

- адрес

- адресация

- Отрегулированный

- продвинутый

- AI

- позволяет

- и

- Приложения

- подхода

- архитектура

- МЫ

- ПЛОЩАДЬ

- AS

- связанный

- At

- основанный

- BE

- становиться

- ниже

- Преимущества

- Заблокировать

- Блоки

- Строительство

- построенный

- by

- CAN

- Может получить

- не могу

- осторожно

- случаев

- катастрофический

- Вызывать

- Центр

- проблемы

- чип

- чипсы

- Часы

- Кластер

- Общий

- конкурировать

- полный

- комплекс

- Вычисление

- вычисление

- Условия

- рассмотрение

- считается

- потребление

- продолжается

- коррупция

- Цена

- может

- счетчик

- Пара

- курс

- Текущий

- клиент

- циклы

- данным

- Центр обработки данных

- Datacenter

- день

- доставить

- требующий

- Проект

- предназначенный

- дизайнеры

- проектирование

- конструкций

- развитый

- Интернет

- распределенный

- Разное

- домен

- доменов

- обращается

- Падение

- Капли

- динамический

- динамично

- каждый

- затрат

- эффективный

- элементы

- Окружающая среда

- средах

- ошибки

- и т.д

- пример

- Ошибка

- Водопад

- семья

- фигура

- гибкого

- колебания

- после

- Что касается

- форма

- частота

- от

- функция

- будущее

- общее назначение

- порождать

- поколение

- получить

- Глобальный

- Go

- Цели

- происходить

- происходит

- Есть

- High

- высокая производительность

- держать

- HTTPS

- идеальный

- Влияние

- Воздействие

- осуществлять

- in

- неточный

- включает в себя

- Увеличение

- расширились

- Увеличивает

- повышение

- независимые

- информация

- интегрированный

- интеграции.

- Умный

- в действительности

- IP

- вопрос

- вопросы

- IT

- большой

- крупномасштабный

- вести

- ведущий

- уровень

- ответственность

- ЖИЗНЬЮ

- локальным

- дольше

- сделанный

- поддерживать

- ДЕЛАЕТ

- Создание

- управление

- Маржа

- Области применения:

- макс-ширина

- методы

- смягчать

- смягчающим

- смягчение

- модуль

- Модули

- БОЛЕЕ

- самых

- двигаться

- природа

- потребности

- сеть

- сетей

- Шум

- особенно

- номер

- of

- Предложения

- on

- ONE

- операционный

- Операционный отдел

- оптимизация

- оптимизированный

- оптимизирующий

- Другие контрактные услуги

- выходной

- часть

- производительность

- выполнения

- явление

- Платформа

- Платон

- Платон Интеллектуальные данные

- ПлатонДанные

- «портфель»

- После

- потенциал

- мощностью

- Напряжение питания

- процесс

- обработка

- процессор

- процессоры

- Продукция

- Недвижимости

- приводит

- повышение

- ассортимент

- быстро

- быстро

- Читать

- реального времени

- причины

- Цена снижена

- "Регулирование"

- надежность

- складская

- обязательный

- Реагируйте

- ответ

- результат

- в результате

- Рост

- Снижение

- Run

- Шкала

- масштабирование

- МОРЕ

- серьезный

- установка

- тяжелый

- Смены

- Шоу

- сигнал

- значительный

- существенно

- меньше

- умный

- Решение

- Решения

- некоторые

- Space

- такие

- внезапный

- поставка

- поддержка

- восприимчивый

- система

- системы

- Тандем

- Технологии

- терминология

- который

- Ассоциация

- Местоположение

- их

- Их

- Эти

- Через

- время

- раз

- синхронизация

- в

- Сегодняшних

- слишком

- традиционный

- использование

- очень разнообразный

- с помощью

- напряжение

- ЧТО Ж

- известный

- который

- широкий

- Широкий диапазон

- широко

- будете

- в

- без

- бы

- зефирнет