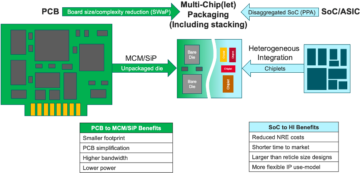

Experți la masă: Ingineria semiconductorilor s-au așezat pentru a vorbi despre calea de urmat pentru memorie în sistemele din ce în ce mai eterogene, cu Frank Ferro, director de grup, management de produs la Cadenţă; Steven Woo, coleg și distins inventator la Rambus; Jongsin Yun, tehnolog de memorie la Siemens EDA; Randy White, manager de programe pentru soluții de memorie la Keysight; și Frank Schirrmeister, vicepreședinte pentru soluții și dezvoltare de afaceri la Arteris. Ceea ce urmează sunt fragmente din acea conversație. Prima parte a acestei discuții poate fi găsită aici.

![[LR]: Frank Ferro, Cadence; Steven Woo, Rambus; Jongsin Yun, Siemens EDA; Randy White, Keysight; și Frank Schirrmeister, Arteris.](https://platoaistream.com/wp-content/uploads/2024/01/rethinking-memory.png)

[LR]: Frank Ferro, Cadence; Steven Woo, Rambus; Jongsin Yun, Siemens EDA; Randy White, Keysight; și Frank Schirrmeister, Arteris

SE: Pe măsură ce ne luptăm cu AI/ML și cu cerințele de putere, ce configurații trebuie regândite? Vom vedea o schimbare de la arhitectura Von Neumann?

Woo: În ceea ce privește arhitecturile de sistem, există o bifurcare în industrie. Aplicațiile tradiționale care sunt calii de muncă dominanti, pe care le rulăm în cloud pe servere bazate pe x86, nu dispar. Există zeci de ani de software care a fost construit și evoluat și care se va baza pe acea arhitectură pentru a funcționa bine. Prin contrast, AI/ML este o clasă nouă. Oamenii au regândit arhitecturile și au construit procesoare foarte specifice domeniului. Vedem că aproximativ două treimi din energie este cheltuită doar pentru a muta datele între un procesor și un dispozitiv HBM, în timp ce doar aproximativ o treime este cheltuită pentru accesarea efectivă a biților din nucleele DRAM. Mișcarea datelor este acum mult mai provocatoare și mai costisitoare. Nu vom scăpa de memorie. Avem nevoie de el pentru că seturile de date devin mai mari. Deci întrebarea este: „Care este calea corectă în continuare?” S-au discutat multe despre stivuire. Dacă ar fi să luăm acea memorie și să o punem direct deasupra procesorului, face două lucruri pentru tine. În primul rând, lățimea de bandă astăzi este limitată de malul țărmului sau de perimetrul cipului. Acolo merg I/O-urile. Dar dacă ar fi să-l stivuiți direct deasupra procesorului, acum puteți folosi întreaga zonă a cipului pentru interconexiuni distribuite și puteți obține mai multă lățime de bandă în memoria însăși și poate alimenta direct în jos. procesorul. Legăturile devin mult mai scurte, iar eficiența energetică probabil crește de ordinul 5X la 6X. În al doilea rând, cantitatea de lățime de bandă pe care o puteți obține din cauza interconectării matricei cu mai multe zone la memorie crește, de asemenea, cu mai mulți factori întregi. Făcând aceste două lucruri împreună, puteți oferi mai multă lățime de bandă și o face mai eficientă din punct de vedere energetic. Industria evoluează la oricare ar fi nevoile și, cu siguranță, acesta este un mod în care vom vedea că sistemele de memorie vor începe să evolueze în viitor pentru a deveni mai eficiente din punct de vedere energetic și pentru a oferi mai multă lățime de bandă.

Fier: Când am început să lucrez la HBM în jurul anului 2016, unii dintre clienții mai avansați au întrebat dacă ar putea fi stivuit. Ei s-au uitat la modul de a stivui DRAM-ul deasupra de ceva timp pentru că există avantaje clare. Din stratul fizic, PHY devine practic neglijabil, ceea ce economisește multă putere și eficiență. Dar acum ai un procesor de mai multe 100 W care are o memorie pe deasupra. Memoria nu poate suporta căldura. Este probabil cea mai slabă verigă din lanțul termic, ceea ce creează o altă provocare. Există beneficii, dar încă trebuie să-și dea seama cum să facă față termicelor. Există mai multe stimulente acum pentru a avansa acest tip de arhitectură, deoarece vă economisește cu adevărat în termeni de performanță și putere și vă va îmbunătăți eficiența de calcul. Dar există unele provocări de design fizic care trebuie abordate. După cum spunea Steve, vedem tot felul de arhitecturi care apar. Sunt total de acord că arhitecturile GPU/CPU nu merg nicăieri, vor fi în continuare dominante. În același timp, fiecare companie de pe planetă încearcă să vină cu o capcană de șoareci mai bună pentru a-și face AI. Vedem SRAM pe cip și combinații de memorie cu lățime de bandă mare. LPDDR și-a ridicat capul destul de mult în aceste zile în ceea ce privește modul de a profita de LPDDR în centrul de date din cauza puterii. Am văzut chiar că GDDR este folosit în unele aplicații de inferență AI, precum și în toate vechile sisteme de memorie. Acum încearcă să stoarce cât mai multe DDR5-uri pe o amprentă. Am văzut fiecare arhitectură la care vă puteți gândi, fie că este vorba de DDR, HBM, GDDR sau altele. Depinde de nucleul procesorului dvs. în ceea ce privește valoarea adăugată generală și apoi cum puteți trece prin arhitectura dvs. particulară. Sistemul de memorie care îl însoțește, astfel încât să vă puteți sculpta procesorul și arhitectura de memorie, în funcție de ceea ce este disponibil.

Si un: O altă problemă este nevolatilitatea. Dacă AI trebuie să se ocupe de intervalul de putere dintre rularea unui AI bazat pe IoT, de exemplu, atunci avem nevoie de multă putere oprită și pornită, iar toate aceste informații pentru antrenamentul AI trebuie să se rotească din nou și din nou. Dacă avem un fel de soluții în care putem stoca acele greutăți în cip, astfel încât să nu trebuie să ne mișcăm întotdeauna înainte și înapoi pentru aceeași greutate, atunci va fi o mulțime de economii de energie, în special pentru IA bazată pe IoT. Va exista o altă soluție pentru a ajuta acele cereri de putere.

Schirrmeister: Ceea ce mi se pare fascinant, din perspectiva NoC, este cazul în care trebuie să optimizați aceste căi de la un procesor care trece printr-un NoC, accesând o interfață de memorie cu un controler care poate trece prin UCIe pentru a trece un chiplet la alt chiplet, care apoi are memorie în aceasta. Nu este că arhitecturile Von Neumann sunt moarte. Dar există atât de multe variații acum, în funcție de volumul de lucru pe care ai dori să o calculezi. Ele trebuie luate în considerare în contextul memoriei, iar memoria este doar un aspect. De unde obțineți datele din localitatea de date, cum sunt aranjate în această DRAM? Lucrăm la toate aceste lucruri, cum ar fi analiza performanței memoriilor și apoi optimizarea arhitecturii sistemului pe aceasta. Stimulează o mulțime de inovații pentru noi arhitecturi, la care nu m-am gândit niciodată când eram la universitate, învățand despre Von Neumann. La celălalt capăt, ai lucruri precum ochiuri. Există acum mult mai multe arhitecturi care trebuie luate în considerare și sunt determinate de lățimea de bandă a memoriei, capacitățile de calcul și așa mai departe, care nu cresc în același ritm.

Alb: Există o tendință care implică calculul dezagregat sau calculul distribuit, ceea ce înseamnă că arhitectul trebuie să aibă mai multe instrumente la dispoziție. Ierarhia memoriei s-a extins. Există semantică inclusă, precum și CXL și diferite memorii hibride, care sunt disponibile pentru flash și în DRAM. O aplicație paralelă la centrul de date este cea auto. Automotive a avut întotdeauna acest senzor de calcul cu ECU-uri (unități de control electronice). Sunt fascinat de modul în care a evoluat spre centrul de date. Având rapid înainte, iar astăzi am distribuit noduri de calcul, numite controlere de domeniu. E același lucru. Încearcă să abordeze faptul că poate puterea nu este o problemă atât de mare, deoarece dimensiunea computerelor nu este la fel de mare, dar latența este cu siguranță o problemă importantă în domeniul auto. ADAS are nevoie de lățime de bandă foarte mare și aveți diferite compromisuri. Și apoi aveți mai mulți senzori mecanici, dar constrângeri similare într-un centru de date. Aveți stocare la rece care nu trebuie să aibă o latență scăzută și apoi aveți alte aplicații cu lățime de bandă mare. Este fascinant să vezi cât de mult au evoluat instrumentele și opțiunile pentru arhitect. Industria a făcut o treabă foarte bună de răspuns și noi toți oferim diverse soluții care alimentează piața.

SE: Cum au evoluat instrumentele de proiectare a memoriei?

Schirrmeister: Când am început cu primele mele cipuri în anii '90, cel mai folosit instrument de sistem a fost Excel. De atunci, am sperat întotdeauna că s-ar putea rupe la un moment dat pentru lucrurile pe care le facem la nivel de sistem, memorie, analiză a lățimii de bandă și așa mai departe. Acest lucru a afectat destul de mult echipele mele. La acea vreme, erau lucruri foarte avansate. Dar, în sensul lui Randy, acum anumite lucruri complexe trebuie simulate la un nivel de fidelitate care anterior nu era posibil fără calcul. Pentru a da un exemplu, asumarea unei anumite latențe pentru un acces DRAM poate duce la decizii proaste de arhitectură și, potențial, la proiectarea incorectă a arhitecturilor de transport de date pe cip. Reversul este, de asemenea, adevărat. Dacă vă asumați întotdeauna cel mai rău caz, atunci veți supraproiecta arhitectura. A avea instrumente care efectuează DRAM și analiza performanței și a avea la dispoziție modelele adecvate pentru controlere permite unui arhitect să simuleze totul, acesta este un mediu fascinant în care să fie. Instrumentul la nivel de sistem s-ar putea de fapt să devină realitate, deoarece unele dintre efectele dinamice pe care nu le mai puteți face în Excel, deoarece trebuie să le simulați - mai ales când introduceți o interfață die-to-die cu caracteristici PHY și apoi legați stratul caracteristici precum toate verificarea dacă totul a fost corect și eventual retrimiterea datelor. Nerespectarea acestor simulări va duce la o arhitectură suboptimă.

Fier: Primul pas în majoritatea evaluărilor pe care le facem este să le oferim bancul de testare a memoriei pentru a începe să se uite la eficiența DRAM. Acesta este un pas uriaș, chiar și făcând lucruri la fel de simple precum rularea instrumentelor locale pentru a face simulare DRAM, dar apoi intră în simulări complete. Vedem mai mulți clienți care solicită acest tip de simulare. Asigurarea că eficiența DRAM-ului este crescută în anii 90 este un prim pas foarte important în orice evaluare.

Woo: O parte din motivul pentru care vedeți creșterea instrumentelor complete de simulare a sistemului este că DRAM-urile au devenit mult mai complicate. Este foarte dificil acum să fii chiar în bară pentru unele dintre aceste sarcini complexe de lucru folosind instrumente simple precum Excel. Dacă te uiți la fișa de date pentru DRAM în anii '90, acele fișe de date erau ca 40 de pagini. Acum sunt sute de pagini. Asta vorbește doar despre complexitatea dispozitivului pentru a obține lățimi de bandă mari. Combinați asta cu faptul că memoria este un astfel de driver în ceea ce privește costul sistemului, precum și lățimea de bandă și latența legate de performanța procesorului. Este, de asemenea, un motor mare în putere, așa că trebuie să simulați la un nivel mult mai detaliat acum. În ceea ce privește fluxul de instrumente, arhitecții de sistem înțeleg că memoria este un factor uriaș. Așadar, instrumentele trebuie să fie mai sofisticate și trebuie să se interfațeze cu alte instrumente foarte bine, astfel încât arhitectul de sistem să aibă cea mai bună imagine globală a ceea ce se întâmplă - în special cu modul în care memoria afectează sistemul.

Si un: Pe măsură ce trecem la era AI, sunt folosite o mulțime de sisteme multi-core, dar nu știm ce date merg unde. De asemenea, merge mai mult paralel cu cipul. Dimensiunea memoriei este mult mai mare. Dacă folosim IA de tip ChatGPT, atunci manipularea datelor pentru modele necesită aproximativ 350 MB de date, ceea ce reprezintă o cantitate imensă de date doar pentru o greutate, iar intrarea/ieșirea reală este mult mai mare. Acea creștere a cantității de date necesare înseamnă că există o mulțime de efecte probabilistice pe care nu le-am văzut până acum. Este un test extrem de provocator să vezi toate erorile legate de această cantitate mare de memorie. Și ECC este folosit peste tot, chiar și în SRAM, care în mod tradițional nu folosea ECC, dar acum este foarte comun pentru cele mai mari sisteme. Testarea pentru toate acestea este foarte dificilă și trebuie susținută de soluții EDA pentru a testa toate acele condiții diferite.

SE: Cu ce provocări se confruntă echipele de ingineri în fiecare zi?

Alb: În orice zi, mă vei găsi în laborator. Îmi suflec mânecile și mi-am murdărit mâinile, înțepăt fire, lipire și altele. Mă gândesc mult la validarea post-siliciu. Am vorbit despre simularea timpurie și instrumentele pe matriță — BiST și lucruri de genul acesta. La sfârșitul zilei, înainte de a livra, vrem să facem o formă de validare a sistemului sau teste la nivel de dispozitiv. Am vorbit despre cum să depășim peretele memoriei. Colocalizăm memoria, HBM, lucruri de genul ăsta. Dacă ne uităm la evoluția tehnologiei de ambalare, am început cu pachete cu plumb. Nu erau foarte bune pentru integritatea semnalului. Decenii mai târziu, am trecut la o integritate optimizată a semnalului, cum ar fi matricele de grilă bile (BGA). Nu am putut accesa asta, ceea ce însemna că nu ai putut-o testa. Așa că am venit cu acest concept numit interpozitor de dispozitiv - un interpozitor BGA - și care ne-a permis să punem în sandwich un dispozitiv special care direcționează semnalele. Apoi l-am putea conecta la echipamentul de testare. Avanză rapid până astăzi, iar acum avem HBM și chipleturi. Cum îmi fac sandwich-ul pe dispozitivul de siliciu? Nu putem și asta e lupta. Este o provocare care mă ține treaz noaptea. Cum efectuăm analiza defecțiunilor pe teren cu un OEM sau un client de sistem, unde nu obțin eficiența de 90%. Există mai multe erori în link, nu se pot inițializa corect și antrenamentul nu funcționează. Este o problemă de integritate a sistemului?

Schirrmeister: Nu ai prefera să faci asta de acasă cu o interfață virtuală decât să mergi la laborator? Nu este răspunsul mai multe analize pe care le construiți în cip? Cu chipleturi, integrăm totul și mai mult. Introducerea fierului de lipit acolo nu este cu adevărat o opțiune, așa că trebuie să existe o modalitate de analiză pe cip. Avem aceeași problemă pentru NoC. Oamenii se uită la NoC, iar tu trimiți datele și apoi dispare. Avem nevoie de analize pe care să le punem acolo, astfel încât oamenii să poată face depanare, iar asta se extinde la nivelul de producție, astfel încât să puteți lucra în sfârșit de acasă și să faceți totul pe baza analizei cipurilor.

Fier: Mai ales cu memoria de bandă mare, nu poți intra fizic acolo. Când acordăm licență pentru PHY, avem și un produs care vine cu asta, astfel încât să puteți pune ochii pe fiecare dintre acești 1,024 de biți. Puteți începe să citiți și să scrieți DRAM din instrument, astfel încât să nu trebuie să intrați fizic acolo. Îmi place ideea de interpozitor. Scoatem niște pini din interpozitor în timpul testării, ceea ce nu puteți face în sistem. Este într-adevăr o provocare să intri în aceste sisteme 3D. Chiar și din punct de vedere al fluxului de instrumente de proiectare, se pare că majoritatea companiilor își fac propriul flux individual pe multe dintre aceste instrumente 2.5D. Începem să punem împreună o modalitate mai standardizată de a construi un sistem 2.5D, de la integritatea semnalului, puterea, întregul flux.

Alb: Pe măsură ce lucrurile merg mai departe, sper că putem menține în continuare același nivel de precizie. Sunt în grupul de conformitate cu factorul de formă UCIe. Mă uit la cum să caracterizez un zar bun cunoscut, un zar de aur. În cele din urmă, acest lucru va dura mult mai mult timp, dar vom găsi un mediu fericit între performanța și acuratețea testării de care avem nevoie și flexibilitatea care este încorporată.

Schirrmeister: Dacă mă uit la chipleturi și adoptarea lor într-un mediu de producție mai deschis, testarea este una dintre provocările mai mari în modul de a le face să funcționeze corect. Dacă sunt o companie mare și controlez toate părțile acesteia, atunci pot constrânge lucrurile în mod corespunzător, astfel încât testarea și așa mai departe să devină fezabile. Dacă vreau să merg la sloganul UCIe că UCI este la doar o literă distanță de PCI și îmi imaginez un viitor în care ansamblul UCIe devine, din perspectiva producției, ca sloturile PCI într-un PC astăzi, atunci aspectele de testare pentru asta sunt într-adevăr provocator. Trebuie să găsim o soluție. E multă treabă de făcut.

Articole pe aceeaşi temă

Viitorul Memoriei (Partea 1 a rotundei de mai sus)

De la încercările de a rezolva problemele termice și energetice până la rolurile CXL și UCIe, viitorul deține o serie de oportunități pentru memorie.

- Distribuție de conținut bazat pe SEO și PR. Amplifică-te astăzi.

- PlatoData.Network Vertical Generative Ai. Împuterniciți-vă. Accesați Aici.

- PlatoAiStream. Web3 Intelligence. Cunoștințe amplificate. Accesați Aici.

- PlatoESG. carbon, CleanTech, Energie, Mediu inconjurator, Solar, Managementul deșeurilor. Accesați Aici.

- PlatoHealth. Biotehnologie și Inteligență pentru studii clinice. Accesați Aici.

- Sursa: https://semiengineering.com/rethinking-memory/

- :are

- :este

- :nu

- :Unde

- $UP

- 1

- 2016

- 3d

- 40

- a

- Despre Noi

- mai sus

- acces

- accesarea

- precizie

- curent

- de fapt

- ADA

- adăuga

- adresa

- Adoptare

- avansat

- Avantaj

- Avantajele

- din nou

- AI

- Instruire AI

- AI / ML

- TOATE

- permis

- permite

- de asemenea

- mereu

- sumă

- an

- analiză

- Google Analytics

- și

- O alta

- răspunde

- Orice

- mai

- oriunde

- aplicație

- aplicatii

- în mod corespunzător

- arhitecți

- arhitectură

- SUNT

- ZONĂ

- în jurul

- amenajat

- Mulțime

- AS

- solicitând

- aspect

- aspecte

- Asamblare

- asuma

- At

- Încercările

- auto

- disponibil

- departe

- înapoi

- Rău

- bilă

- Lățime de bandă

- bar

- bazat

- Pe scurt

- bază

- BE

- deoarece

- deveni

- devine

- fost

- înainte

- fiind

- Beneficiile

- CEL MAI BUN

- Mai bine

- între

- Mare

- mai mare

- Pic

- Pauză

- aduce

- construi

- construit

- afaceri

- dezvoltarea afacerii

- dar

- by

- Cadenţă

- denumit

- a venit

- CAN

- Poate obține

- capacități

- caz

- Centru

- sigur

- cu siguranță

- lanţ

- contesta

- provocări

- provocare

- Caracteristici

- caracteriza

- control

- cip

- Chips

- clasă

- clar

- Cloud

- rece

- Depozitare la rece

- combinaţii

- cum

- venire

- Comun

- Companii

- companie

- complex

- complexitate

- conformitate

- complicat

- Calcula

- Calculatoare

- tehnica de calcul

- concept

- Condiții

- Conectați

- luate în considerare

- constrângeri

- context

- contrast

- Control

- controlor

- Conversație

- Nucleu

- corecta

- A costat

- ar putea

- Cuplu

- Procesor

- creează

- client

- clienţii care

- de date

- Data Center

- seturi de date

- zi

- zilnic

- Zi

- mort

- afacere

- zeci de ani

- Deciziile

- categoric

- cererile

- În funcție

- depinde de

- Amenajări

- proiect

- detaliat

- Dezvoltare

- dispozitiv

- .

- diferit

- dificil

- direct

- Director

- discuţie

- dispoziție

- Distins

- distribuite

- calcul distribuit

- do

- face

- Nu

- face

- domeniu

- dominant

- făcut

- Dont

- jos

- condus

- şofer

- în timpul

- dinamic

- Devreme

- efecte

- eficiență

- eficient

- Electronic

- capăt

- energie

- Inginerie

- Întreg

- Mediu inconjurator

- echipament

- Eră

- Erori

- mai ales

- Eter (ETH)

- evaluare

- evaluări

- Chiar

- în cele din urmă

- Fiecare

- tot

- pretutindeni

- evoluţie

- evolua

- evoluat

- evoluează

- exemplu

- Excel

- extins

- scump

- extinde

- extremă

- extrem

- Ochi

- Față

- fapt

- factor

- Eșec

- fascinant

- FAST

- realizabil

- membru

- fidelitate

- camp

- Figura

- În cele din urmă

- Găsi

- First

- bliț

- Flexibilitate

- Flip

- debit

- urmează

- urmă

- Pentru

- formă

- mai departe

- Înainte

- găsit

- sincer

- din

- Complet

- mai mult

- viitor

- obține

- obtinerea

- Da

- dat

- Caritate

- Go

- Merge

- merge

- De aur

- plecat

- bine

- buna treaba

- am

- Grilă

- grup

- În creştere

- HAD

- Manipularea

- mâini

- fericit

- Avea

- având în

- cap

- ajutor

- ierarhie

- Înalt

- deține

- Acasă

- speranţă

- Cum

- Cum Pentru a

- HTML

- HTTPS

- mare

- sute

- Hibrid

- i

- idee

- if

- imagina

- afectate

- impact

- important

- îmbunătăţi

- in

- Stimulent

- inclus

- în mod incorect

- Crește

- tot mai mult

- individ

- industrie

- informații

- Inovaţie

- în interiorul

- integra

- integritate

- interconexiuni

- interfaţă

- în

- implicând

- problema

- probleme de

- IT

- ESTE

- în sine

- Loc de munca

- doar

- Cunoaște

- cunoscut

- de laborator

- mare

- mai mare

- cea mai mare

- Latență

- mai tarziu

- strat

- conduce

- învăţare

- scrisoare

- Nivel

- Licență

- ca

- Limitat

- LINK

- Link-uri

- local

- Uite

- cautati

- Lot

- loturi

- Jos

- menține

- face

- Efectuarea

- administrare

- manager

- de fabricaţie

- multe

- Piață

- max-width

- poate

- me

- mijloace

- a însemnat

- mecanic

- mediu

- Amintiri

- Memorie

- ar putea

- Modele

- mai mult

- cele mai multe

- muta

- mutat

- mişcare

- în mişcare

- mult

- my

- Nevoie

- nevoilor

- nu

- Nou

- noapte

- noduri

- acum

- număr

- of

- de pe

- Vechi

- on

- ONE

- afară

- deschide

- Oportunităţi

- Optimizați

- optimizate

- optimizarea

- Opțiune

- Opţiuni

- or

- comandă

- Altele

- Altele

- afară

- global

- Învinge

- propriu

- ofertele

- ambalaje

- pagini

- Paralel

- parte

- special

- trece

- cale

- căi

- PC

- oameni

- efectua

- performanță

- perspectivă

- fizic

- Fizic

- pini

- planetă

- Plato

- Informații despre date Platon

- PlatoData

- Punct

- posibil

- potenţial

- putere

- preşedinte

- în prealabil

- probabil

- Problemă

- procesor

- procesoare

- Produs

- management de produs

- producere

- Program

- adecvat

- cum se cuvine

- furniza

- pune

- întrebare

- cu totul

- ridicare

- rată

- mai degraba

- Citind

- într-adevăr

- legate de

- se bazează

- necesar

- Necesită

- rezolvă

- răspunde

- rezultat

- Scăpa

- dreapta

- Ridica

- rolurile

- sul

- Alerga

- funcţionare

- acelaşi

- Economisiți

- Economie

- spunând

- Scară

- Al doilea

- vedea

- vedere

- pare

- văzut

- semantică

- semiconductor

- trimite

- senzor

- senzori

- servere

- câteva

- coli

- schimbare

- navă

- parte

- fete

- Siemens

- Semnal

- semnalele

- Siliciu

- asemănător

- simplu

- simulare

- simulări

- întrucât

- singur

- Mărimea

- sloturi

- So

- Software

- soluţie

- soluţii

- unele

- sofisticat

- vorbeşte

- special

- uzat

- Stoarce

- stivui

- stivuite

- stivuire

- standardizate

- punct de vedere

- Începe

- început

- Pornire

- Pas

- Steve

- steven

- Încă

- depozitare

- stoca

- Lupta

- astfel de

- Suportat

- sigur

- sistem

- sisteme

- tabel

- Lua

- Vorbi

- echipe

- tehnolog

- Tehnologia

- termeni

- test

- Testarea

- teste

- decât

- acea

- Viitorul

- lor

- Lor

- apoi

- Acolo.

- termic

- Acestea

- ei

- lucru

- lucruri

- crede

- Al treilea

- acest

- aceste

- gândit

- Prin

- timp

- la

- astăzi

- împreună

- instrument

- Unelte

- top

- INTRU TOTUL

- compromisuri

- tradiţional

- tradiţional

- Pregătire

- de transport

- tendință

- adevărat

- încercat

- Două

- două treimi

- tip

- înţelege

- de unităţi

- universitate

- us

- utilizare

- utilizat

- folosind

- validare

- valoare

- variații

- diverse

- foarte

- viciu

- Vicepreședinte

- Vizualizare

- Virtual

- de

- mers

- Perete

- vrea

- a fost

- Cale..

- we

- greutate

- BINE

- au fost

- Ce

- indiferent de

- cand

- dacă

- care

- în timp ce

- alb

- întreg

- de ce

- voi

- cu

- fără

- peți

- Apartamente

- lucru de acasă

- de lucru

- Mini rulouri de absorbție

- scris

- tu

- Ta

- zephyrnet