A S2C é líder global em prototipagem de FPGA há quase duas décadas, e suas plataformas de prototipagem de FPGA acompanham de perto a disponibilidade dos FPGAs mais recentes – incluindo os FPGAs mais recentes da Xilinx e da Intel. E eles estão definitivamente cumprindo a promessa de aprimorar suas soluções de prototipagem para prototipagem de design em hiperescala – aumento de escala capacidades e capacidades da plataforma de prototipagem para suportar projetos de vários bilhões de portas.

Olhando para o início do 4T 2020, a S2C anunciou suporte para os então novos FPGAs Xilinx VU19P UltraScale+, oferecendo plataformas de prototipagem de FPGA simples, duplas e quádruplas. Então, em dezembro de 2020, a S2C fez o anúncio de sua família de plataformas de prototipagem Prodigy Logic Matrix de alta densidade com 8 FPGAs por Logic Matrix, 8 Logic Matrix por rack de servidor único (64 FPGAs) e a conexão de vários racks de servidores juntos. As primeiras iterações do Logic Matrix foram entregues com FPGAs Xilinx VU440 (apelidados de LX1) para os primeiros clientes que não podiam esperar pela versão VU19P (apelidada de LX2).

Agora, a S2C está intensificando seu jogo Logic Matrix com o LX2, que aumenta a capacidade útil da porta de prototipagem em 60% em relação à versão VU440! Mais portas utilizáveis por FPGA significam menos FPGAs, menos interconexões de FPGA e maior desempenho para o mesmo projeto de protótipo. Com uma capacidade estimada de portões de 392 milhões de portões por LX2, um rack de servidor padrão totalmente preenchido com 8 LX2 permite uma capacidade estimada de prototipagem de mais de 3 bilhões de portas ASIC!

Figura 1: Matriz Lógica Prodigy LX2

| Família Prodigy Logic Matrix | ||

| LX1 | LX2 | |

| FPGA | XCVU440 | XCVU19P |

| Portas ASIC estimadas (M) | 240 | 392 |

| Número de FPGAs | 8 | 8 |

| Células Lógicas do Sistema (K) | 44,328 | 71,504 |

| Memória FPGA (Mb) | 709 | 1,327.2 |

| Fatias DSP | 23,040 | 30,720 |

| E/S de usuário externo | 9,216 | 10,368 |

| Transceptores SerDes | 384 GTH | 640 GTY |

| Conectores Prodígio | 64 | 72 |

| Conectores PGT | 8 | 0 |

| Conectores de Transceptor | 80 MSAS cada um com 4 GTH + 8 IOs | 160 MCIO cada um com 4 GTY + 8 IOs |

| Qual o desempenho do SerDes? | 16 Gbps | 28 Gbps |

Figura 2: Família de Matriz Lógica

A interconexão flexível e de alta velocidade é fundamental para a prototipagem FPGA de alta densidade, e o Logic Matrix oferece suporte a uma estratégia de interconexão hierárquica de três níveis: Ponte Curta para interconexão entre FPGAs vizinhos; SysLink para interconexão de cabos FPGA de alta largura de banda e TransLink para interconexão FPGA SerDes de longa distância através de cabos MCIO. Para simplificar a interconexão do FPGA e maximizar o valor do TransLink, o fluxo de particionamento do S2C suporta o recém-introduzido High-Speed Transceiver Pin Multiplexing (HSTPM) da Xilinx, simplificando a transferência de sinal com precisão de ciclo, multiplexação de pinos e conectividade SerDes FPGA de baixa latência.

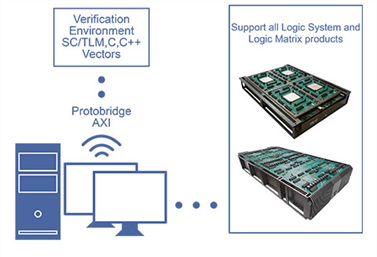

Para minimizar o tempo de prototipagem e maximizar a produtividade da prototipagem, as outras ferramentas de produtividade de prototipagem da S2C são projetadas com o Logic Matrix em mente, incluindo Tempo de execução do Player Pro software – e ferramentas complementares de prototipagem S2C, incluindo ProtoBridge, MDM Proe S2C IP pronto para protótipo.

Tempo de execução do Player Pro software está incluído com LX2, fornecendo recursos convenientes, como gerenciamento avançado de relógio, autoteste integrado, detecção automática de placa, programação de tensão de E/S, downloads múltiplos de FPGA e monitoramento e gerenciamento remoto do sistema. Também está incluído o AXEVision, uma ferramenta de depuração AXI-over-Ethernet integrada para simplificar a depuração remota de projetos relacionados ao AXI.

ProtoBridge suporta transferências de dados de alto rendimento (até 1 GB/s) entre o PC host e o LX2 – permitindo a transferência de grandes quantidades de transações modeladas por software, fluxos de vídeo ou outros estímulos de teste para validação do sistema.

Figura 3: ProtoBridge

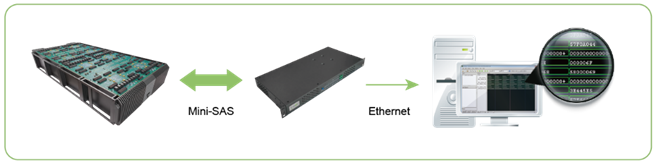

MDM Pro apresenta depuração profunda de rastreamento com disparos cruzados para até oito FPGAs, visualização de rastreamento de sinal multi-FPGA em uma única janela de visualização, 64 GB de armazenamento externo de forma de onda de rastreamento, taxas de amostragem de rastreamento de até 125 MHz e suporta linguagens de máquina de estado de disparo para capturas de rastreamento complexas requisitos.

Figura 4: MDM Pro

S2C também oferece uma rica biblioteca de IP pronto para protótipo para o LX2 – Placas filhas plug-and-play – que aceleram a criação do ambiente de prototipagem em torno do protótipo FPGA.

Figura 5: Placas filhas IP prontas para protótipo

Matriz Lógica Prodígio LX2 está disponível agora. Para obter mais informações, entre em contato com seu representante de vendas local da S2C ou visite www.s2ceda.com.

Compartilhe esta postagem via: Fonte: https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/- 2020

- Adicionar

- anunciou

- Anúncio

- por aí

- ASIC

- disponibilidade

- bilhão

- borda

- cabos

- Capacidade

- da conexão

- Conectividade

- Clientes

- dados,

- entregando

- Design

- Detecção

- distância

- Cedo

- Meio Ambiente

- família

- Funcionalidades

- Figo

- Primeiro nome

- fluxo

- FPGA

- jogo

- Portões

- Global

- HTTPS

- Incluindo

- INFORMAÇÕES

- Intel

- IP

- Chave

- Idiomas

- grande

- mais recente

- Biblioteca

- local

- de grupos

- Matriz

- milhão

- monitoração

- oferecendo treinamento para distância

- Oferece

- Outros

- PC

- atuação

- plataforma

- Plataformas

- Pro

- produtividade

- Ferramentas de Produtividade

- Programação

- prototipagem

- Preços

- Requisitos

- vendas

- aumento de escala

- Software

- Soluções

- Estado

- estímulo

- armazenamento

- Estratégia

- córregos

- ajuda

- suportes

- .

- teste

- Transações

- valor

- Vídeo

- esperar

- QUEM